# الأكاديمية العربية الدولية

الأكاديمية العربية الدولية

Arab International Academy

---

## الأكاديمية العربية الدولية المقررات الجامعية

---

# الدوائر المنطقية

نظري ... عملي

(مع شرح لما يزيد على ١٥٠ شريحة إلكترونية)

أ.د. محمد ابراهيم العدوى

قسم الإلكترونيات والاتصالات والحسابات - كلية الهندسة بحلوان - جامعة حلوان

## الإهداء

إلى كل من يحترم لغته ويعتز بها !!!

## رجاء من كل قراء هذا الكتاب

الكتاب متاح لجميع القراء دون أى تكلفة وللاستفادة منه على أى وجه. فرجاء

إذا رأيت عزيزى القارئ أنك قد استفدت منه فلا أطلب منك سوى الدعاء

لمؤلفه إن كنت غير قادر ماديا، أما القارئ القادر ماديا فأطلب منه التبرع بما

يستطيع لأى جهة خيرية يريده، ول يكن على سبيل المثال مستشفى سلطان

الأطفال ٥٧٣٥٧ بالقاهرة، أو مستشفى الكبد بالمنصورة، أو مستشفى القلب

(مجدى يعقوب) بأسوان، أو هيئة مصر الخير، أو صندوق تحيا مصر، مع نية

ثواب التبرع للمتبرع وللمؤلف.

## المؤلف

أ.د. محمد ابراهيم العدوى

98eladawy@gmail.com

## عرض الكتاب

**لا شك** أننا نعيش الآن في عالم من الرقمنيات ابتداء من لعب الأطفال البسيطة وانتهاء بنظم التراسل مع الأقمار الصناعية والتليفونات المحمولة، فكلها تعامل من خلال الإشارات الرقمية. من السهل جداً أن تعامل مع مثل هذه الإشارات إذا تعلمنا أساسيات علم الإلكترونيات الرقمية بأسلوب سهل وبسيط على القارئ العربي.

لقد أصبح التعامل مع الإلكترونيات هذه الأيام من الأمور السهلة والبسيطة حتى على الماء غير المتخصص. يرجع ذلك إلى أن التعامل مع الإلكترونيات الآن أصبح على مستوى الأنظمة. فأنت الآن تستطيع شراء شريحة إلكترونية بثمن قليلة تحتوي مكثف إشارة كامل وكل ما عليك هو قراءة دليل هذه الشريحة لتعرف أين تضع إشارة الدخل، ومن أين ستأخذ الخرج، وأين ستضع مصدر القدرة للشريحة. وهكذا ستجد هناك في سوق الإلكترونيات شريحة أو أكثر تستطيع بها بناء أي مشروع يخطر ببالك مهما كانت درجة تعقيده.

نحن هنا نقدم هذا الكتاب كخطوة أولى لتحقيق هذا الهدف، هدف أن يستطيع أي قارئ سواء كان من طلاب المراحل الأولى من كليات الهندسة أو من الماء بناء أي دائرة يفكر فيها وذلك بأسلوب سهل وبسيط وبعيد عن التعقيد. من أجل ذلك رأينا أن نعرض الخلفية النظرية لموضوعات الإلكترونيات الرقمية المهمة، ثم عرضنا بالشرح المبسط

الكثير من الشرائح الموجودة في السوق والتي تؤدي هذا الغرض من حيث الرسم الطرفي والوظيفي لكل شريحة. ربما تحتوى المكتبة العربية على بعض الكتب في هذا المجال والتي أغلبها من الكتب المترجمة، ولكن معظم هذه الكتب تختتم فقط بالناحية النظرية ونادرًا ما تتعرض بالشرح لبعض الشرائح الذي يعني القارئ عن الجرى وراء جمع كتالوجات هذه الشرائح، وهذا ما حاولنا تحقيقه هنا من خلال الشرح الكاف لما يزيد على ١٥٠ شريحة إلكترونية في الموضوعات المختلفة. فكما أن هذا الكتاب صمم ليكون كتاباً دراسياً للسنوات الأولى من كليات الهندسة، ومناسبًا أيضًا لهواة الإلكترونيات، إلا أنه يعتبر أيضًا كتالوجاً أو مرجعًا في الكثير من شرائح الإلكترونيات الرقمية. ولقد تم عمل جدول يضم أرقام هذه الشرائح ووظيفتها كل منها وموقع كل منها في الكتاب لسهولة الوصول إلى أي شريحة بسرعة.

**الفصل الأول** من الكتاب يعرض مقدمة عامة عن الإلكترونيات الرقمية تبدأ بالتعرف على الأنواع المختلفة للمقاومات والمكثفات وكيفية قراءتها وتحديد القدرة لها. بعد ذلك يعرض الفصل للأنواع المختلفة للشرائح الإلكترونية وكيفية التعامل مع أطرافها. بعد ذلك يقدم الفصل فكرة سريعة عن أجهزة القياس المستخدمة في قياس وإظهار الإشارات الرقمية.

**الفصل الثاني** يقدم أنظمة العد المختلفة وكيفية التحويل من نظام لآخر وكيفية إجراء العمليات الحسابية في هذه الأنظمة وبالذات النظام الثنائي حيث أنه هو النظام المستخدم في الحاسوبات وال الإلكترونيات الرقمية على وجه العموم.

**الفصل الثالث** يقدم كل أنواع البوابات المنطقية التي تعتبر أدوات الإلكترونيات الرقمية، وقدم الفصل أيضًا للكثير من الشرائح المتاحة في السوق والتي تؤدي وظيفة كل بوابة من هذه البوابات.

**الفصل الرابع** يقدم الجبر البوليني، هذا الجبر الذي يعتبر حساب الدوائر المنطقية. يقدم الفصل أيضًا للطرق المختلفة لتبسيط التعبيرات المنطقية، وكيفية بناء هذه التعبيرات في صورة دائرة إلكترونية من البوابات المختلفة وبأكثر من طريقة.

**الفصل الخامس** يقدم العديد من الدوائر المنطقية الشهيرة ومنها المشفرات Encoders و محللات الشفرة Decoders و منتقل البيانات Multiplexer وموزع البيانات Demultiplexer ويقدم الفصل أيضاً للكثير من الشرائح المستخدمة في ذلك.

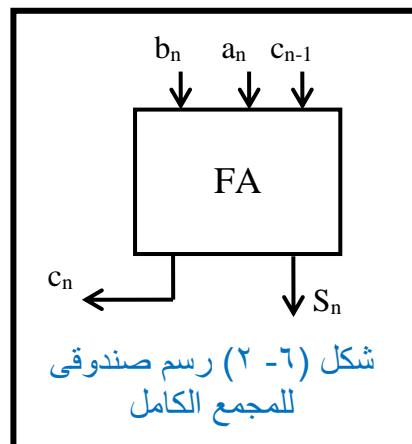

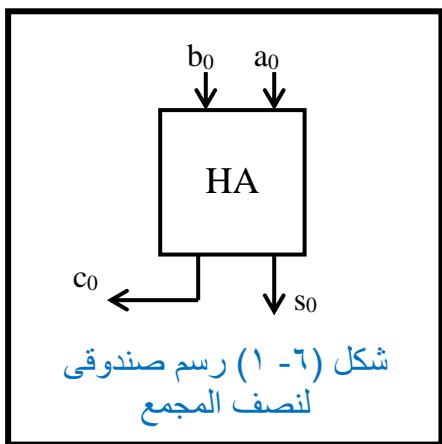

**الفصل السادس** يقدم دوائر الحساب ومن أهمها الجمع بأنواعه وكيفية استخدامه كطراح ثم دوائر المقارنة والشريحة المستخدمة في ذلك.

**الفصل السابع** يقدم شرحاً وافياً للمساكنات بأنواعها والفرق بين هذه الأنواع، ثم يختتم الفصل بالشرح الوافى للكثير من الشريحة الإلكترونية.

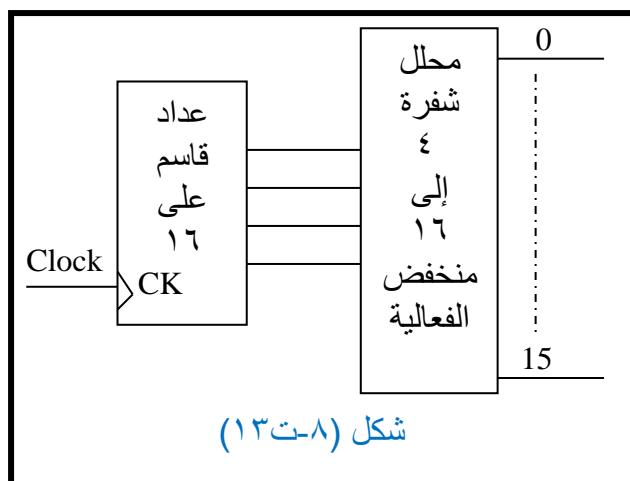

**الفصل الثامن** يقدم شرحاً مفصلاً للعدادات الرقمية كأحد تطبيقات القالبات الأساسية وأحد الدوائر الرقمية المستخدمة بكثرة في الكثير من التطبيقات، ويختتم الفصل أيضاً بالعديد من شرائح العدادات ذات الخواص والمواصفات المختلفة.

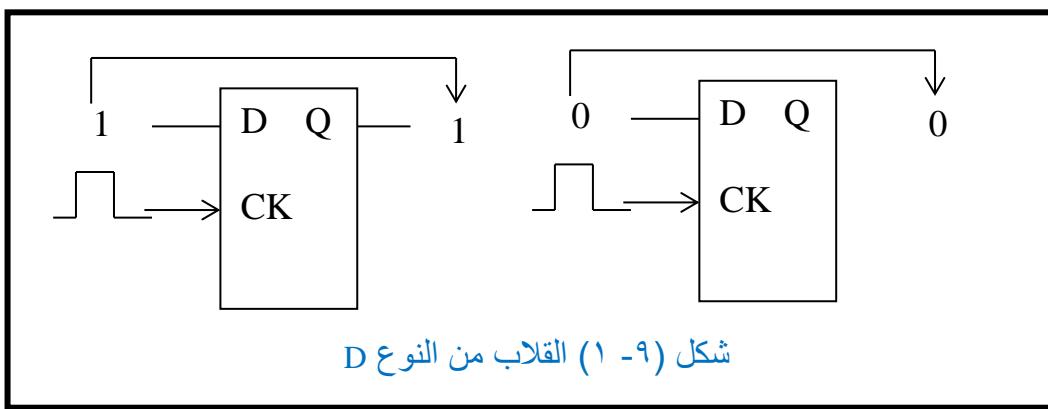

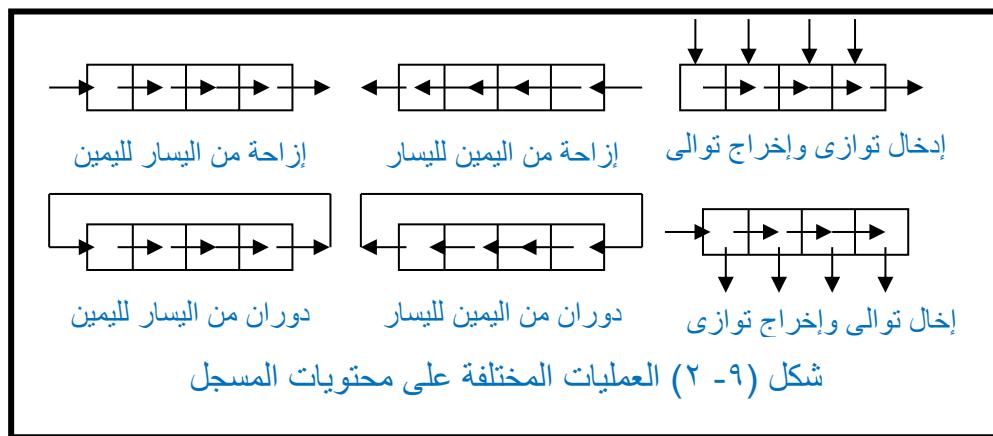

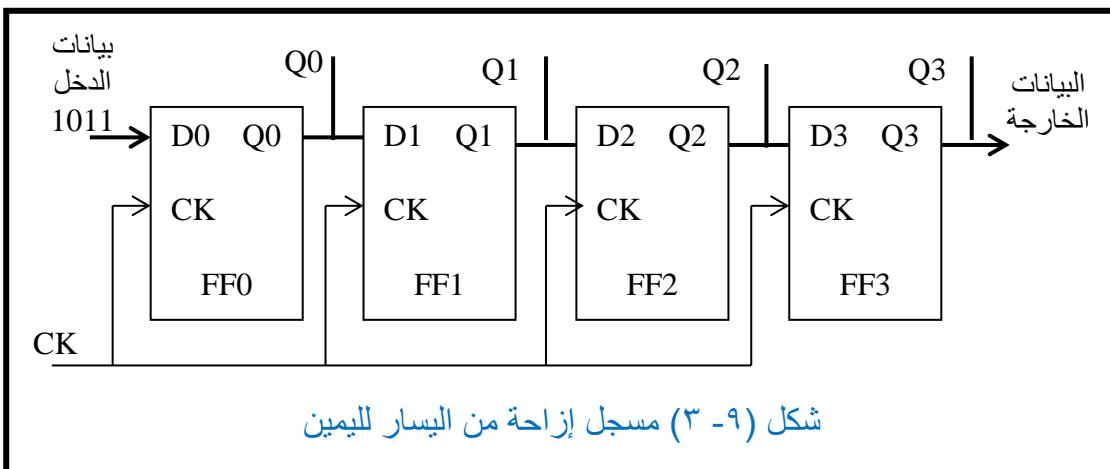

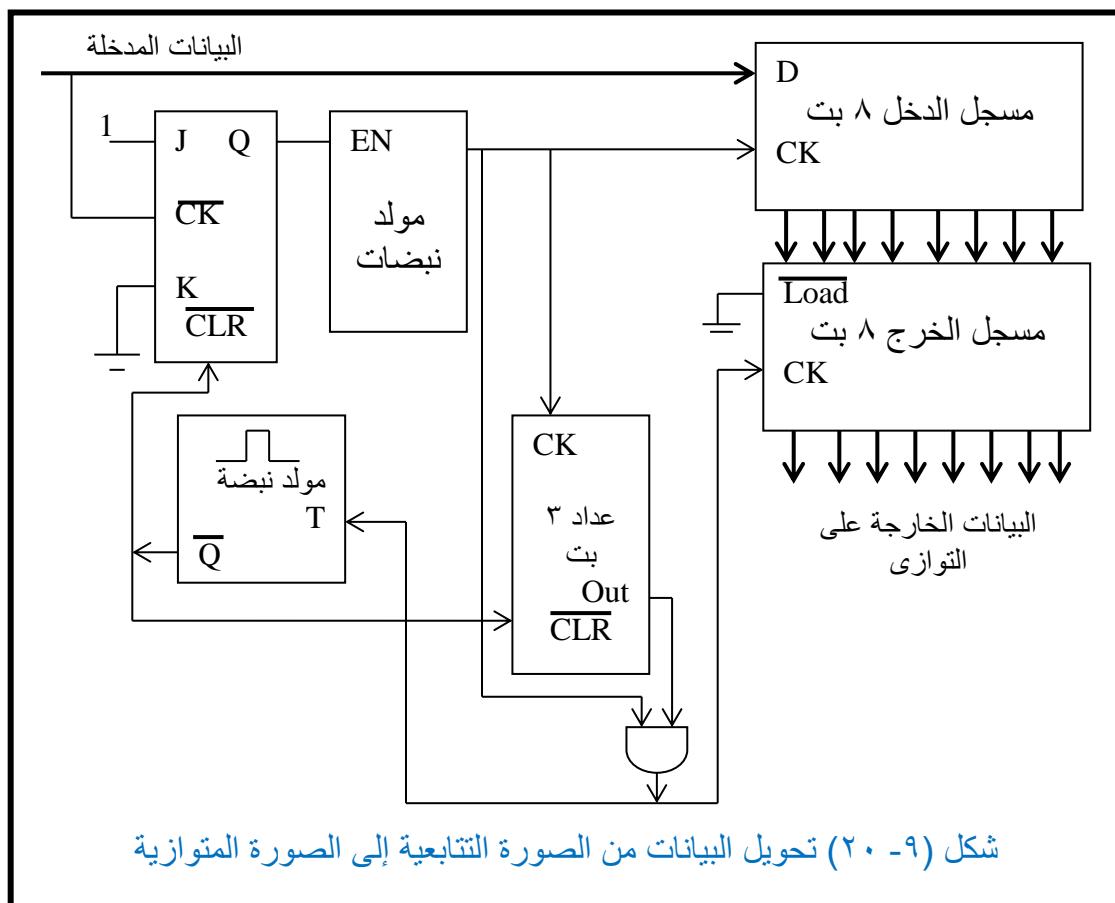

**الفصل التاسع** يقدم مسجلات الإزاحة كأحد التطبيقات كثيرة الاستخدام في الدوائر والمشاريع الإلكترونية، ويختتم الفصل أيضاً بشرح العديد من الشريحة المستخدمة لهذا الغرض.

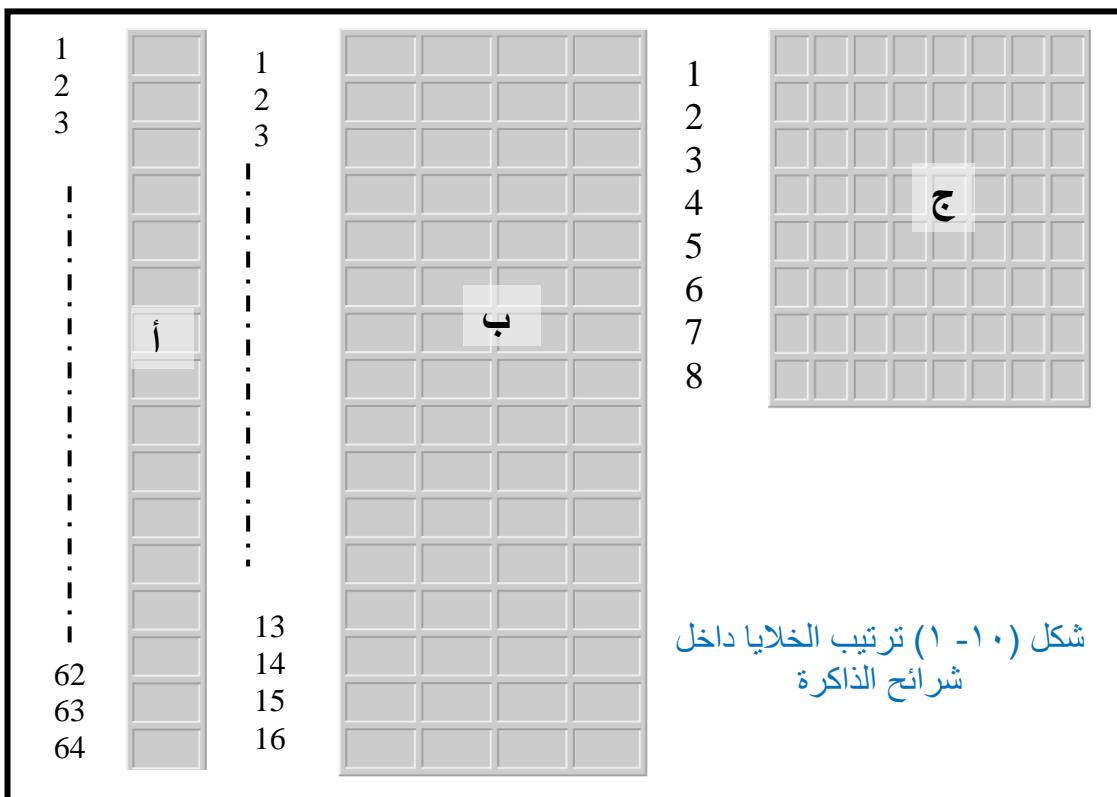

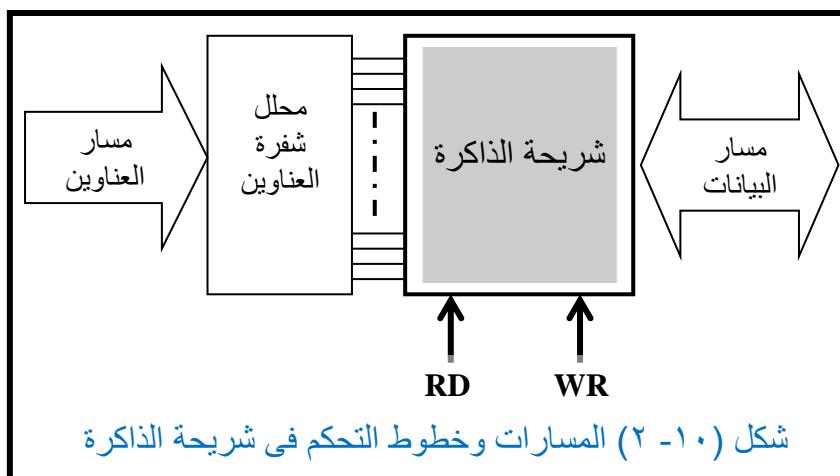

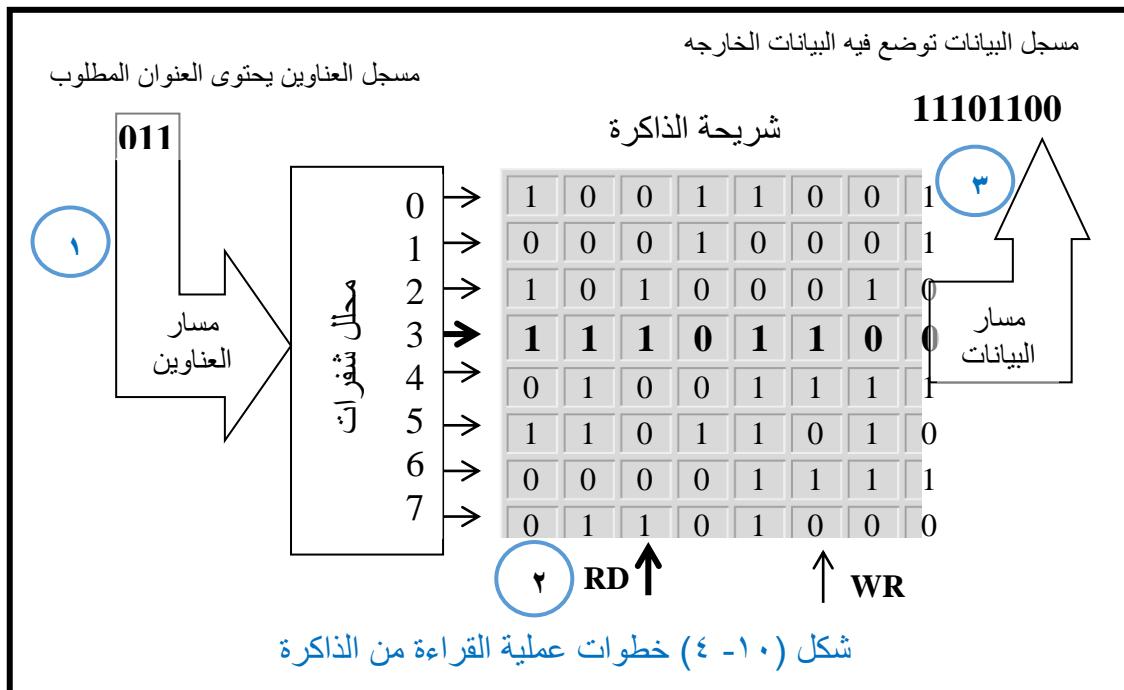

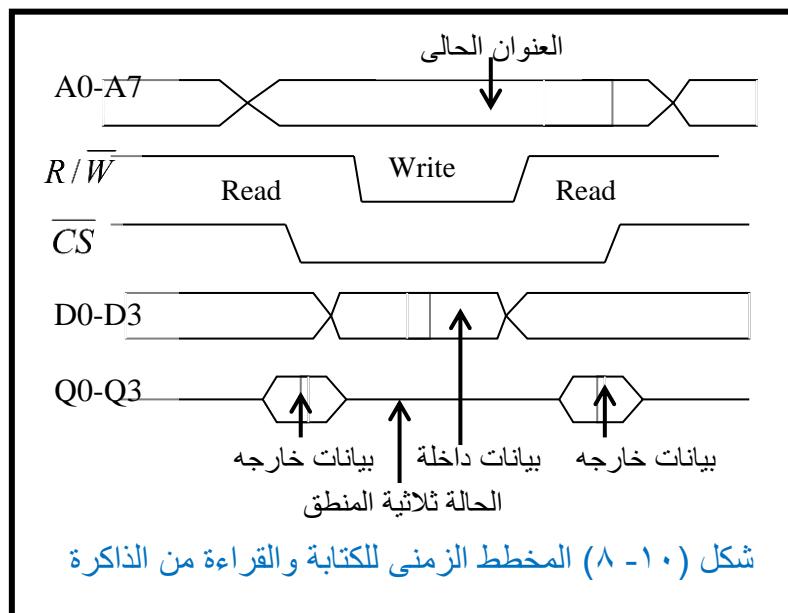

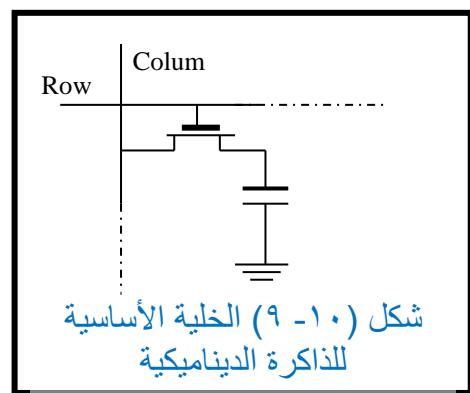

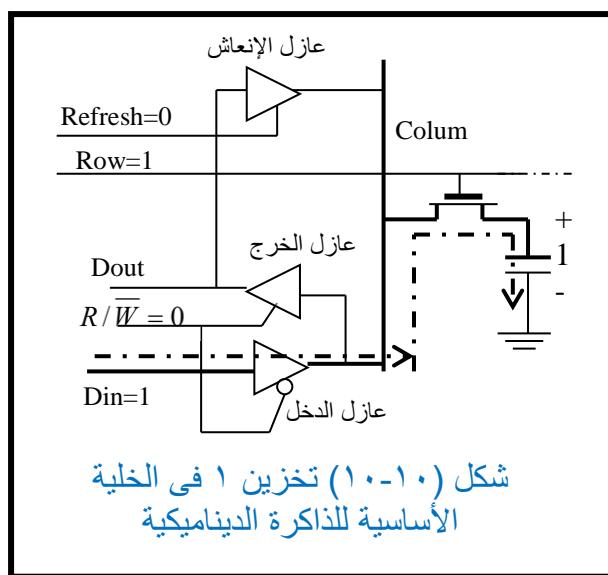

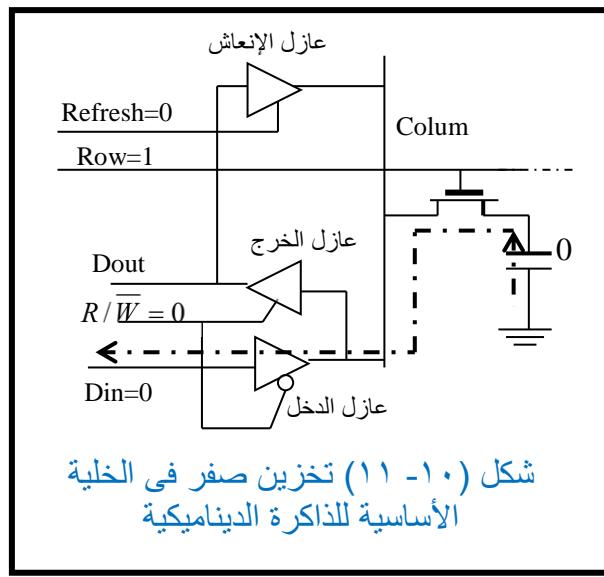

**الفصل العاشر** يقدم شرحاً لأنواع المختلفة من الذاكرة سواء ذاكرة القراءة والكتابة RAM أو ذاكرة القراءة فقط ROM. ثم يقدم الفصل أيضاً شرحاً للعديد من شرائح الذاكرة شائعة الاستخدام.

**الفصل الحادى عشر** يعرض لكيفية بناء دوائر التوقيت المختلفة باستخدام شرائح متاحة في السوق رخيصة الثمن جداً. كلنا نعلم مدى أهمية دوائر التوقيت في الكثير من التطبيقات والمشاريع المختلفة. يقدم الفصل أيضاً شرحاً وافياً للكثير من شرائح التوقيت والاستخدامات المختلفة والخواص المميزة لكل شريحة.

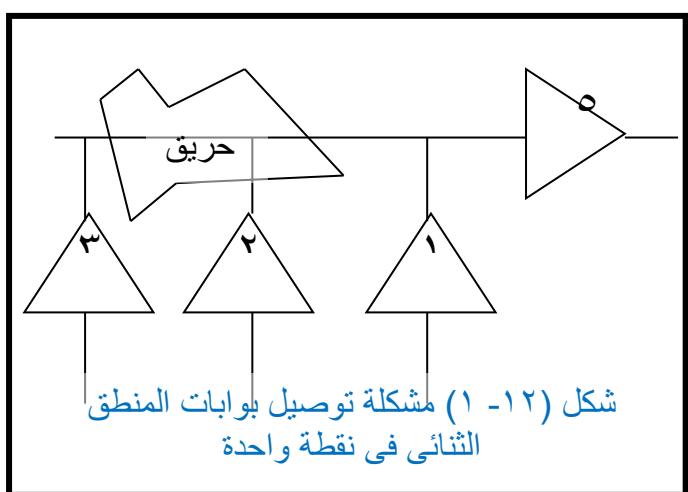

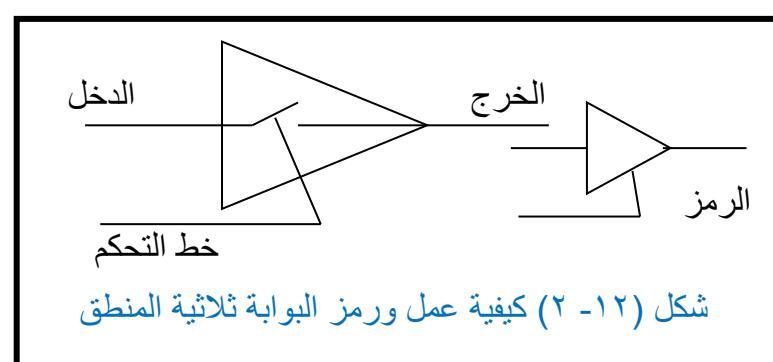

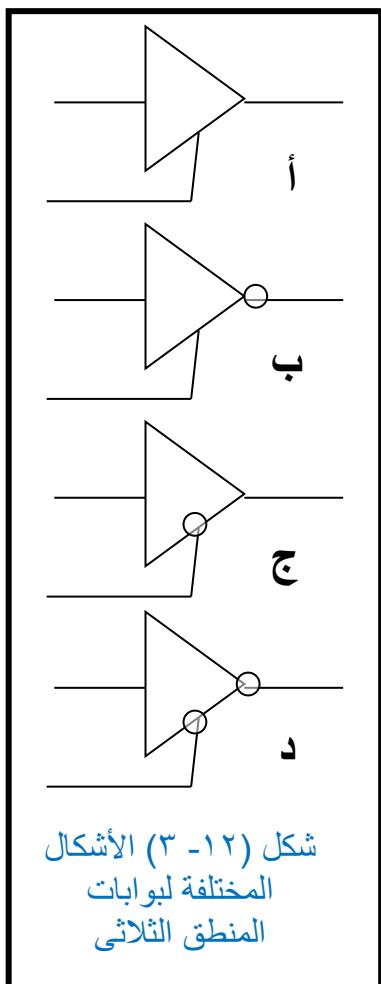

**الفصل الثاني عشر** يقدم عرضاً لنوع ممهم من البوابات المنطقية وهي البوابات ثلاثة المنطق التي تستخدم بكثرة بالذات عند التعامل مع المعالجات والحسابات.

بعد ذلك تم وضع قاموس لكل المصطلحات والكلمات الأجنبية التي تم استخدامها في هذا الكتاب مع إعطاء نبذة مختصرة عن معنى هذه الكلمة واستخداماتها إذا تطلب الأمر. وقد حاولنا في أثناء الشرح وضع الكلمة أو المصطلح الإنجليزي كما هو باللغة الإنجليزية وبالذات عند أول ذكر له حتى لا نحرم المستخدم من معرفة ذلك. في بعض المواضيع القليلة في الكتاب تم استخدام النطق الأجنبي لبعض الكلمات باللغة العربية ولكن بعد شرح المعنى العربي للكلمة. فمثلاً بوابة الضرب المنطقى AND تم كتابتها بوابة آند لسرعة التعامل وكان ذلك فقط مع البوابات المنطقية وذلك لشيوخ النطق الأجنبي وكثرة استخدامه.

يعتقد البعض أن الكتابة العلمية أو التدريس باللغة العربية هو مهارة للغات الأجنبية التي تحتاجها مواكبة العلم والتكنولوجيا، ونحن نؤكد هنا على أننا لسنا ضد تعلم اللغات الأجنبية ولكننا ضد فكرة أن مواكبة العلم والتكنولوجيا لا تكون باللغة العربية. هل نحكم على رجل الشارع أن يتعلم اللغات الأجنبية حتى يمكنه النهوض بنفسه والتقدم مع العلم والتكنولوجيا، أم نحضر له العلم والتكنولوجيا على طبق من فضة بلغته فيستطيع استيعابها وهضمها، وعند ذلك فقط سيبدع ويفيظ كل طاقاته التي كانت مخبأة وراء حاجز العجز اللغوى. إن معظم الشعب المصرى لديه ثقافة طيبة ممتازة يستطيع بها أن يشخص المرض ويصف العلاج ونحن نعتقد أن ذلك مرجعه إلى المطبوعات العربية في ذلك وكثرة الأدوية التي يستخدمها

وكلها لها نشرات باللغة العربية، حتى أن البعض افتتح عدم كتابة نشرات الأدوية باللغة العربية حتى لا يتمادى البعض في وصف العلاج بنفسه ودون الرجوع للطبيب. لقد تأخرنا كثيراً نحن القائمين على تدريس المادة العلمية في استخدام اللغة العربية في كتابة مذكراتنا أو مؤلفاتنا وحتى في التدريس في قاعات المحاضرات حتى فرضت المصطلحات الأجنبية نفسها علينا وأصبحنا لا نستطيع الفكاك منها بالرغم من وجود المرادف العربي السهل لها. بالله ماذا يفضل البعض استخدام كلمة *encoder* ويتردد في أن ينطق بكلمة مشفر، أو أن يقول *multiplexer* وبصيغة الخزى والعار إذا قال منتقى بيانات، والأمثلة لا حصر لها في كل الحالات. إن كل تقارير متخصصي التربية العالميين توصى بأن يكون التدريس باللغة الأم لأى دارس وحدروا من خطورة الإفراط في تعلم اللغات الأجنبية. إن هذا ما اتبعه اليابانيون وكل دول شرق آسيا التي وصلت إلى ما وصلت إليه الآن من تقدم علمي واقتصادي. التعليم في اليابان باللغة اليابانية في كل مراحل التدريس، ولا تدرس اللغات الأجنبية إلا كمقترنات اختيارية يختارها من يريد تعلم هذه اللغة وأنا أعتقد أن هذا هو سر وصولهم إلى ما وصلوا إليه الآن. لقد جربنا كثيراً التمسك والإفراط في أن الطريق إلى التقدم هو من خلال اللغات الأجنبية، فهل آن الأوان في أن نخرب إعطاء اللغة العربية الفرصة الحقيقة لتكون لغة التدريس الأساسية في الجامعات، وتوجه العناية للتأليف بها والترجمة إليها.

وأخيراً أتقدم بالشكر إلى كل أفراد أسرتي الذين أتاحوا لي الفرصة والوقت في تجهيز وإعداد هذا الكتاب كخطوة وتجربة ثانية أرجو أن تتكرر للكتابة باللغة العربية التي لا عز لنا إلا بعزها ورفعتها. وأرجو أن أتلقى أي مقتراحات في هذا الشأن وبالتالي أكيد ستكون قوة دافعة.

#### المؤلف

أ.د. محمد ابراهيم العدوى

كلية الهندسة بحلوان جامعة حلوان

قسم الاتصالات والإلكترونيات والمحاسيب

[98eladawy@gmail.com](mailto:98eladawy@gmail.com)

## جدول الشرائح الموجودة في هذا الكتاب

| الصفحة | الوظيفة                                          | رقم الشرحية |

|--------|--------------------------------------------------|-------------|

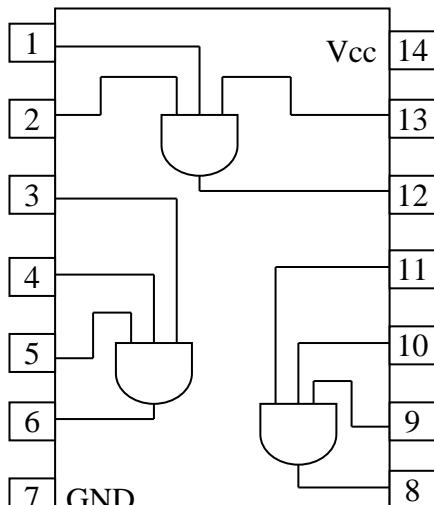

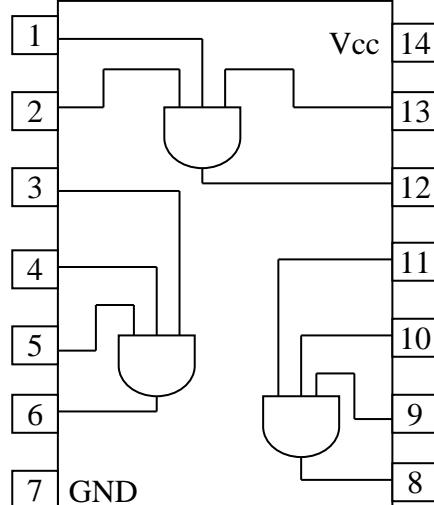

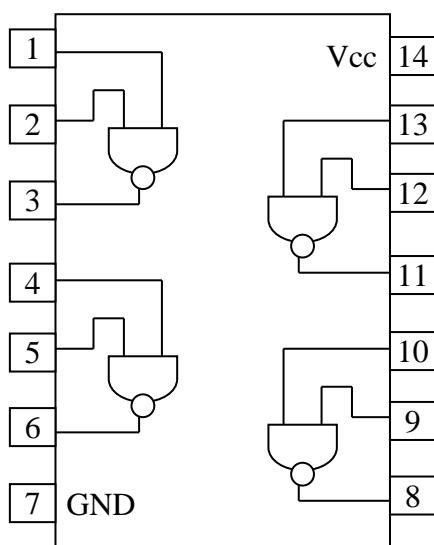

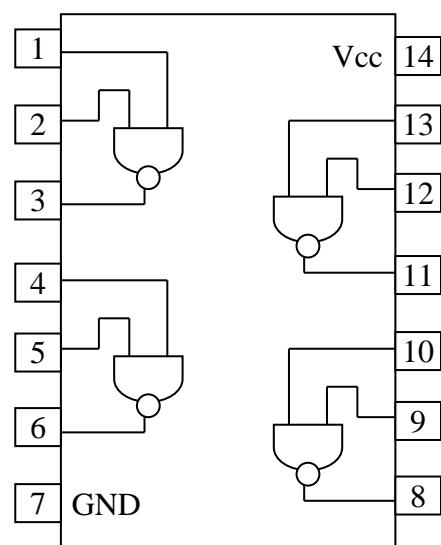

| ٤٨     | ٤ بوابات ناند NAND ثنائية المداخل                | 7400        |

| ٤٨     | ٤ بوابات ناند NAND ثنائية المداخل مفتوحة المجمع  | 7401        |

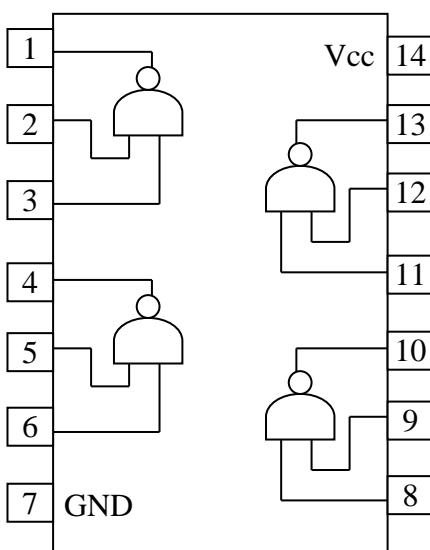

| ٥١     | ٤ بوابات نور NOR ثنائية المداخل                  | 7402        |

| ٤٨     | ٤ بوابات ناند NAND ثنائية المداخل مفتوح المجمع   | 7403        |

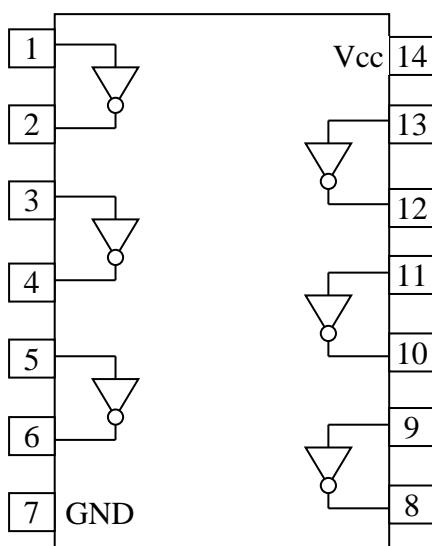

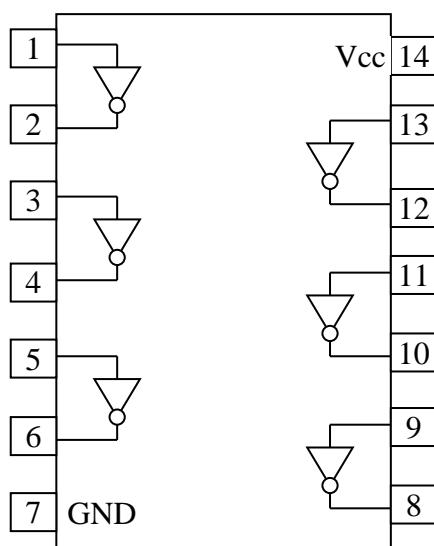

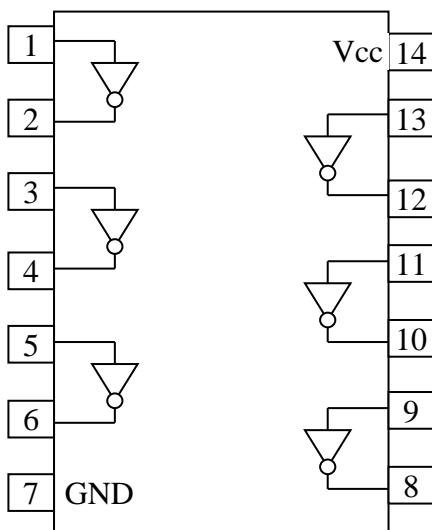

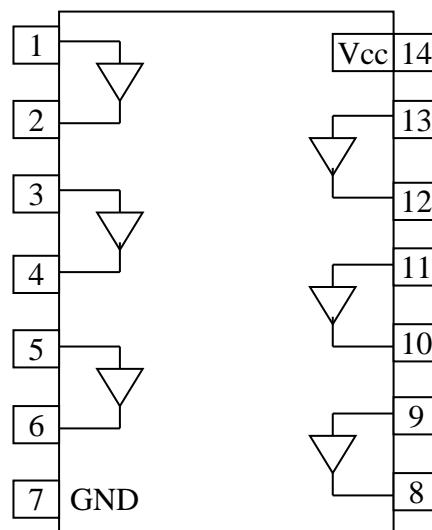

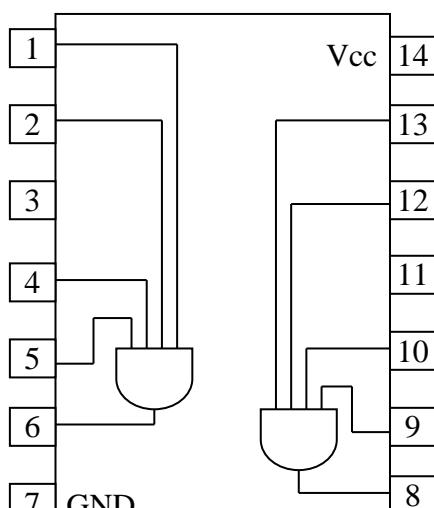

| ٤٥     | ٦ عواكس Inverter                                 | 7404        |

| ٤٥     | ٦ عواكس مفتوحة المجمع                            | 7405        |

| ٤٦     | ٦ عواكس مفتوح المجمع ، دافع تيار Current driver  | 7406        |

| ٤٦     | ٦ عواكس مفتوح المجمع                             | 7407        |

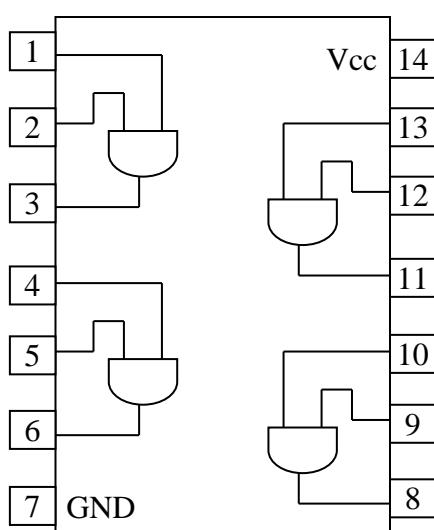

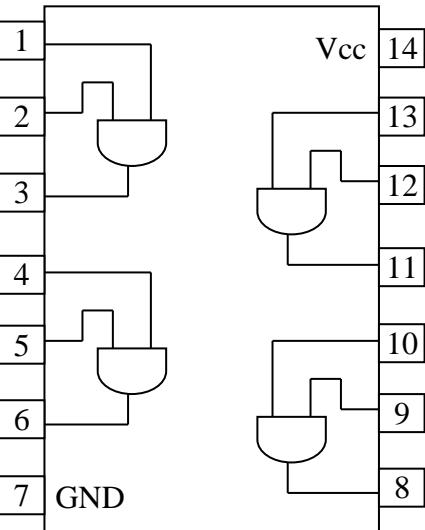

| ٤٧     | ٤ بوابات آند AND ثنائية المداخل                  | 7408        |

| ٤٧     | ٤ بوابات آند AND ثنائية المداخل مجمع مفتوح       | 7409        |

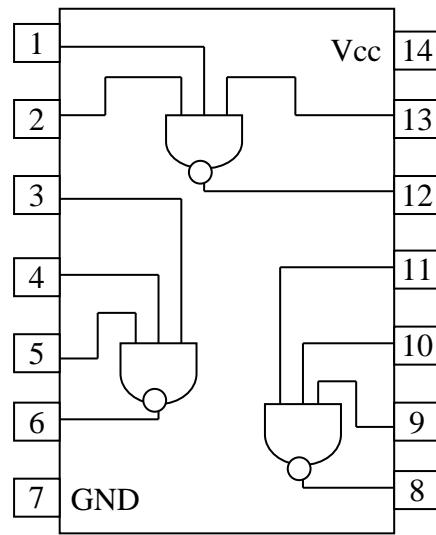

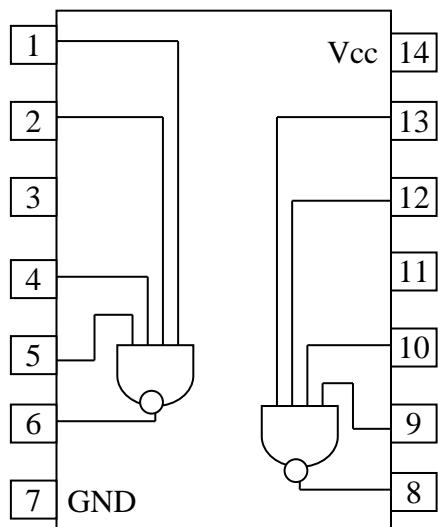

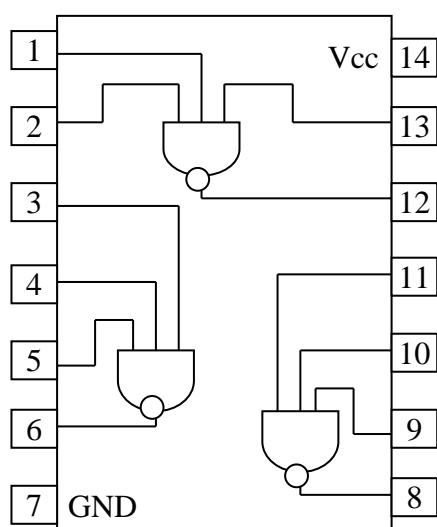

| ٤٩     | ٣ بوابات ناند NAND ثلاثة المداخل                 | 7410        |

| ٤٧     | ٣ بوابات آند AND ثلاثة المداخل                   | 7411        |

| ٤٩     | ٣ بوابات ناند NAND ثلاثة المداخل مجمع مفتوح      | 7412        |

| ٤٧     | ٣ بوابات آند AND ثلاثة المداخل مجمع مفتوح        | 7415        |

| ٤٦     | ٦ عواكس مفتوح المجمع ، دافع تيار                 | 7416        |

| ٤٦     | ٦ دافع تيار مفتوح المجمع                         | 7417        |

| ٤٩     | ٢ بوابة ناند NAND رباعية المداخل                 | 7420        |

| ٤٨     | ٢ بوابة آند AND رباعية المداخل                   | 7421        |

| ٥١     | ٢ بوابة نور NOR رباعية المداخل بطرف تنشيط Strobe | 7425        |

| ٤٨     | ٤ بوابات ناند NAND ثنائية المداخل                | 7426        |

| ٥١     | ٣ بوابات نور NOR ثلاثة المداخل                   | 7427        |

| ٥١     | ٤ بوابات نور NOR ثنائية المداخل                  | 7428        |

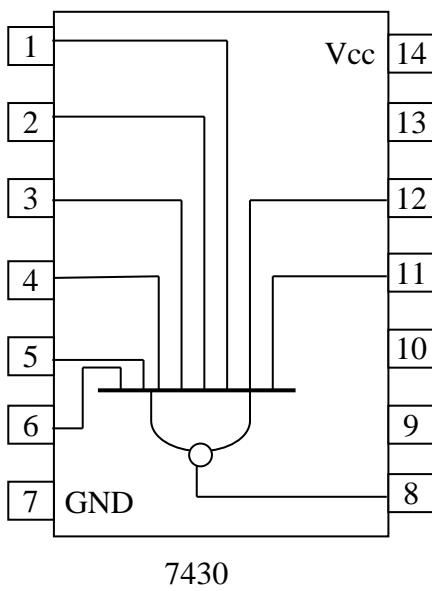

| ٥٠     | بوابة ناند NAND واحدة ثنائية المداخل             | 7430        |

| ٤٨     | ٤ بوابات أور OR ثنائية المداخل                   | 7432        |

| ٥١     | ٤ بوابات نور NOR ثنائية المداخل مفتوح المجمع     | 7433        |

| ٤٨     | ٤ بوابات ناند NAND ثنائية المداخل                | 7437        |

| ٤٨     | ٤ بوابات ناند NAND ثنائية المداخل مفتوح المجمع   | 7438        |

| ٤٩     | ٤ بوابات ناند NAND ثنائية المداخل مفتوح المجمع   | 7439        |

| ٤٩     | ٢ بوابة ناند NAND رباعية المداخل                 | 7440        |

|     |                                                                                                                                 |       |

|-----|---------------------------------------------------------------------------------------------------------------------------------|-------|

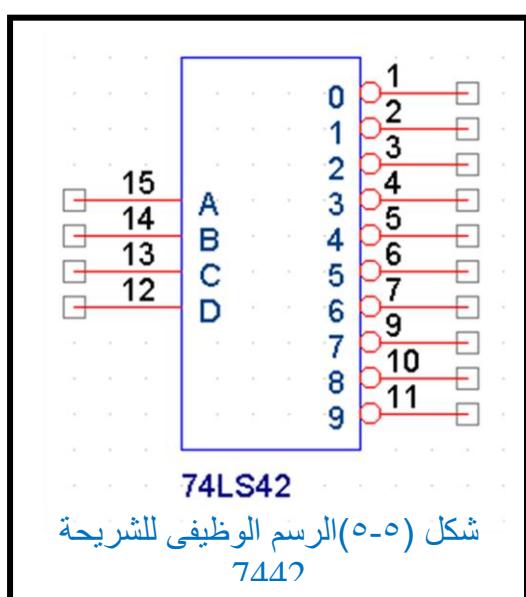

| ٧٧  | محلل شفرة ، شفرات عشرية مكودة ثنائيا BCD إلى عشري                                                                               | 7442  |

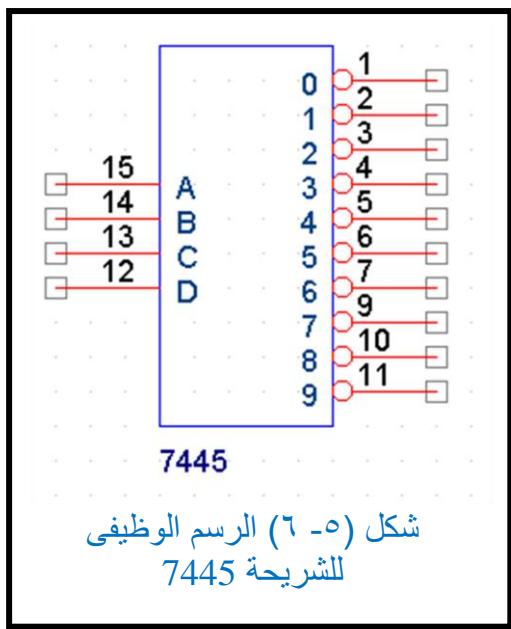

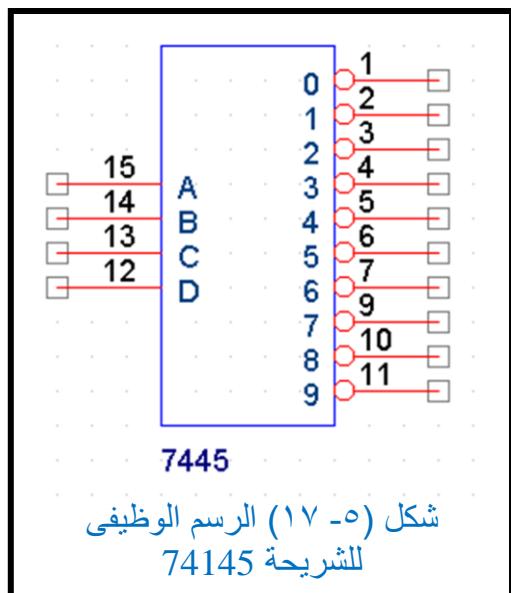

| ٧٧  | محلل شفرة ، شفرات عشرية مكودة ثنائيا BCD إلى عشري مفتوح المجمع                                                                  | 7445  |

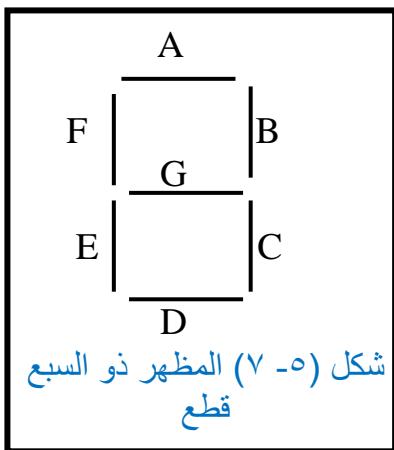

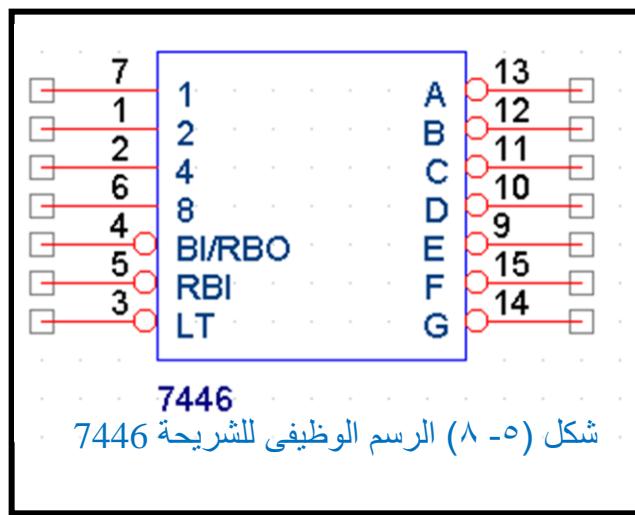

| ٧٨  | محلل شفرة ، شفرات عشرية مكودة ثنائيا BCD إلى شفرة السبع قطع ، دافع تيار ، خرج منخفض الفعالية ، للقطع متعددة الآنود Common anode | 7446  |

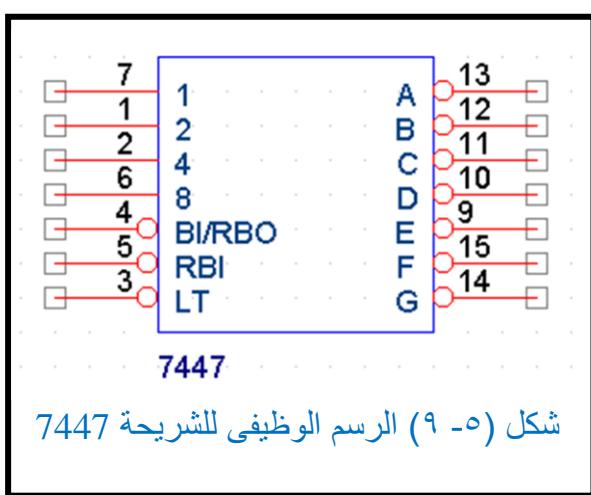

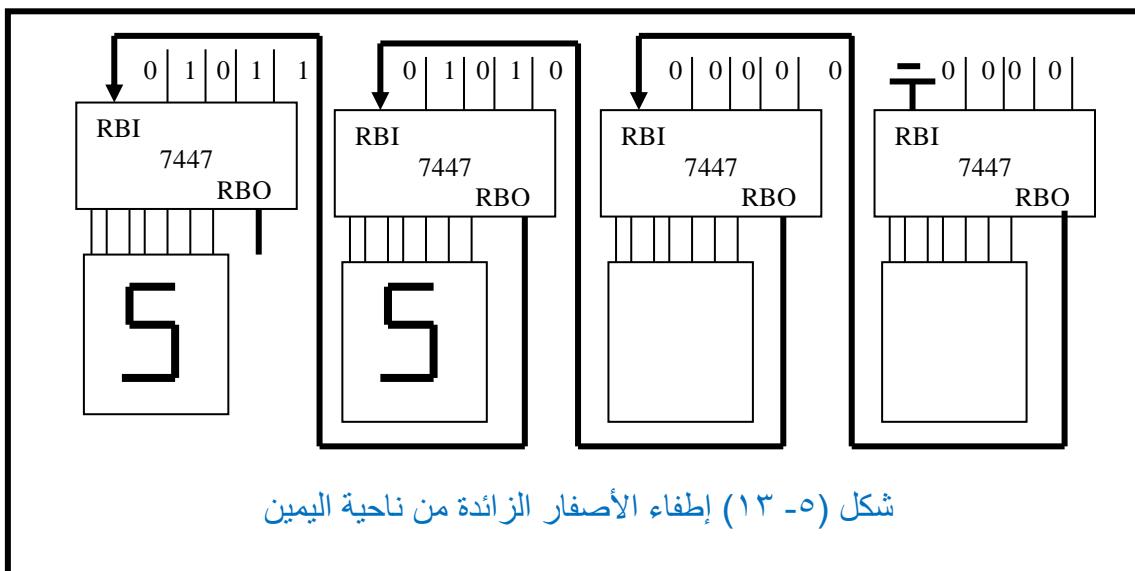

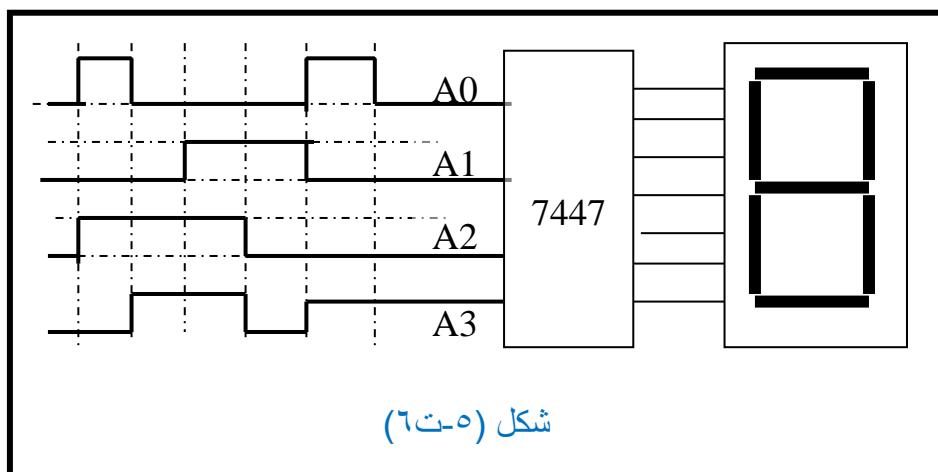

| ٧٨  | محلل شفرة ، شفرات عشرية مكودة ثنائيا BCD إلى شفرة السبع قطع ، دافع تيار ، خرج منخفض الفعالية ، للقطع متعددة الآنود Common anode | 7447  |

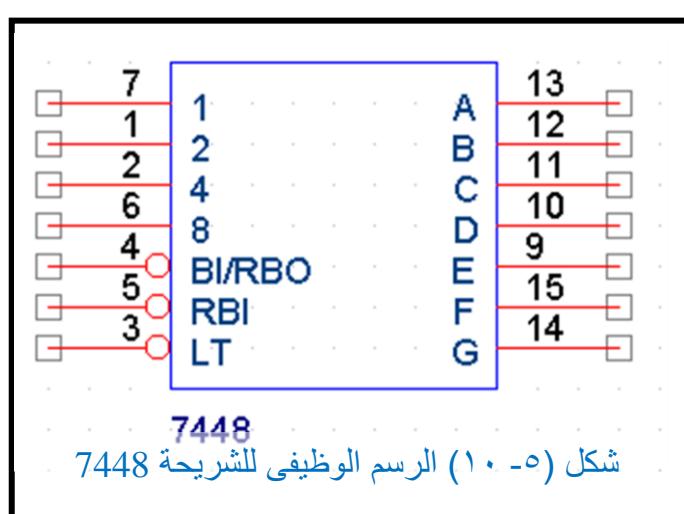

| ٧٨  | محلل شفرة ، شفرات عشرية مكودة ثنائيا BCD إلى شفرة السبع قطع ، دافع تيار ، خرج عالي الفعالية للقطع متعددة الكاثود Common cathode | 7448  |

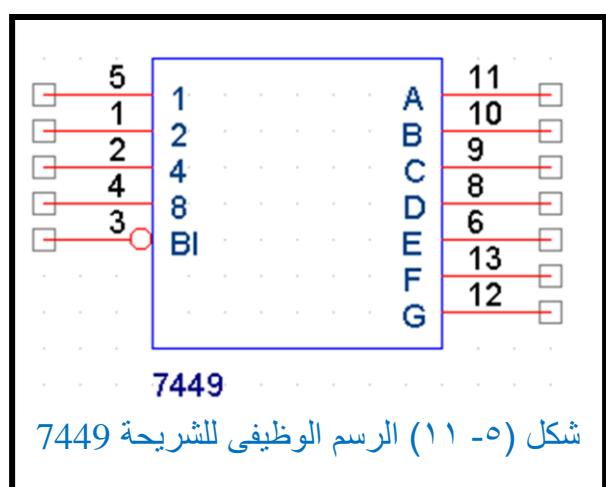

| ٧٨  | محلل شفرة ، شفرات عشرية مكودة ثنائيا BCD إلى شفرة السبع قطع ، دافع تيار ، خرج عالي الفعالية للقطع متعددة الكاثود Common cathode | 7449  |

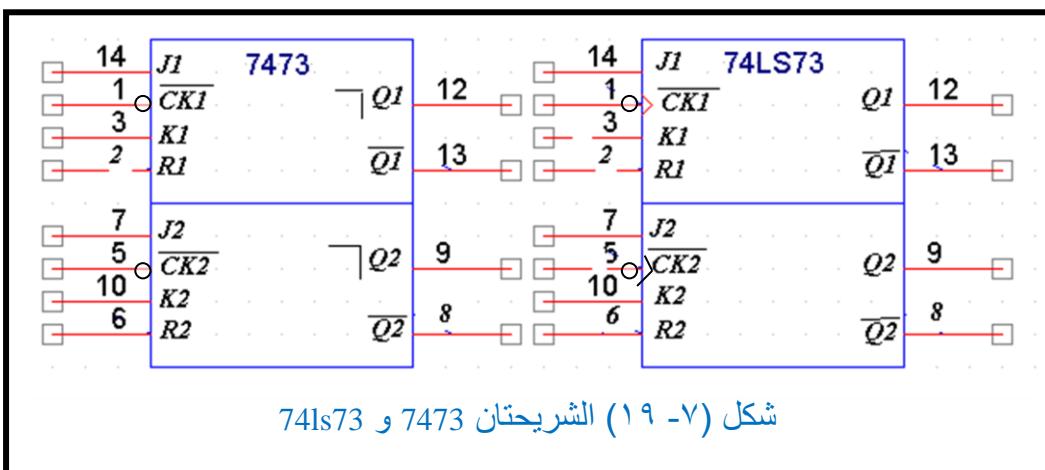

| ١٢٦ | ٢ قلاب JK                                                                                                                       | 7473  |

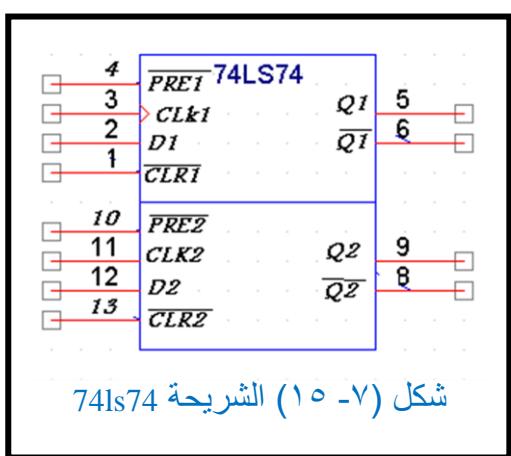

| ١٢٤ | ٢ قلاب D                                                                                                                        | 7474  |

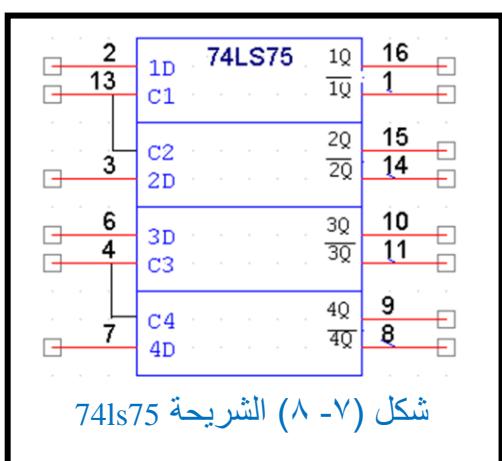

| ١٢٠ | ٤ ماسك Latch                                                                                                                    | 7475  |

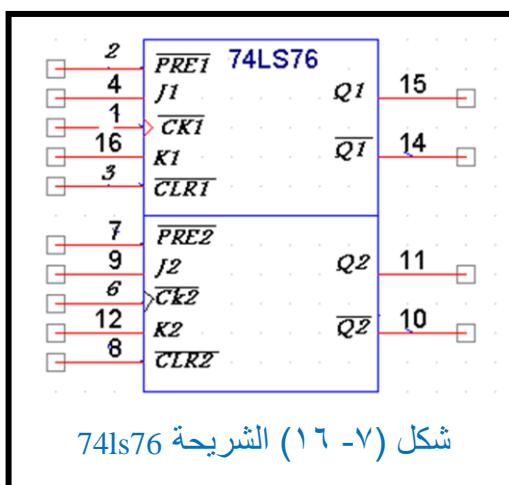

| ١٢٤ | ٢ قلاب JK                                                                                                                       | 7476  |

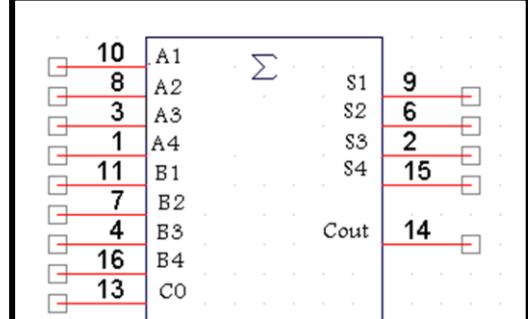

| ١٠٧ | مجموع كامل ٤ بت Full adder                                                                                                      | 7483  |

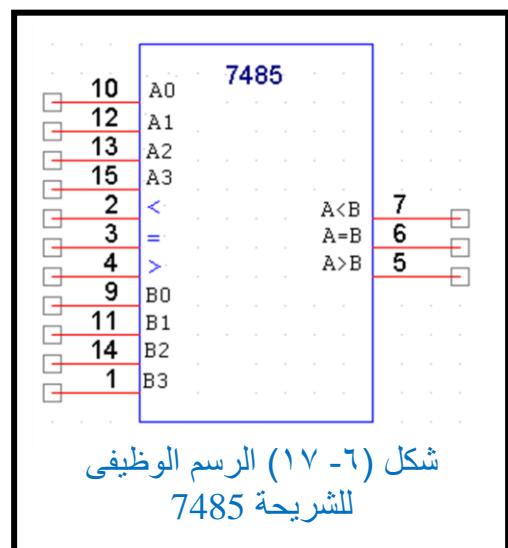

| ١١١ | مقارن ٤ بت Comparator                                                                                                           | 7485  |

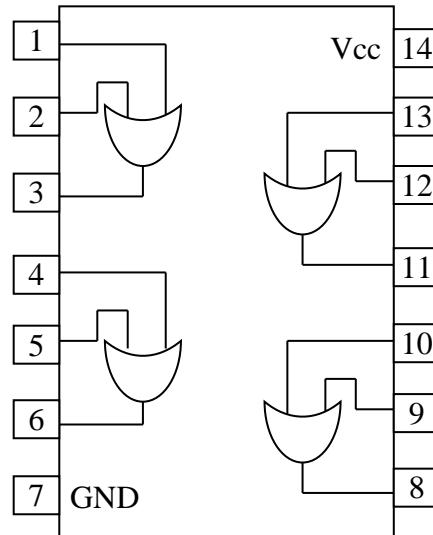

| ٥٢  | ٤ بوابات إكس أور XOR                                                                                                            | 7486  |

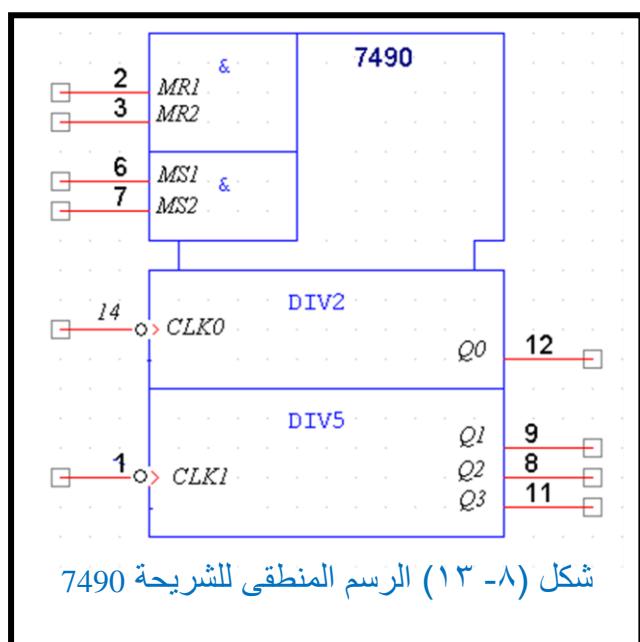

| ١٤٤ | عداد عشري ، قاسم على ١٠                                                                                                         | 7490  |

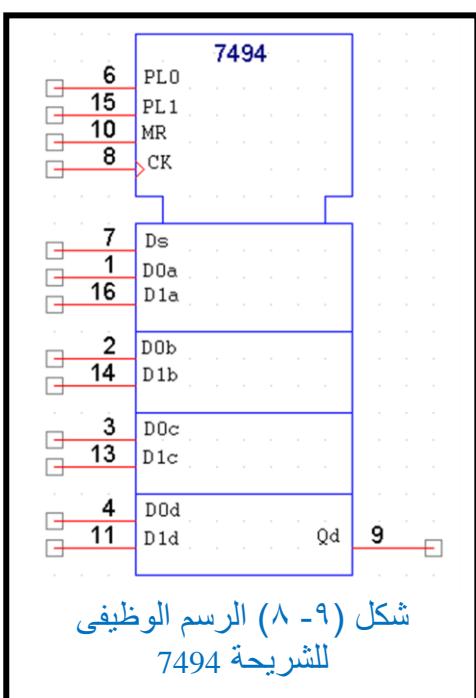

| ١٦٣ | مسجل إزاحة ٤ بت                                                                                                                 | 7491  |

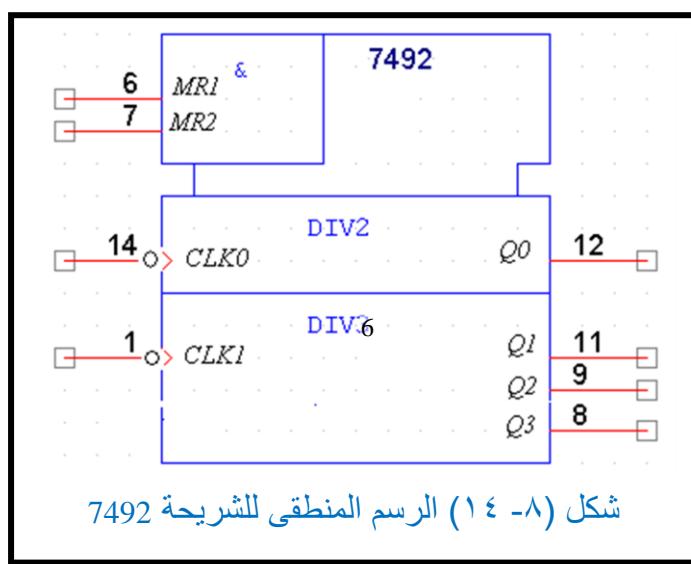

| ١٤٥ | عداد قاسم على ١٢                                                                                                                | 7492  |

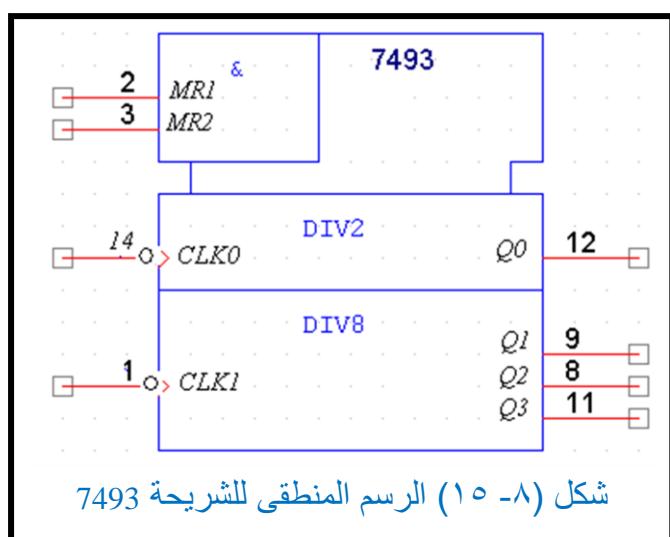

| ١٤٦ | عداد ثنائي توجي ٤ بت Ripple                                                                                                     | 7493  |

| ١٦٤ | مسجل إزاحة ٤ بت                                                                                                                 | 7494  |

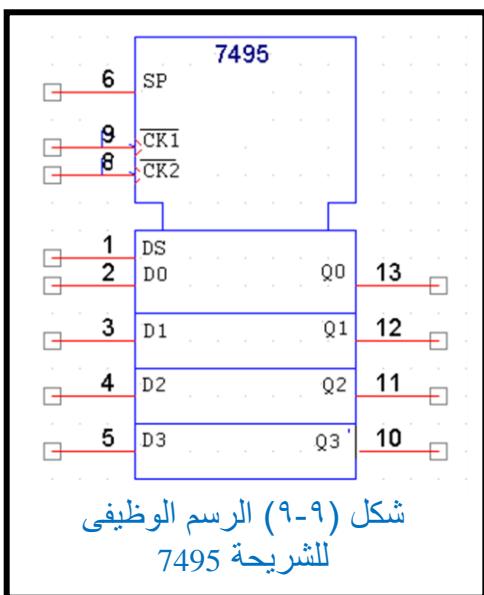

| ١٦٤ | مسجل إزاحة ٤ بت                                                                                                                 | 7495  |

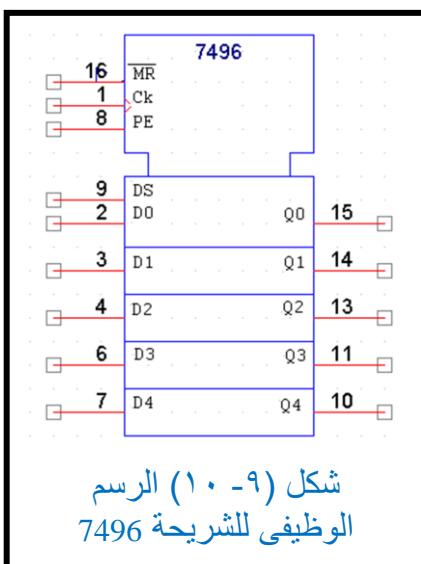

| ١٦٥ | مسجل إزاحة ٥ بت                                                                                                                 | 7496  |

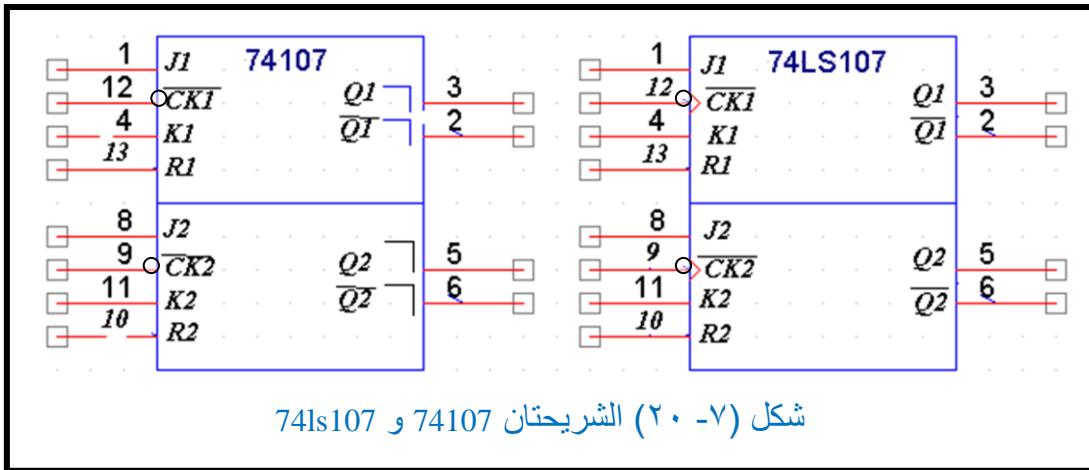

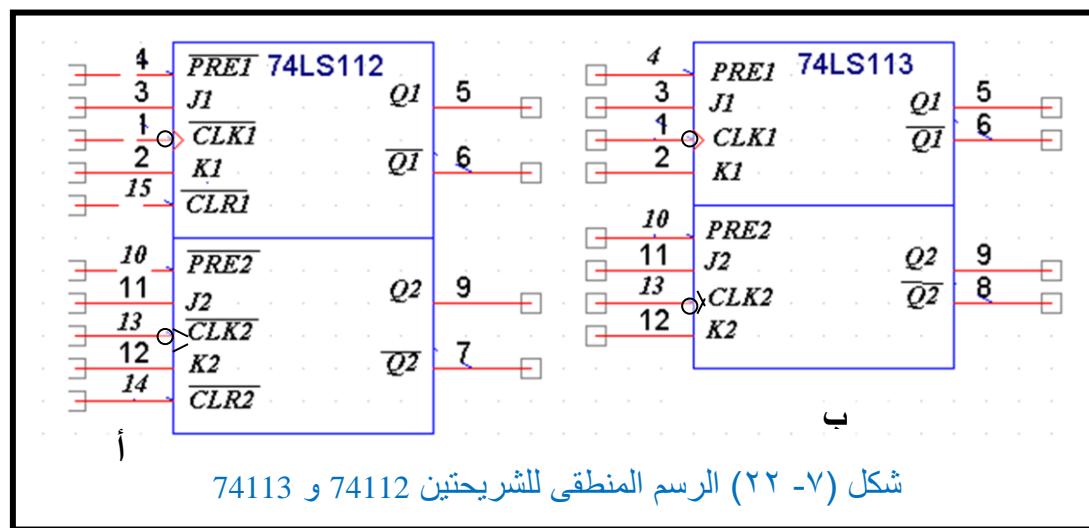

| ١٢٦ | ٢ قلاب JK                                                                                                                       | 74107 |

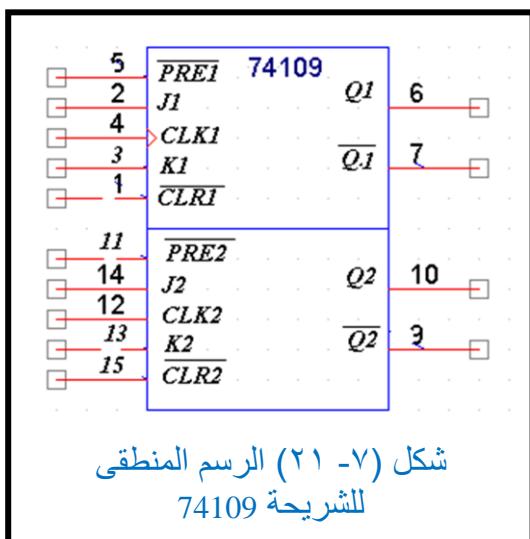

| ١٢٧ | ٢ قلاب JK                                                                                                                       | 74109 |

| ١٢٨ | ٢ قلاب JK                                                                                                                       | 74112 |

| ١٢٨ | ٢ قلاب JK                                                                                                                       | 74113 |

|     |                                                                        |       |

|-----|------------------------------------------------------------------------|-------|

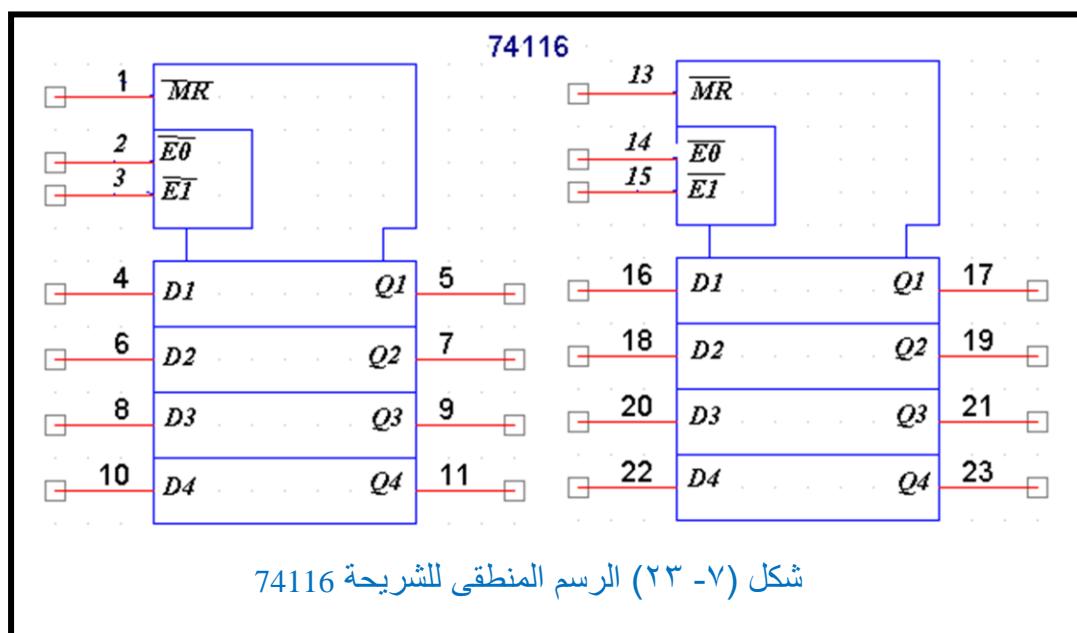

| ١٢٨ | ٢ ماسك كل منهم ٤ بت شفاف Transparent                                   | 74116 |

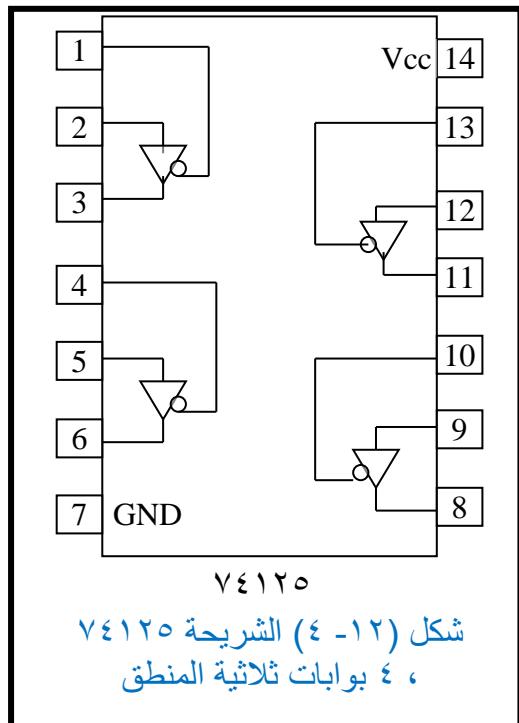

| ٢١٦ | ٤ بوابات ثلاثية المنطق                                                 | 74125 |

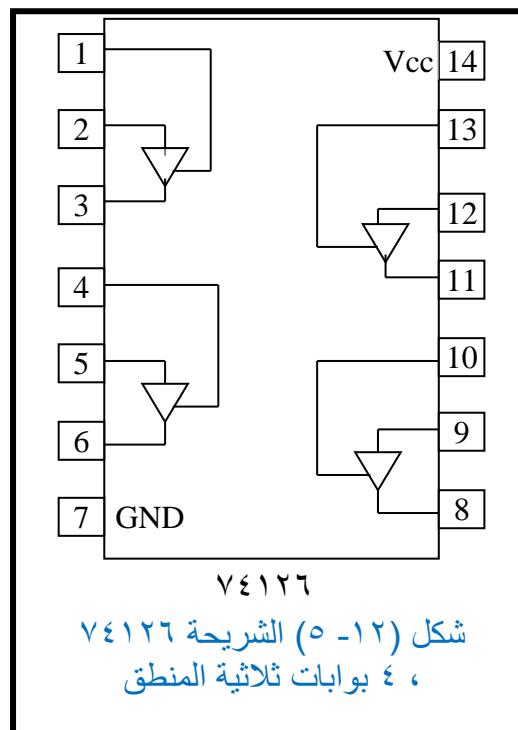

| ٢١٧ | ٤ بوابات ثلاثية المنطق                                                 | 74126 |

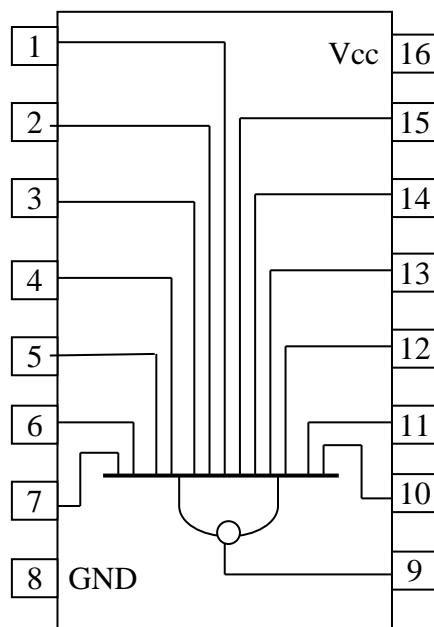

| ٥٠  | بوابة ناند NAND لها ١٣ دخل                                             | 74133 |

| ٥٠  | بوابة ناند NAND لها ١٢ دخل ، ثلاثية المنطق                             | 74134 |

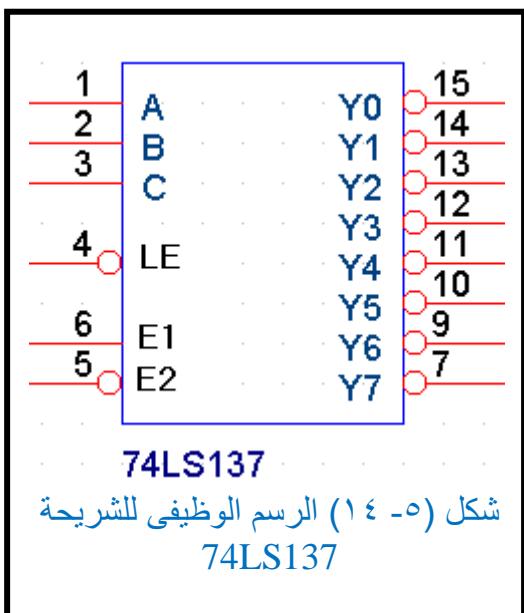

| ٨٢  | محلل شفرة Decoder ، أو موزع بيانات Demultiplexer ١ إلى ٨ مع ماسك للدخل | 74137 |

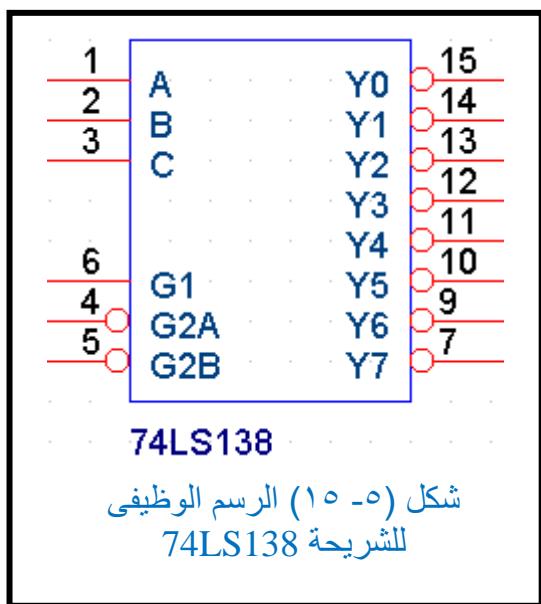

| ٨٣  | محلل شفرة ، أو موزع بيانات ١ إلى ٨                                     | 74138 |

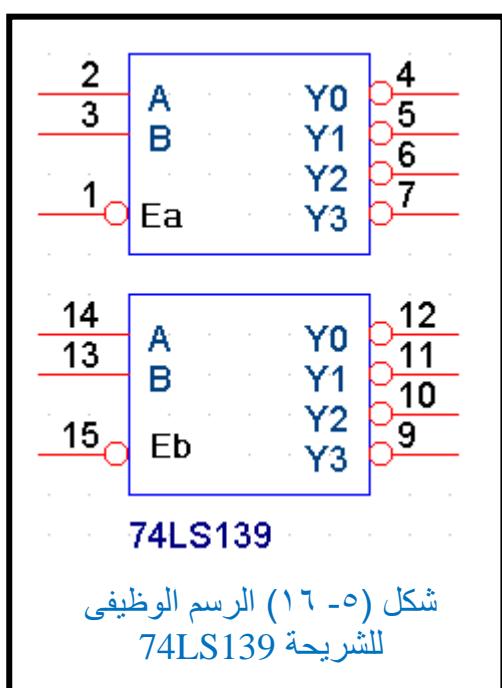

| ٨٤  | ٢ محلل شفرة أو موزع بيانات ١ إلى ٤                                     | 74139 |

| ٨٥  | محلل شفرة ، شفرات عشرية مكونة ثنائيا BCD إلى عشري مفتوح المجمع         | 74145 |

| ٨٨  | مشفر مع الأولوية ١٠ خطوط إلى ٤                                         | 74147 |

| ٩٠  | مشفر مع الأولوية ٨ إلى ٣                                               | 74148 |

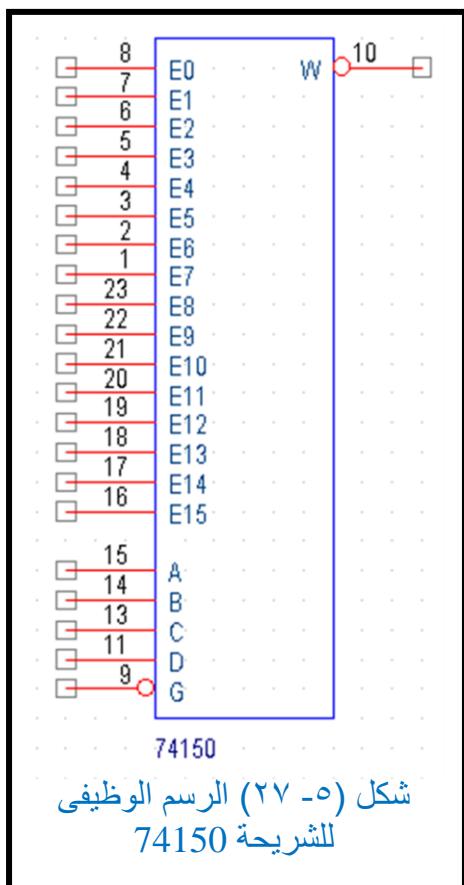

| ٩٣  | منتقى بيانات ١٦ Multiplexer دخل                                        | 74150 |

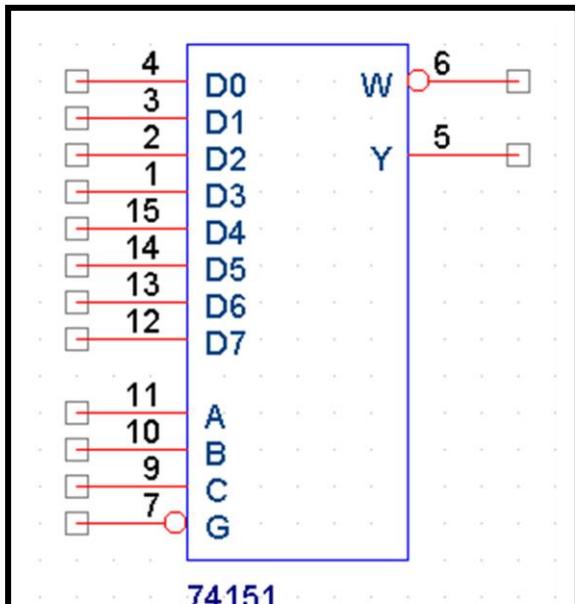

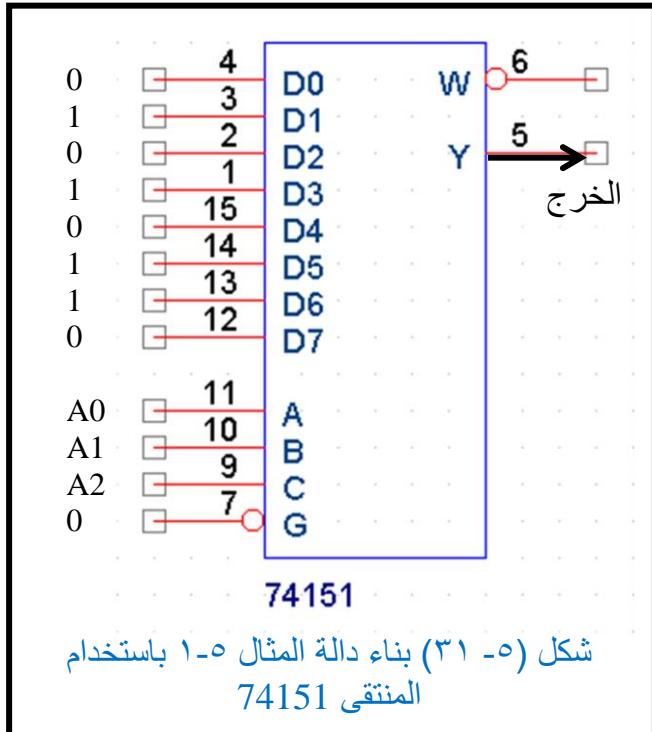

| ٩٤  | منتقى بيانات ٨ Multiplexer ٨ دخل                                       | 74151 |

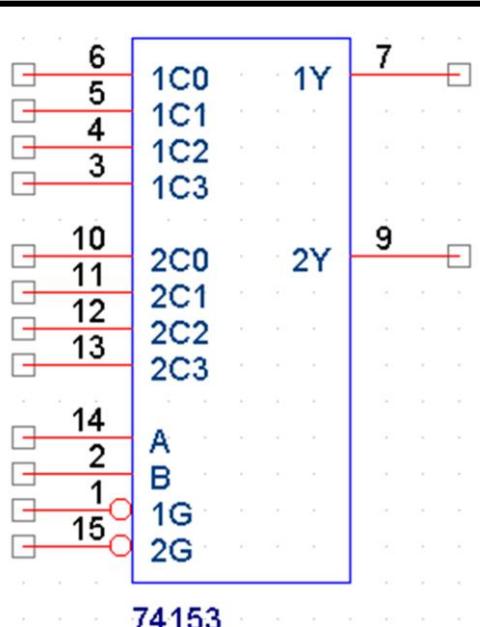

| ٩٤  | ٢ منتقمى بيانات ٤ خطوط إلى واحد                                        | 74153 |

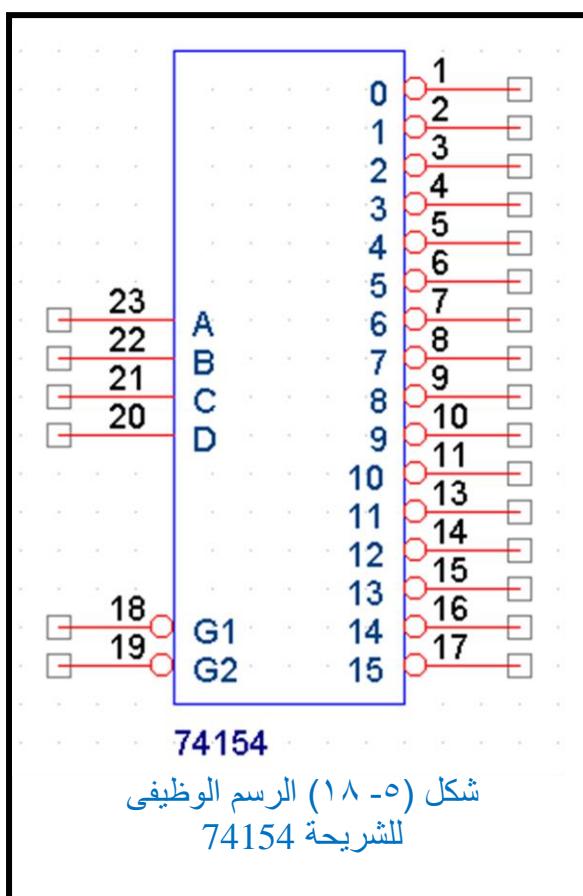

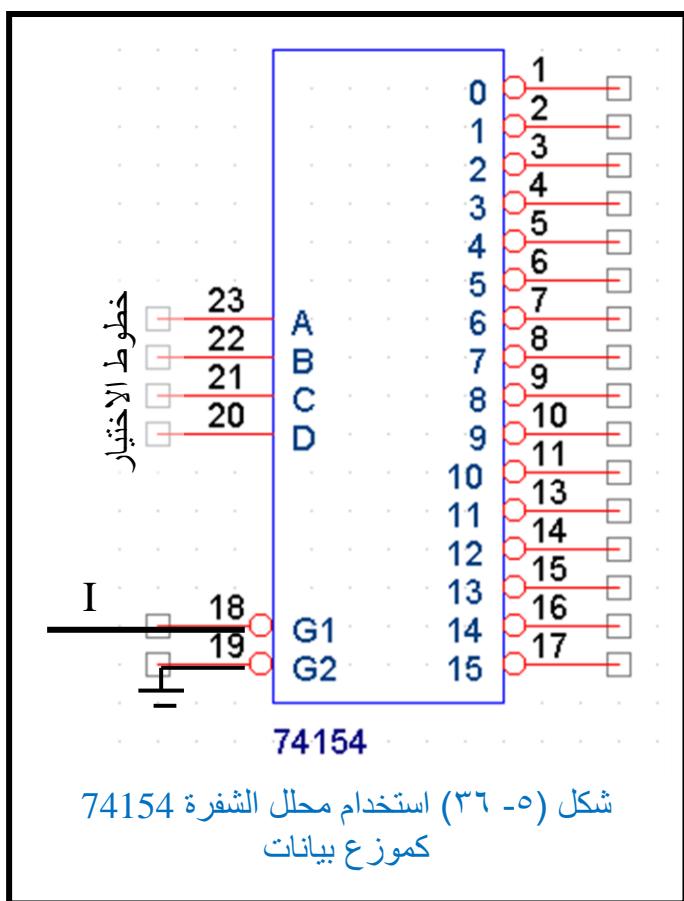

| ٨٦  | محلل شفرة Decoder ، أو موزع بيانات ١ إلى ١٦                            | 74154 |

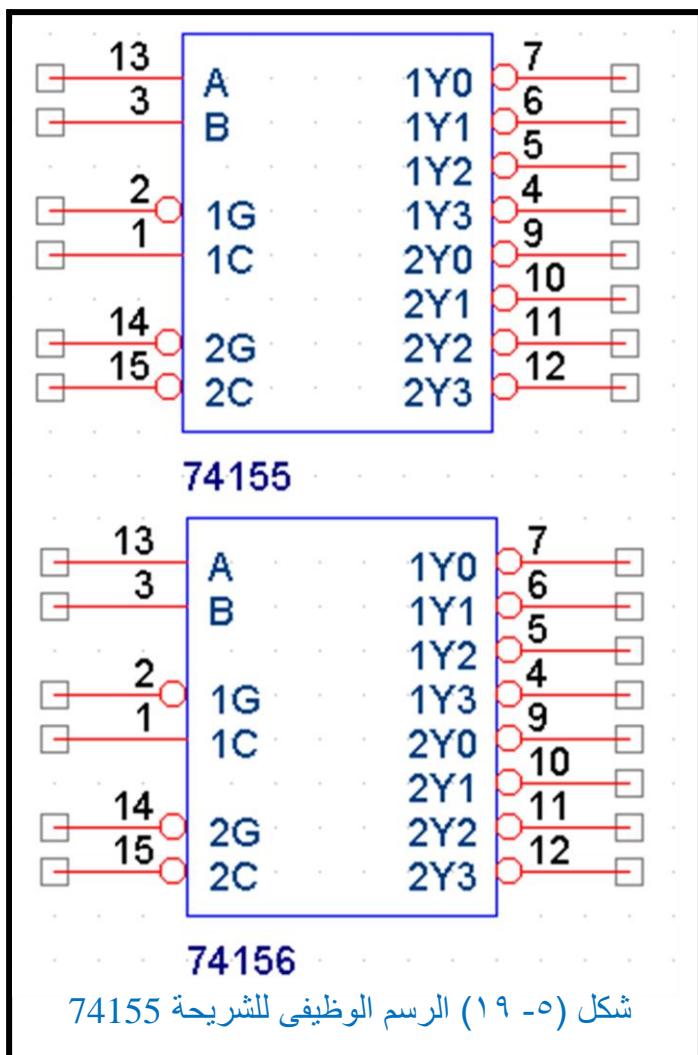

| ٨٦  | ٢ محلل شفرة ، موزع بيانات ٢ إلى ٤                                      | 74155 |

| ٨٧  | ٢ محلل شفرة ، موزع بيانات ٢ إلى ٤ ، مجمع مفتوح                         | 74156 |

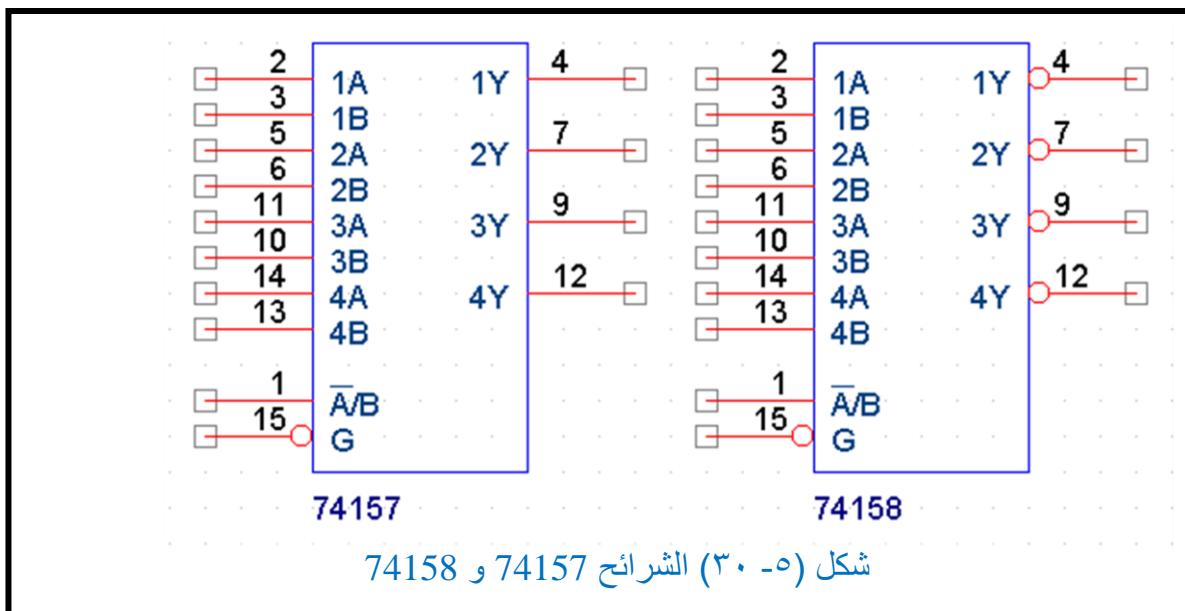

| ٩٥  | ٤ منتقمى بيانات MUX كل منهم له دخالان                                  | 74157 |

| ٩٥  | ٤ منتقمى بيانات MUX كل منهم له دخالان والخرج معكوس                     | 74158 |

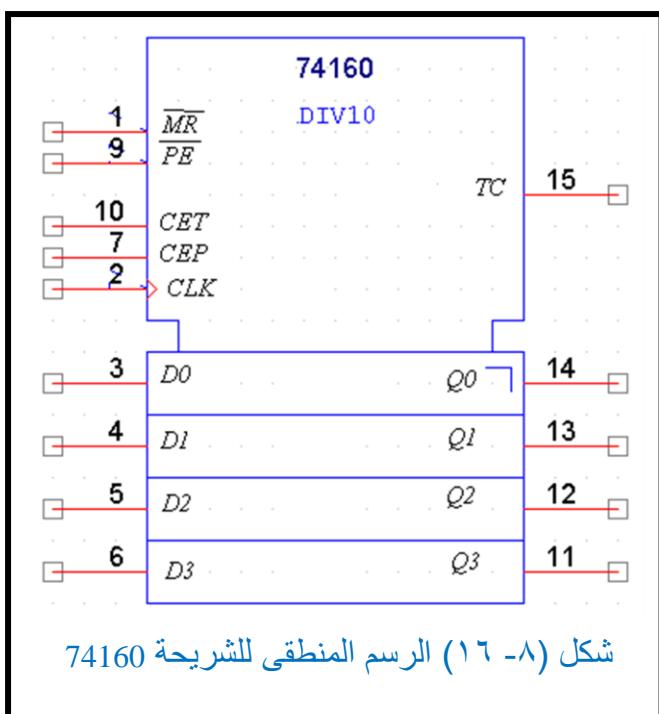

| ١٤٧ | عداد عشري                                                              | 74160 |

| ١٤٧ | عداد ثنائى                                                             | 74161 |

| ١٤٧ | عداد عشري                                                              | 74162 |

| ١٤٧ | عداد ثنائى                                                             | 74163 |

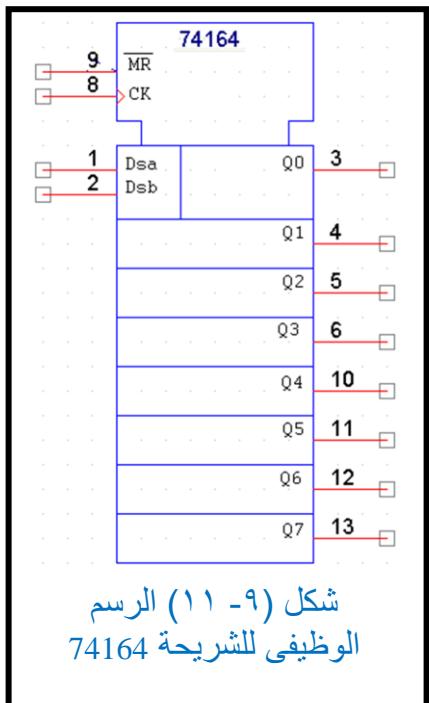

| ١٦٧ | مسجل إزاحة ٨ بت                                                        | 74164 |

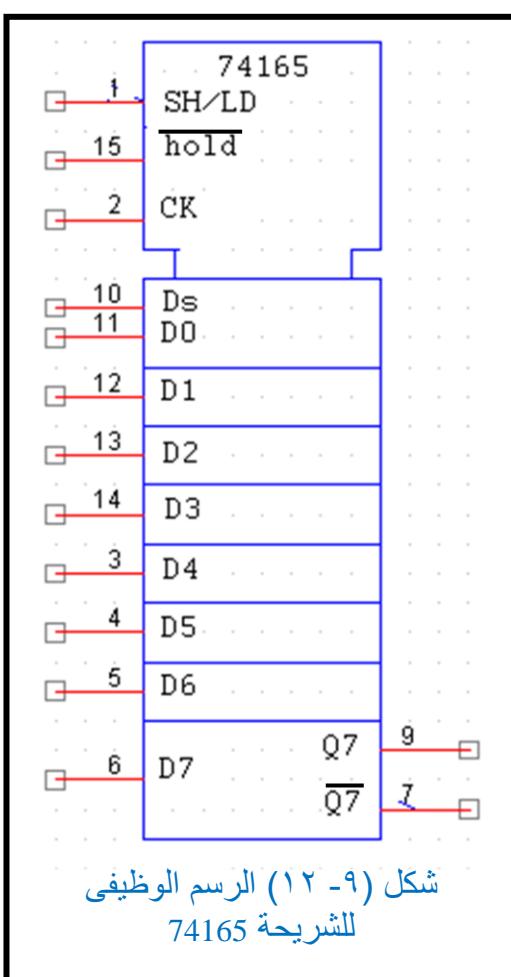

| ١٦٧ | مسجل إزاحة ٨ بت                                                        | 74165 |

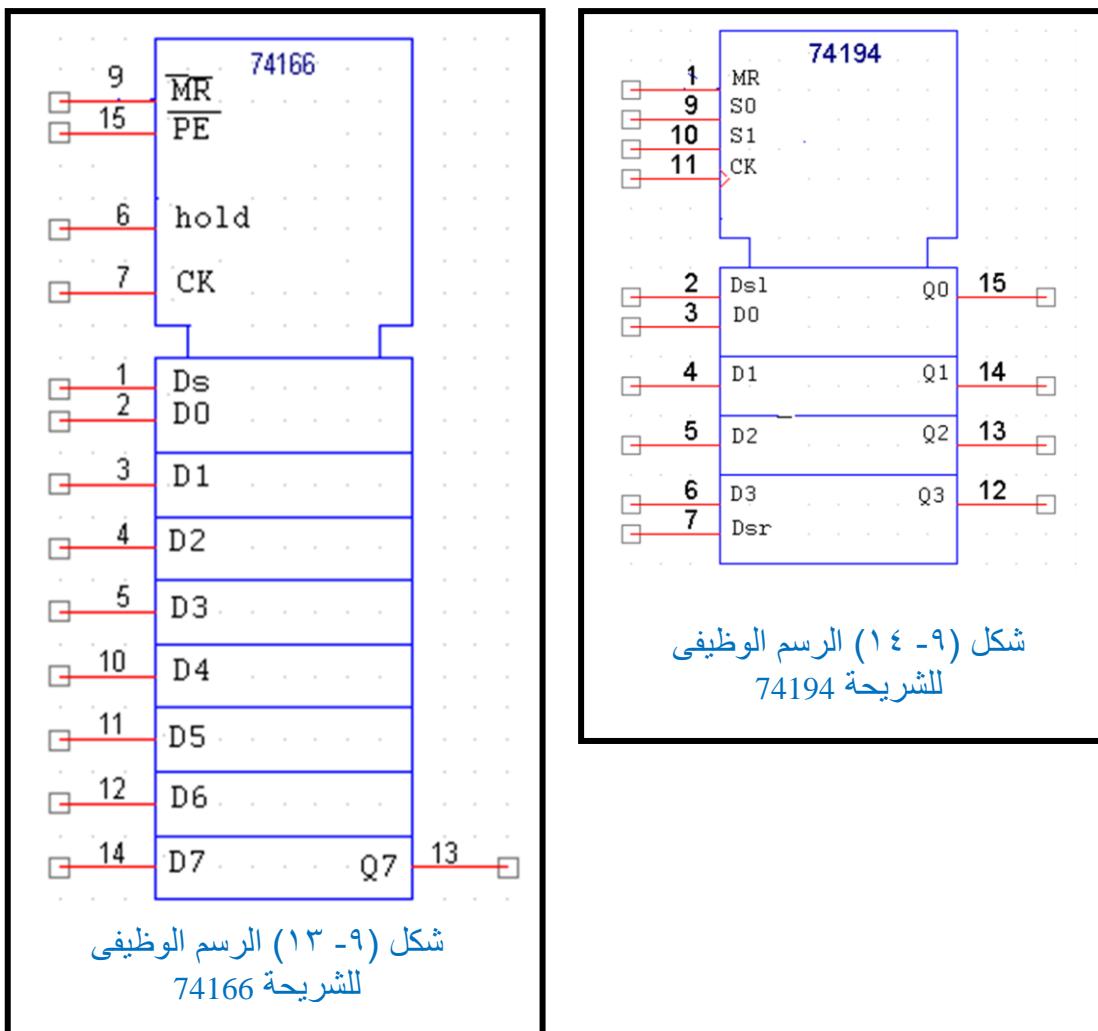

| ١٦٧ | مسجل إزاحة ٨ بت                                                        | 74166 |

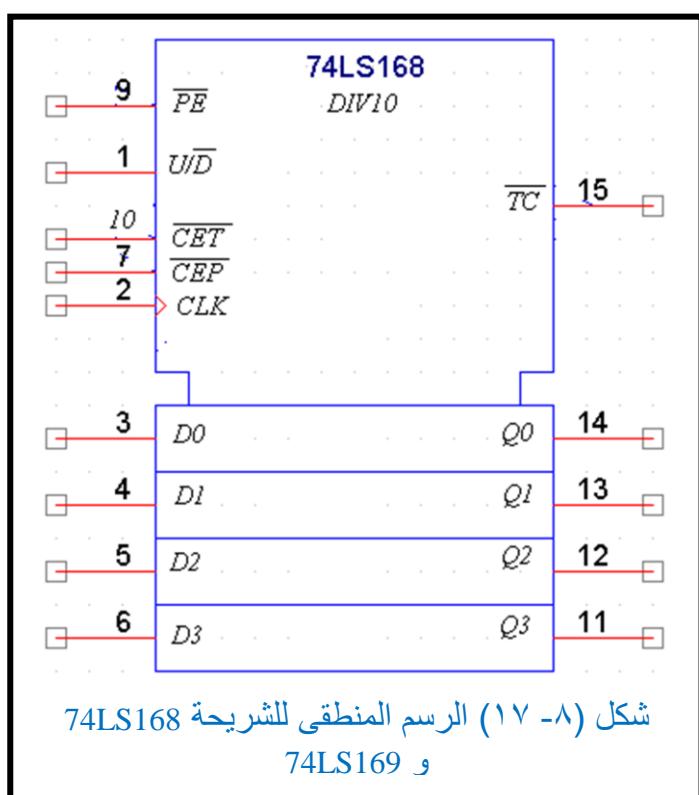

| ١٤٨ | عداد ثنائى ٤ بت تصاعدى تنازلى توافقى                                   | 74168 |

| ١٤٨ | عداد ثنائى ٤ بت تصاعدى تنازلى توافقى                                   | 74169 |

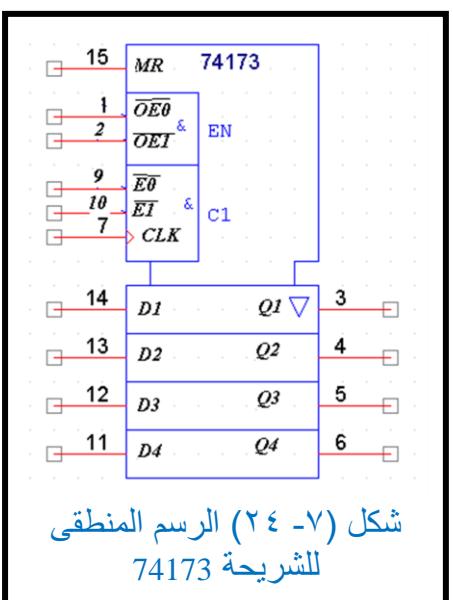

| ١٢٩ | ٢ قلاب D بخرج ثلاثي المنطق                                             | 74173 |

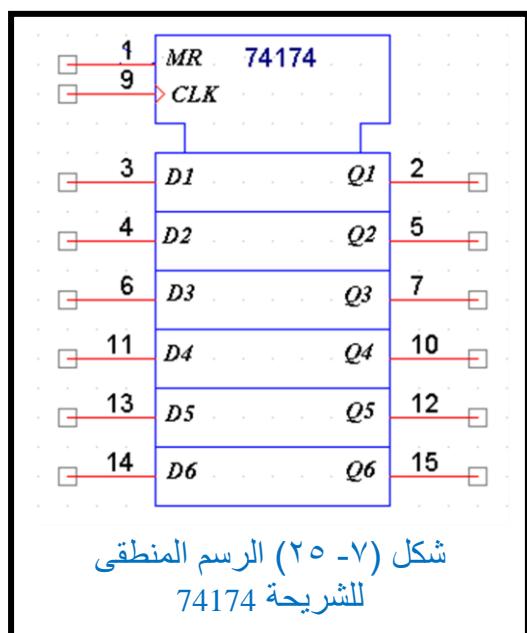

| ١٢٩ | ٦ قلاب D                                                               | 74174 |

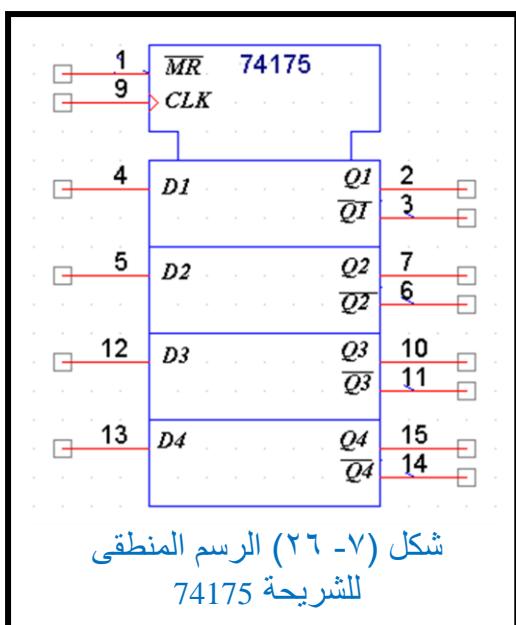

| ١٣٠ | ٤ قلاب D                                                               | 74175 |

|     |                                             |       |

|-----|---------------------------------------------|-------|

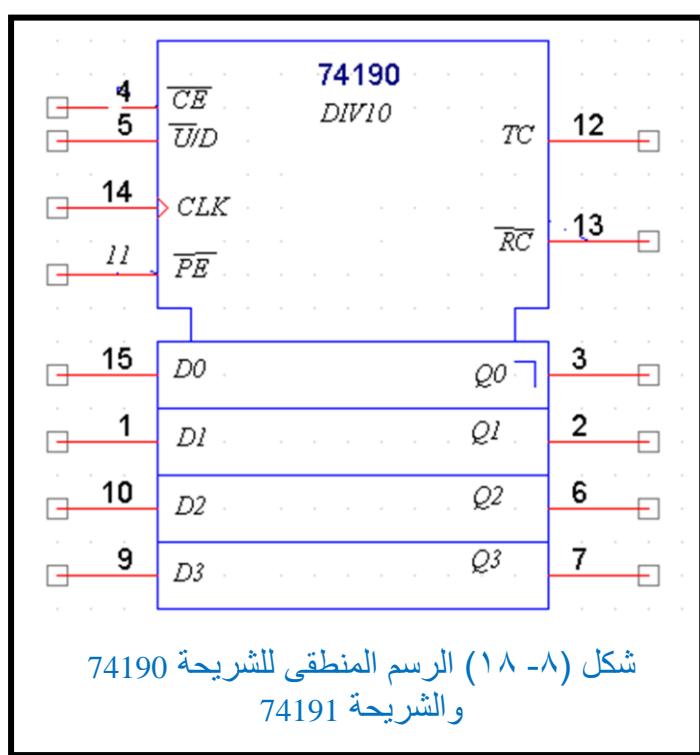

| ١٤٩ | عداد عشرى تصاعدى تنازلى                     | 74190 |

| ١٤٩ | عداد ثنائى تصاعدى تنازلى                    | 74191 |

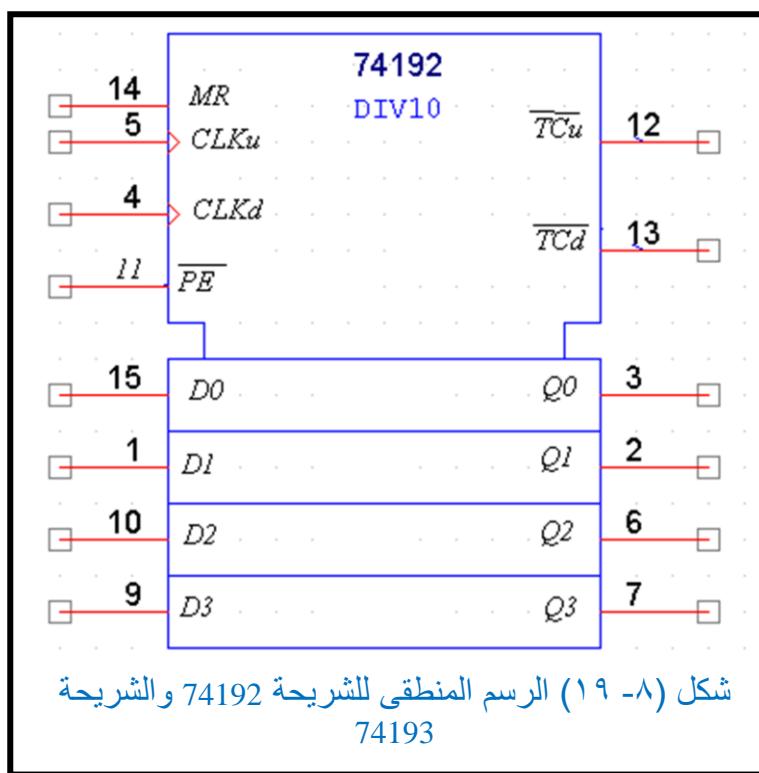

| ١٥٠ | عداد عشرى تصاعدى تنازلى                     | 74192 |

| ١٥٠ | عداد ثنائى تصاعدى تنازلى                    | 74193 |

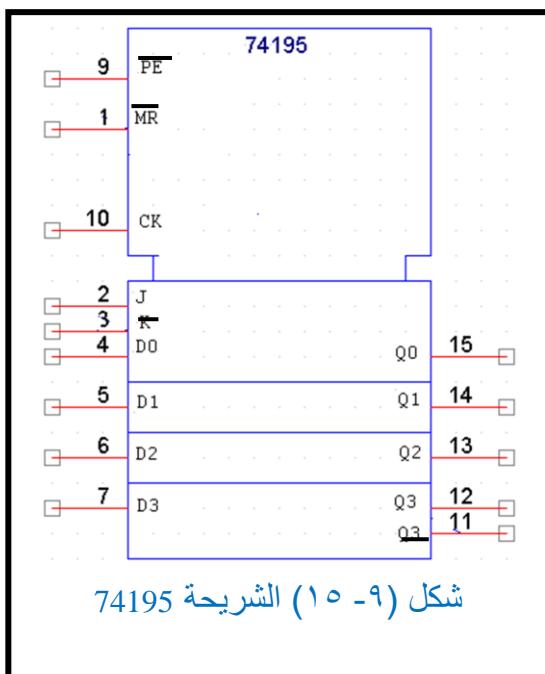

| ١٦٧ | مسجل إزاحة ٤ بت عام الأغراض                 | 74194 |

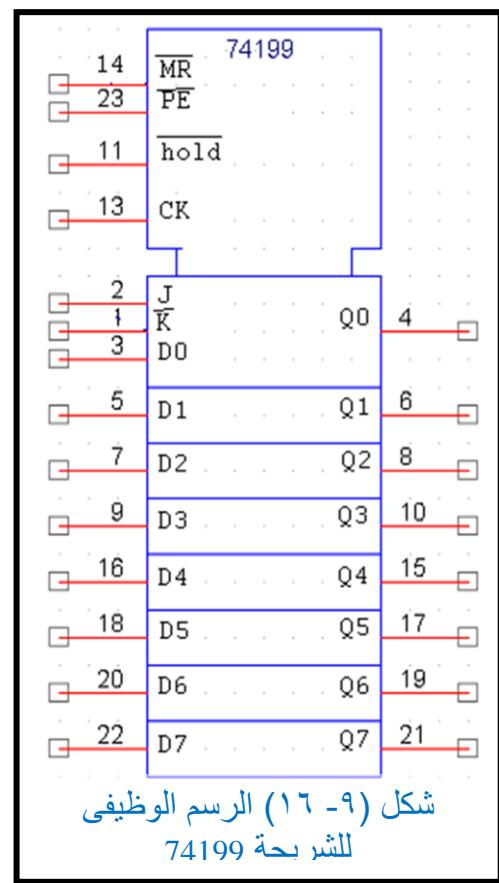

| ١٦٨ | مسجل إزاحة ٤ بت                             | 74195 |

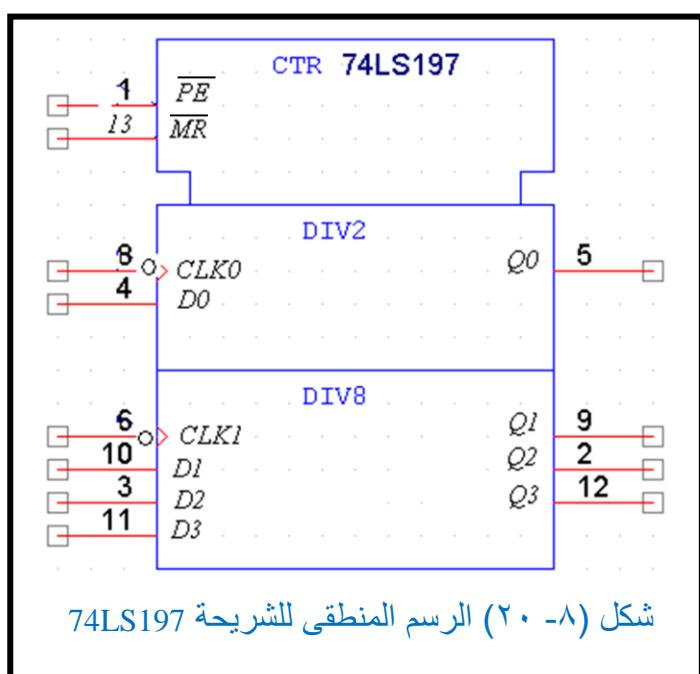

| ١٥١ | عداد ثنائى ٤ بت توجى                        | 74197 |

| ١٧٩ | مسجل إزاحة ٨ بت                             | 74199 |

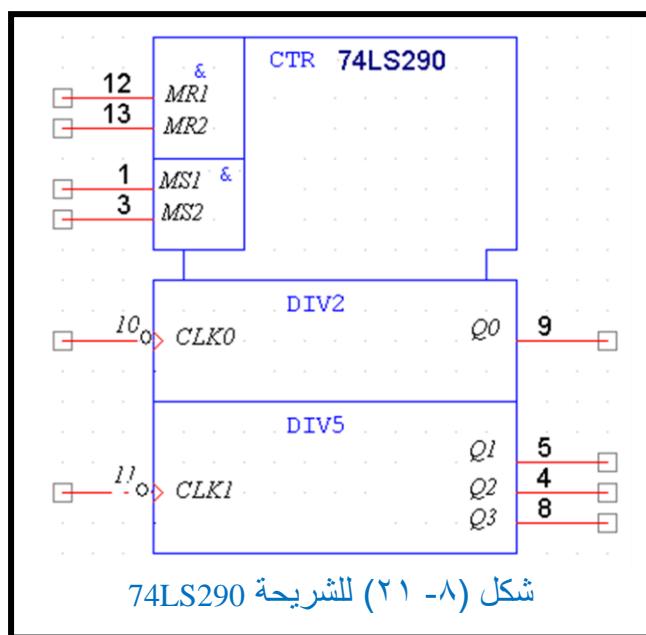

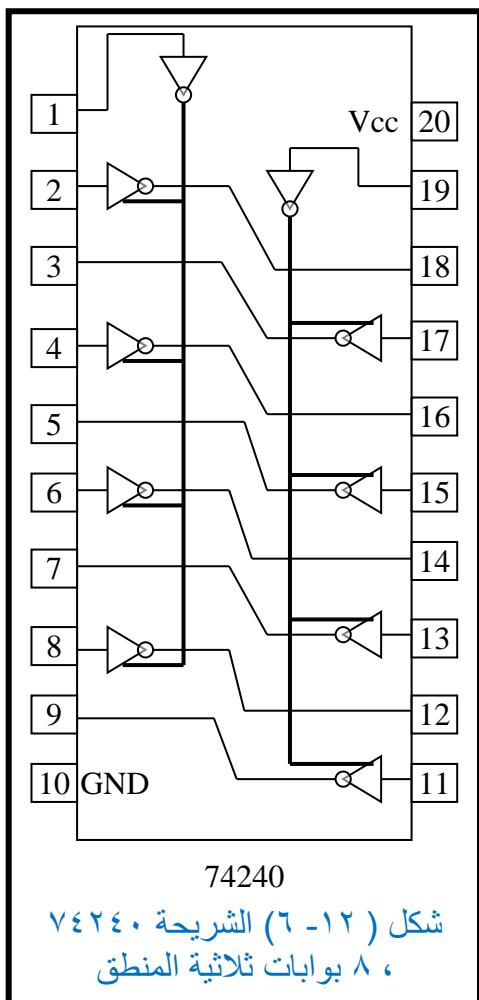

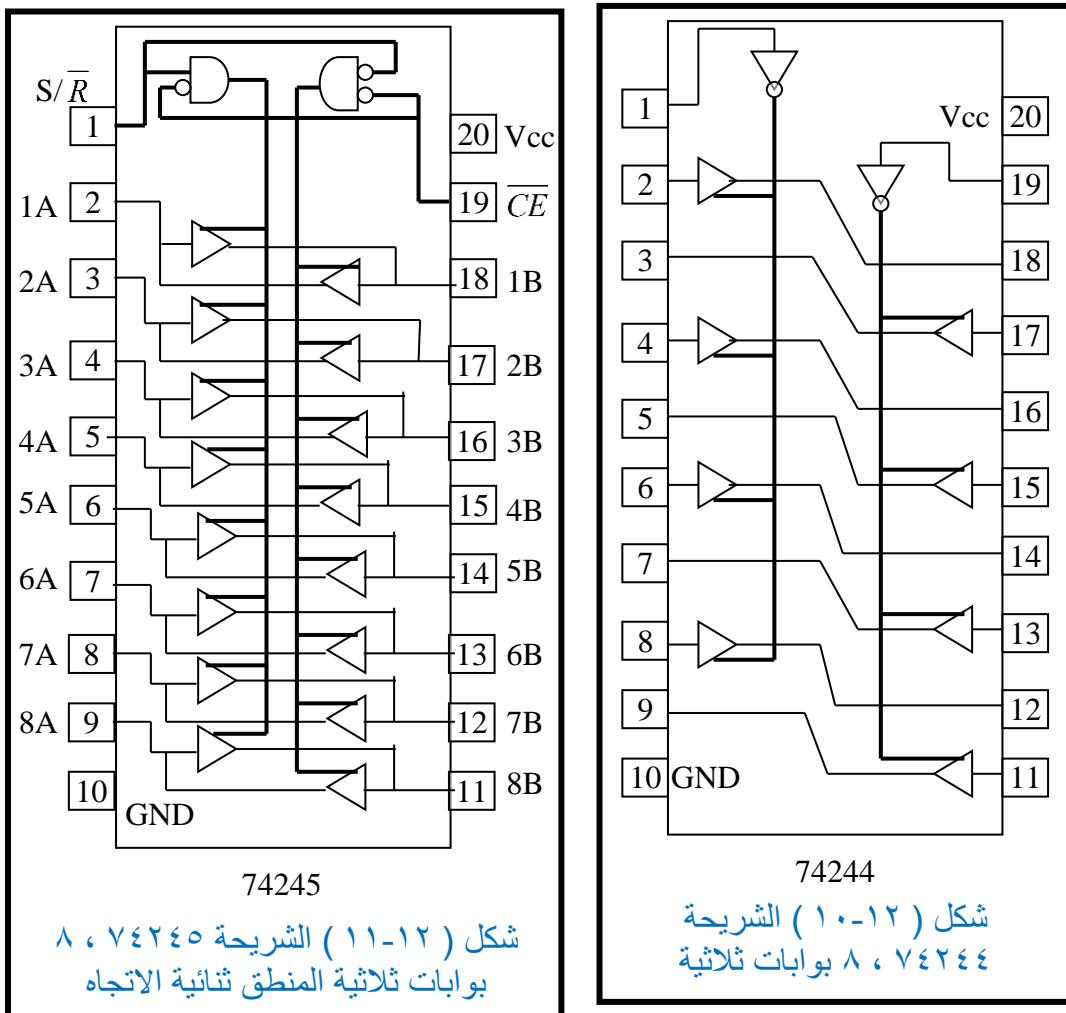

| ٢١٧ | ٨ بوابات ثلاثة المنطق                       | 74240 |

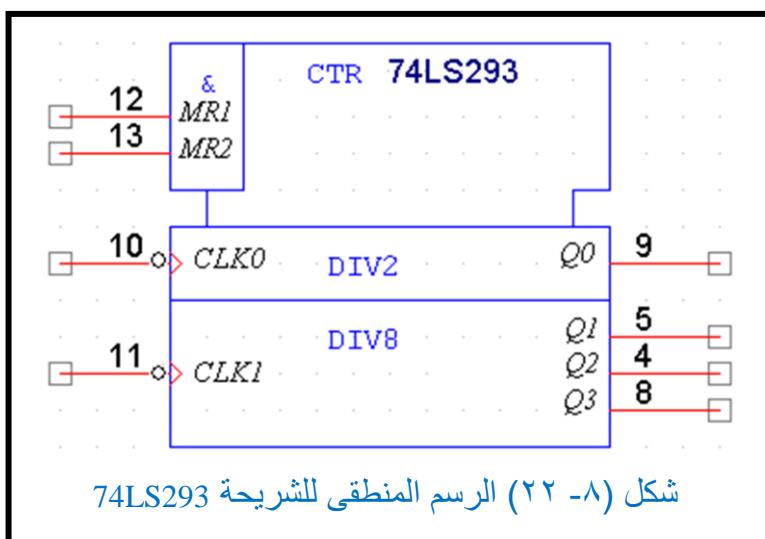

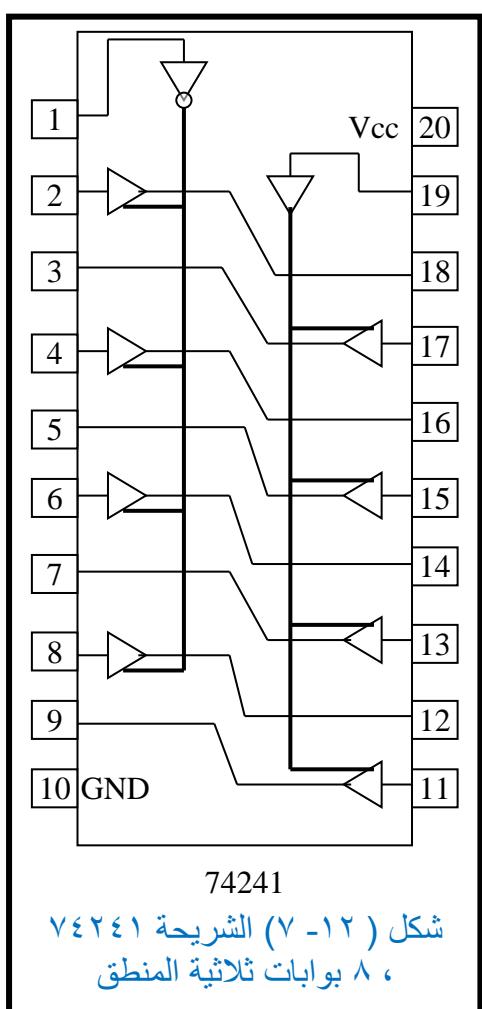

| ٢١٨ | ٨ بوابات ثلاثة المنطق                       | 74241 |

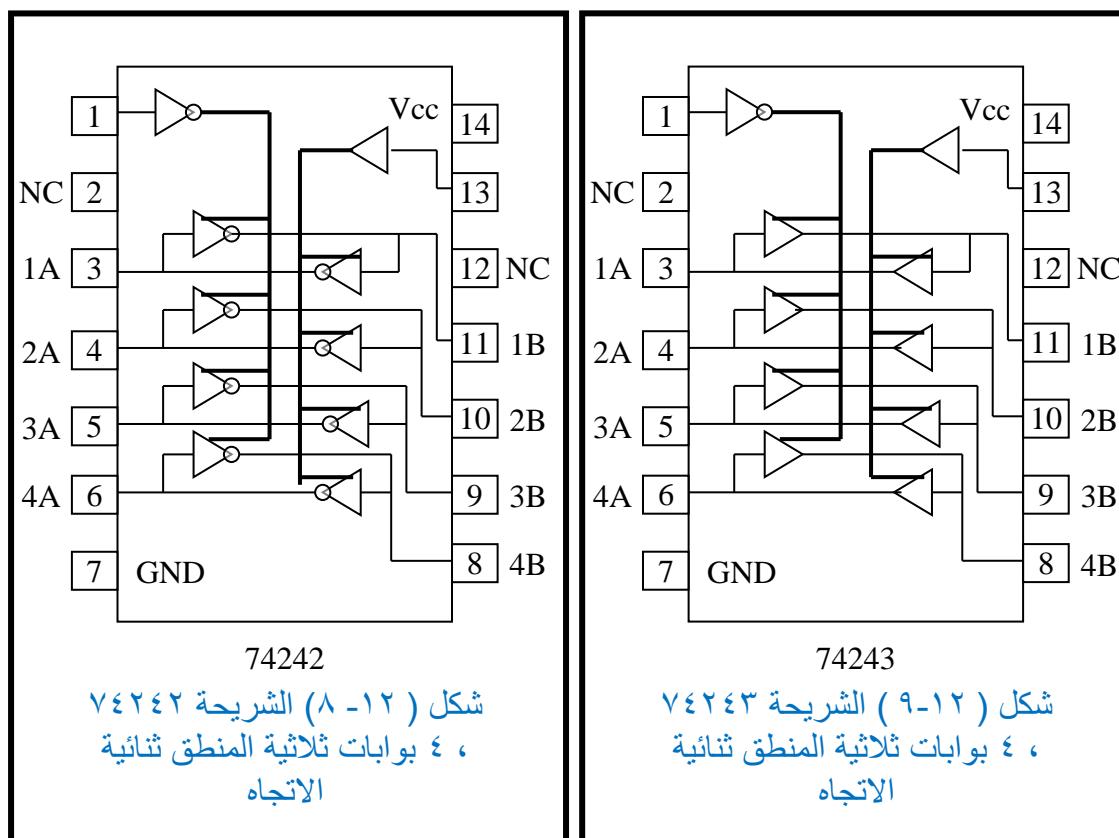

| ٢١٨ | ٤ بوابات ثلاثة المنطق ثنائية الاتجاه        | 74242 |

| ٢١٨ | ٤ بوابات ثلاثة المنطق ثنائية الاتجاه        | 74243 |

| ٢١٨ | ٨ بوابات ثلاثة المنطق                       | 74244 |

| ٢١٩ | ٨ بوابات ثلاثة المنطق ثنائية الاتجاه        | 74245 |

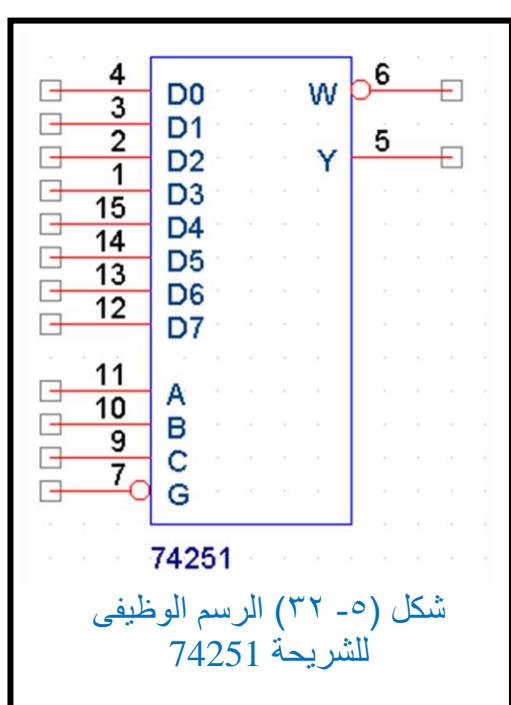

| ٩٦  | منتقى بيانات ٨ دخول ، خرج ثلاثي المنطق      | 74251 |

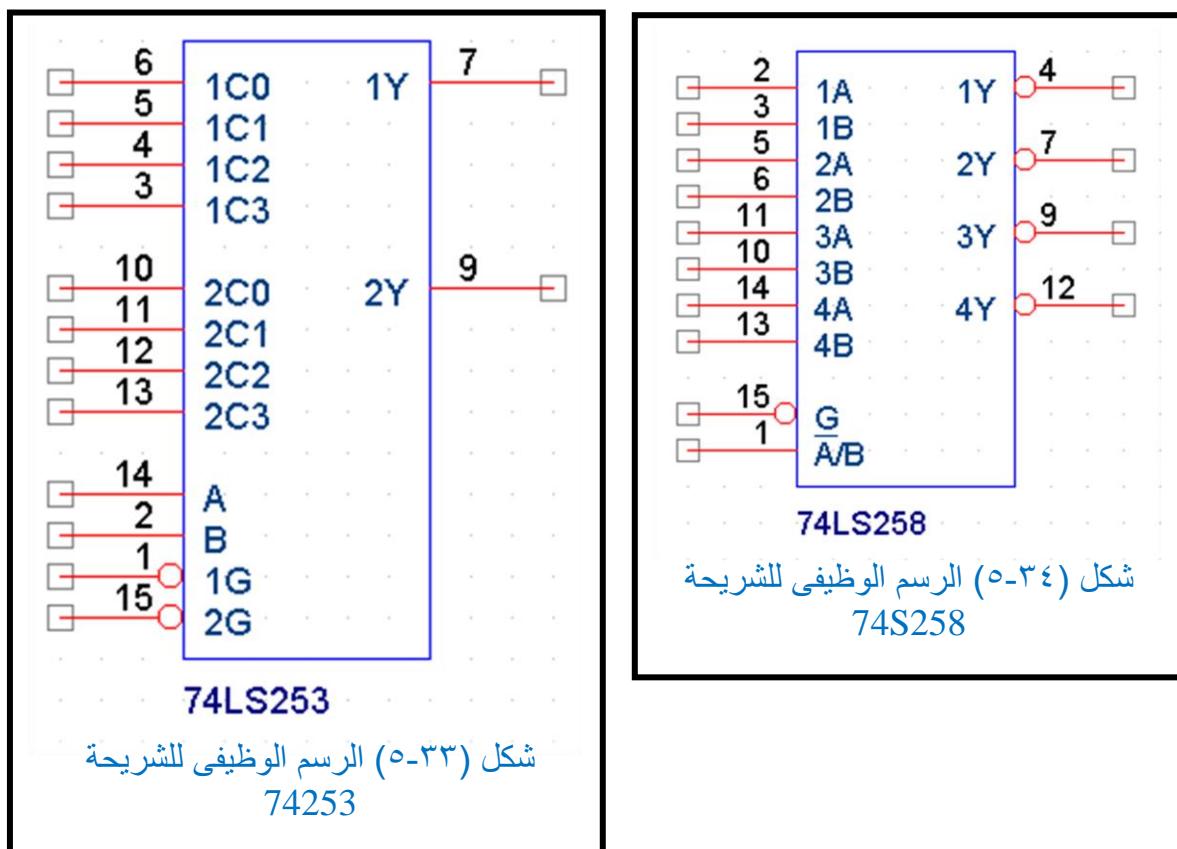

| ٩٧  | ٢ منتقى بيانات ، ٤ دخول ، خرج ثلاثي المنطق  | 74253 |

| ٩٧  | ٤ منتقى بيانات ، ٢ دخل ، خرج ثلاثي المنطق   | 74258 |

| ٥٢  | ٤ بوابات إكس نور XNOR بدخلين ، مفتوح المجمع | 74266 |

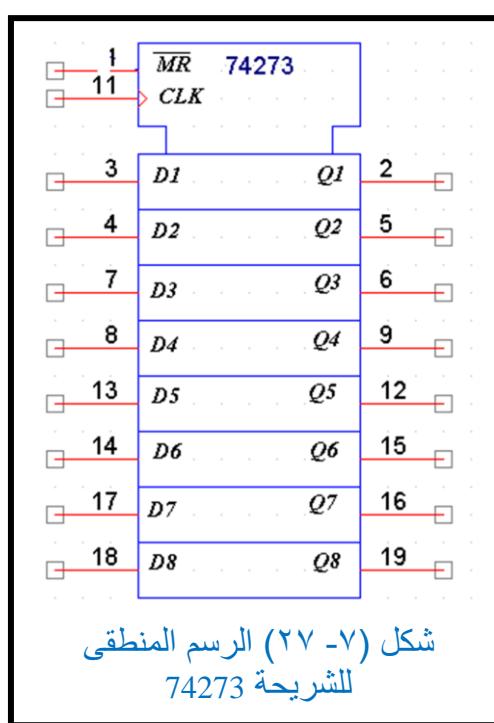

| ١٣٠ | ٨ قلابات D                                  | 74273 |

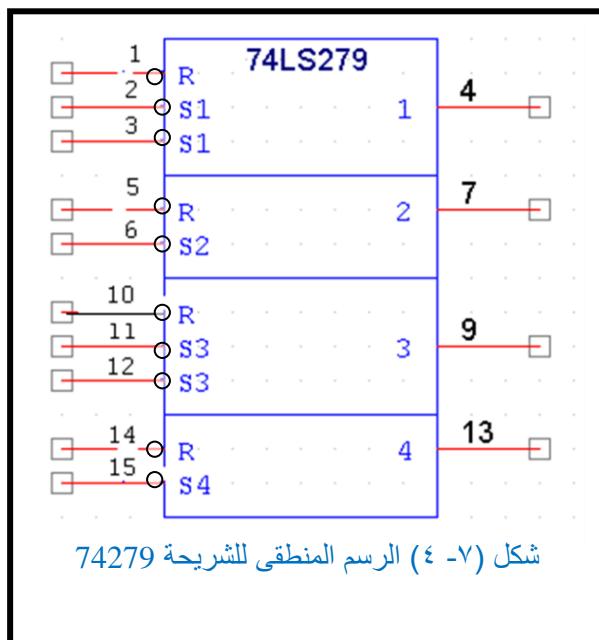

| ١١٨ | ٤ ماسك RS                                   | 74279 |

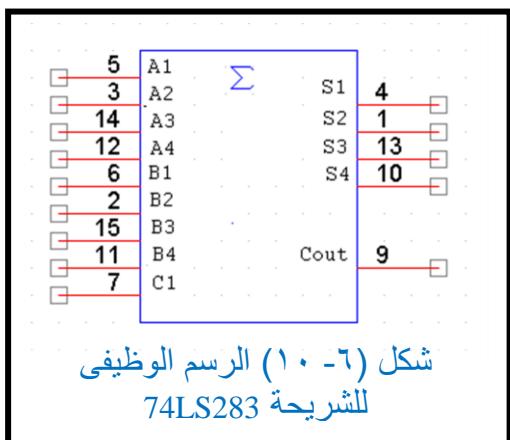

| ١٠٧ | مجموع كامل adder بحمل سريع                  | 74283 |

| ١٥١ | عداد عشرى                                   | 74290 |

| ١٥٢ | عداد ثنائى ٤ بت توجى                        | 74293 |

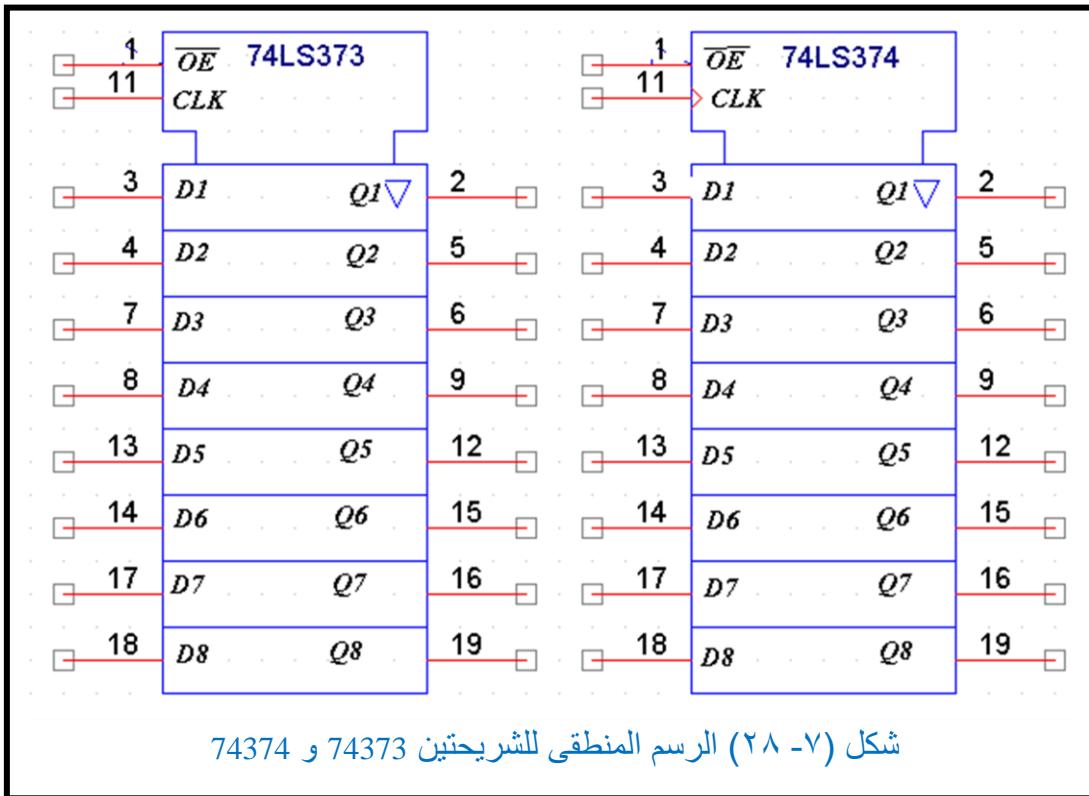

| ١٣٠ | ٨ قلابات D ، خرج ثلاثي المنطق               | 74373 |

| ١٣٠ | ٨ قلابات D ، خرج ثلاثي المنطق               | 74374 |

| ١٥٣ | ٢ عداد عشرى توجى                            | 74390 |

| ١٥٣ | ٢ عداد ثنائى توجى                           | 74393 |

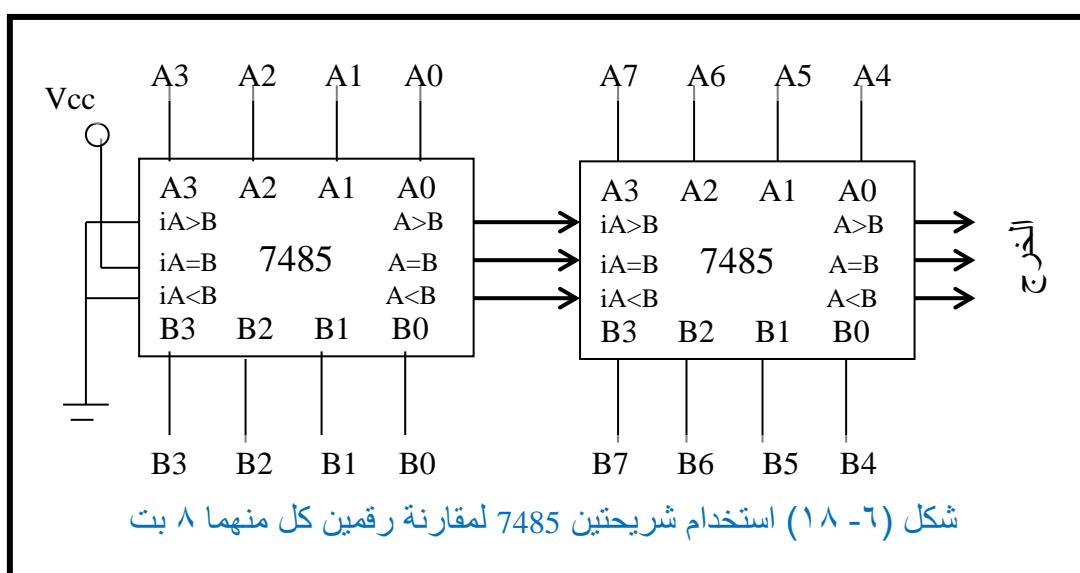

| ١١٢ | مقارن ٨ بت                                  | 74682 |

| ١١٢ | مقارن ٨ بت                                  | 74684 |

| ١١٢ | مقارن ٨ بت                                  | 74688 |

| ١٩٨ | دائرة توقيت                                 | 555   |

| ٢٠٧ | دائرة توقيت                                 | 556   |

|     |                                       |        |

|-----|---------------------------------------|--------|

| ٢٠٩ | دائرة توقيت                           | 558    |

| ٢٠٩ | دائرة توقيت                           | 559    |

| ٢٠٥ | دائرة توقيت ، مع عداد ، قابلة للبرمجة | 2240   |

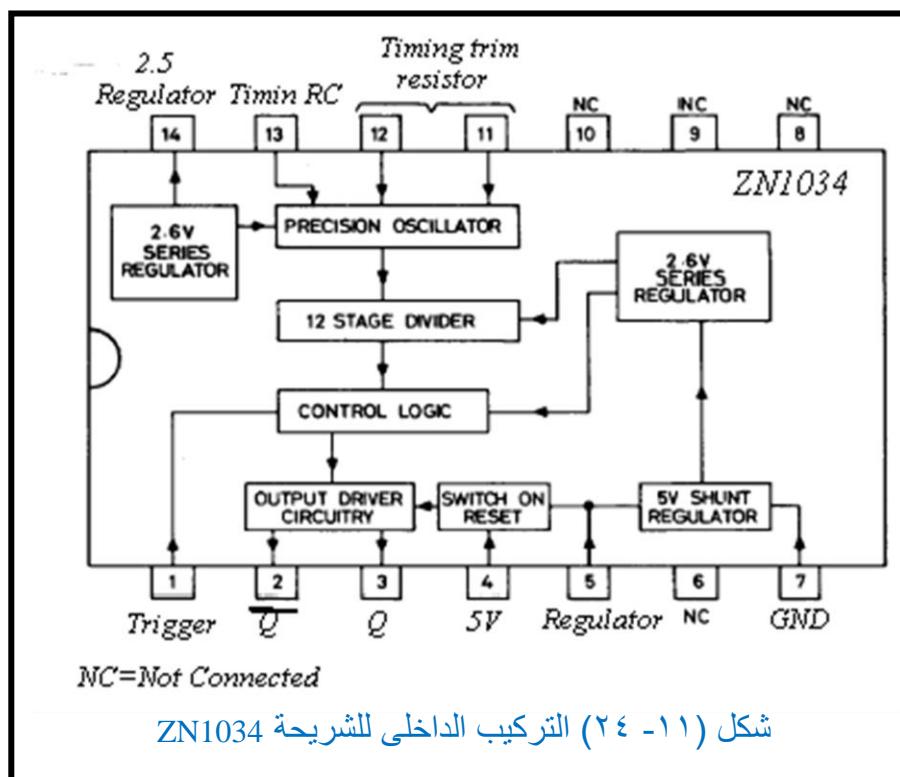

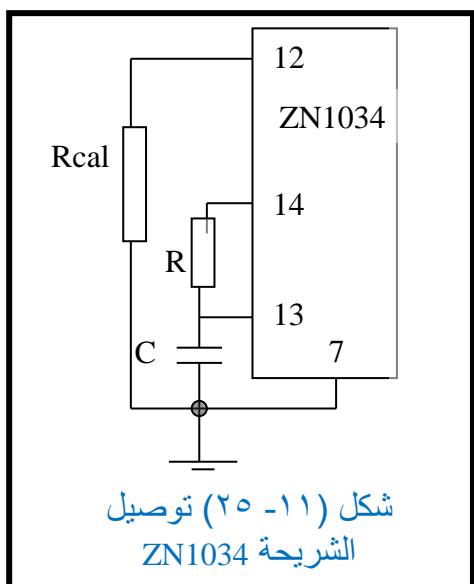

| ٢١١ | دائرة توقيت ، مع عداد                 | ZN1034 |

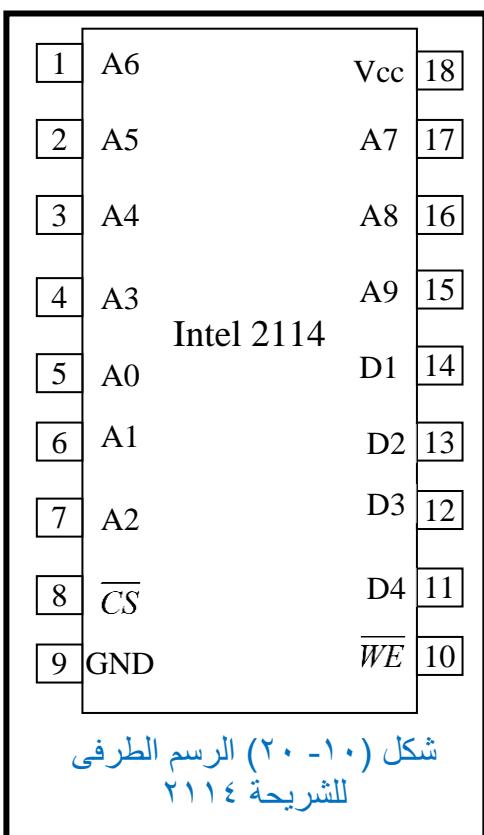

| ١٨٨ | ذاكرة قراءة وكتابة RAM ٤ كيلو×٤ بت    | 2114   |

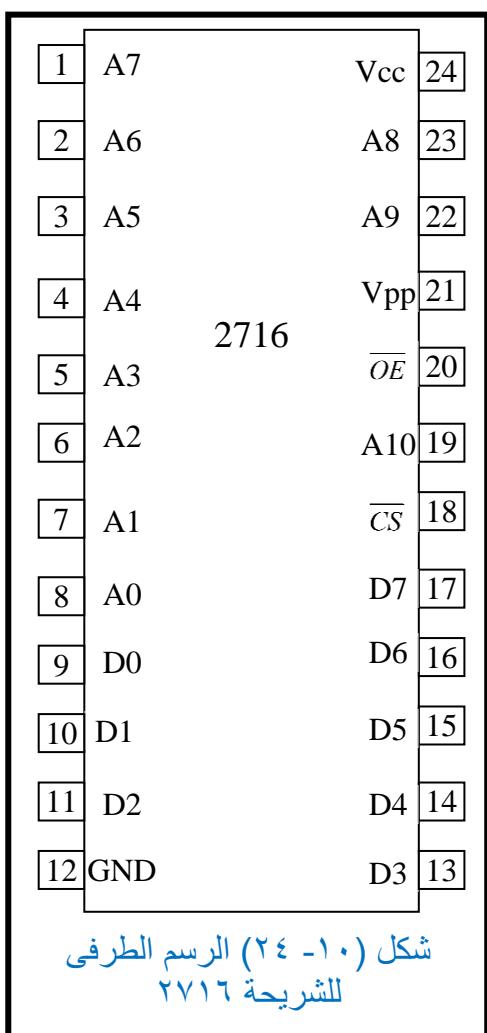

| ١٩٠ | ذاكرة قراءة فقط ROM ٢ كيلوبايت        | 2716   |

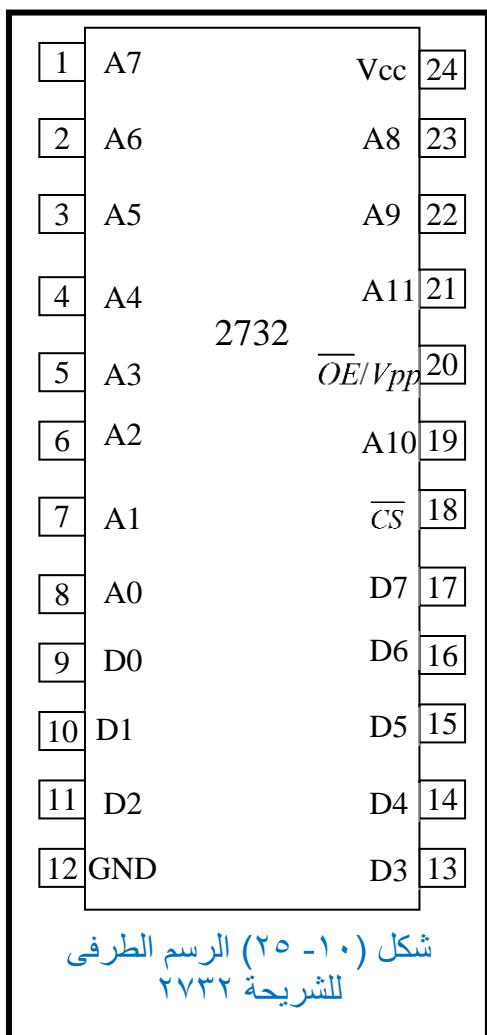

| ١٩١ | ذاكرة قراءة فقط ROM ٤ كيلوبايت        | 2732   |

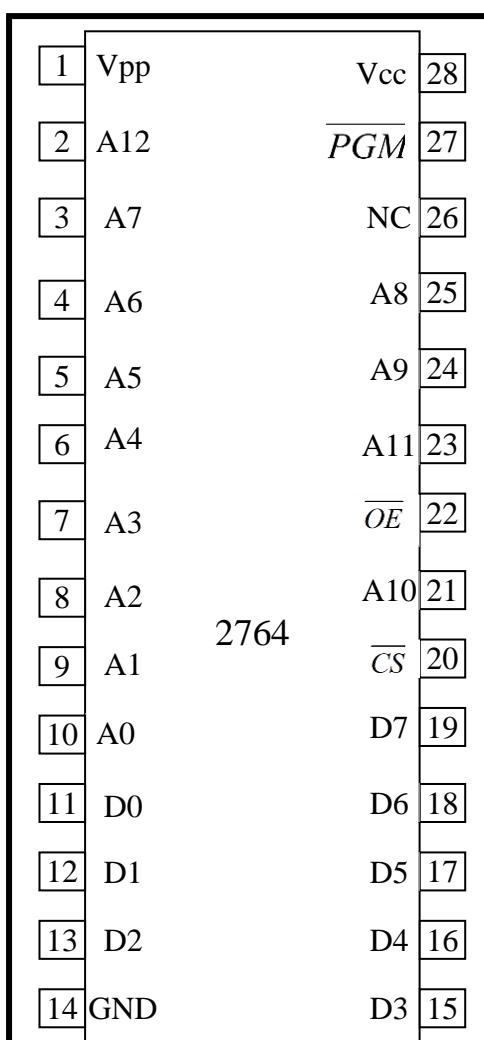

| ١٩١ | ذاكرة قراءة فقط ROM ٨ كيلوبايت        | 2764   |

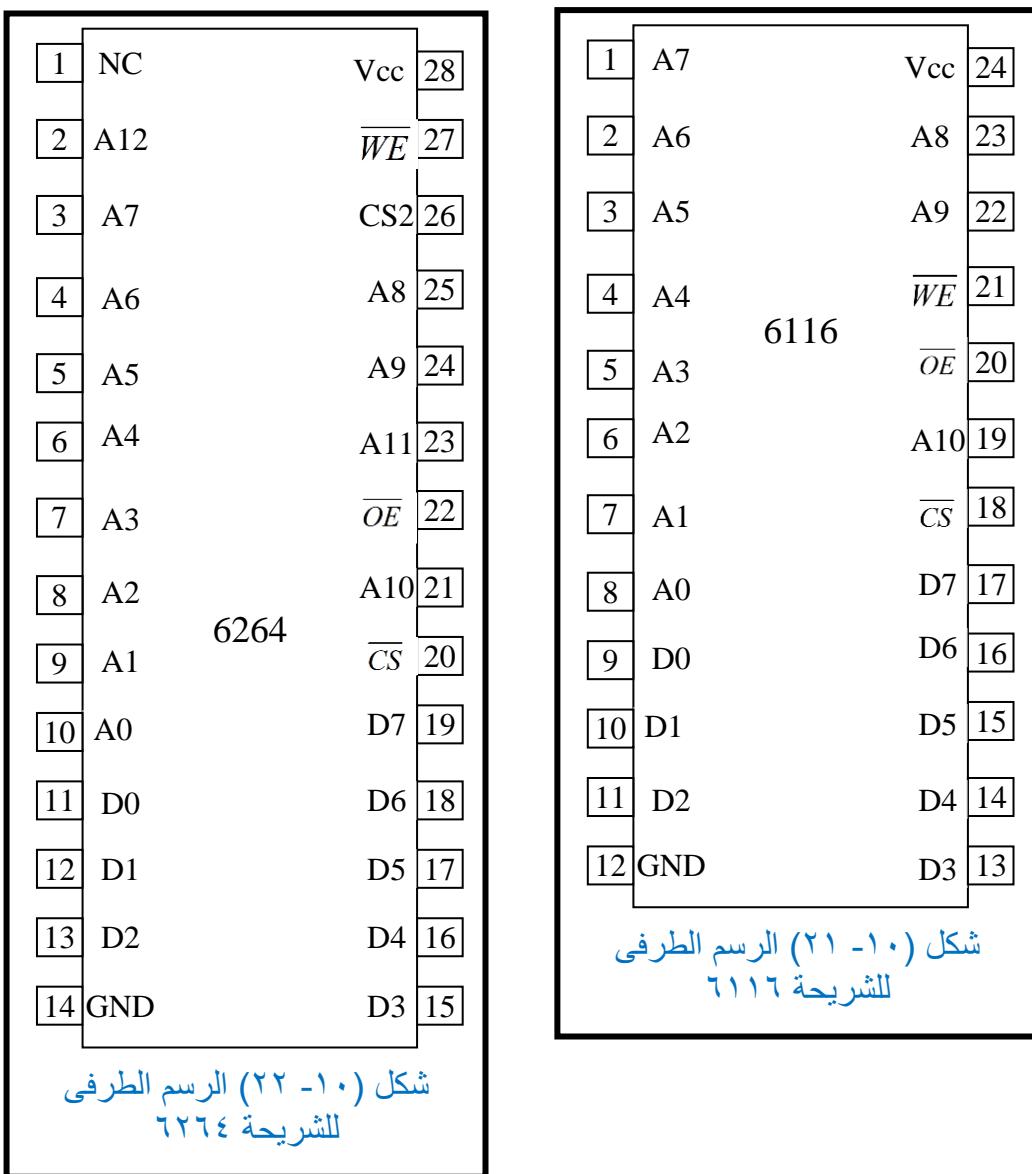

| ١٨٨ | ذاكرة قراءة وكتابة RAM ٢ كيلوبايت     | 6116   |

| ١٨٨ | ذاكرة قراءة وكتابة RAM ٨ كيلوبايت     | 6264   |

| ١٩١ | ذاكرة قراءة فقط ROM ٣٢ كيلوبايت       | 27256  |

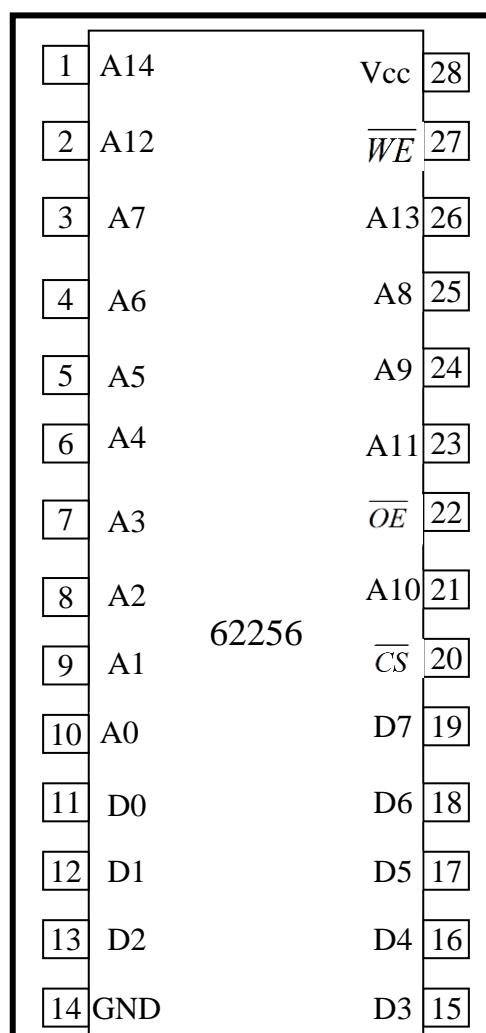

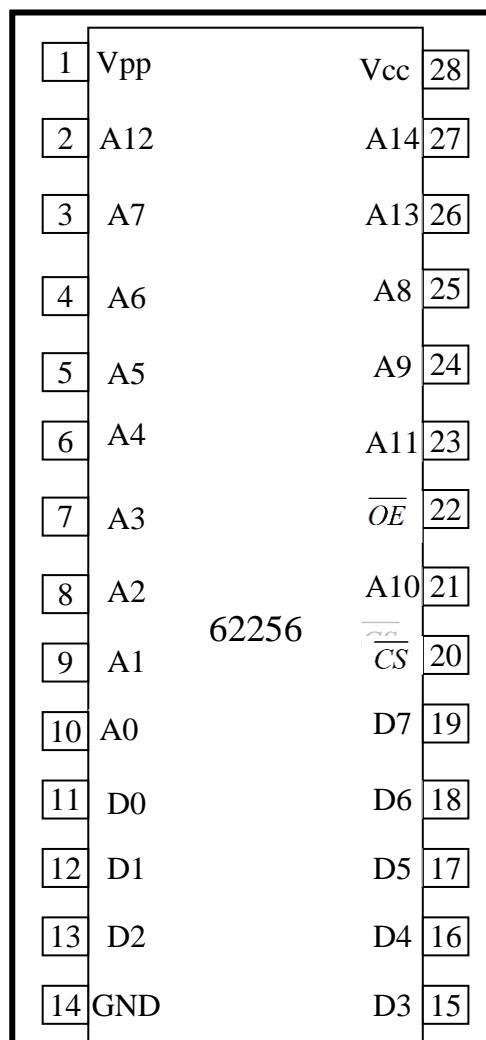

| ١٨٩ | ذاكرة قراءة وكتابة RAM ٣٢ كيلوبايت    | 62256  |

## المحتويات

[الإهداء](#)

[عرض الكتاب](#)

[جدول الشرائح الموجودة في هذا الكتاب](#)

### الفصل الأول: أساسيات عامة

|    |                                                                                      |

|----|--------------------------------------------------------------------------------------|

| ١  | <a href="#">١-١ مقدمة</a>                                                            |

| ٢  | <a href="#">٢-١ المقاومات الكهربائية</a>                                             |

| ٢  | <a href="#">٣-١ المكثفات</a>                                                         |

| ٨  |                                                                                      |

| ٩  | <a href="#">٤-١ الدوائر التكاملية</a>                                                |

| ١٣ | <a href="#">٥-١ الإشارات الانسياقية والإشارات الرقمية</a> Analog and digital signals |

| ١٤ | <a href="#">٦-١ الأجهزة المستخدمة لاختبار الدوائر الرقمية</a>                        |

| ١٧ | <a href="#">٧-١ تمارين</a>                                                           |

### الفصل الثاني: أنظمة العد Numbering systems

|    |                                                                                      |

|----|--------------------------------------------------------------------------------------|

| ١٩ | <a href="#">١-٢ مقدمة</a>                                                            |

| ٢٠ | <a href="#">٢-٢ النظام العشري Decimal system</a>                                     |

| ٢٠ | <a href="#">٣-٢ نظام العد الثنائي Binary system</a>                                  |

| ٢١ |                                                                                      |

| ٢٦ | <a href="#">٤-٢ المتتم الأحادي والمتمم الثنائي</a> Ones and twos complement          |

| ٢٧ | <a href="#">٥-٢ الأرقام السالبة والأرقام الموجبة في النظام الثنائي</a>               |

| ٢٧ | <a href="#">- نظام مقدار الإشارة Sign magnitude</a>                                  |

| ٢٧ | <a href="#">- نظام المتتم الأحادي</a>                                                |

| ٢٨ | <a href="#">- نظام المتتم الثنائي</a>                                                |

| ٢٩ | <a href="#">٦-٢ العمليات الحسابية على الأعداد ذات الإشارة</a>                        |

| ٢٩ | <a href="#">- أولاً: عملية الجمع</a>                                                 |

| ٣٠ | <a href="#">- خطأ الفيضان Over flow error</a>                                        |

| ٣١ | <a href="#">- ثانياً: عملية الطرح</a>                                                |

| ٣١ | <a href="#">٧-٢ النظام الثمانى Octal system</a>                                      |

| ٣٣ | <a href="#">٨-٢ النظام الستعشرى Hexadecimal system</a>                               |

| ٣٤ | <a href="#">٩-٢ الأرقام العشرية المكونة ثنائيا Binary Coded Decimal Numbers, BCD</a> |

| ٣٦ | <a href="#">١٠-٢ تمارين</a>                                                          |

|    |                                                         |

|----|---------------------------------------------------------|

| ٣٨ | <b>الفصل الثالث: البوابات المنطقية Logic gates</b>      |

| ٣٩ | ١-٣ مقدمة                                               |

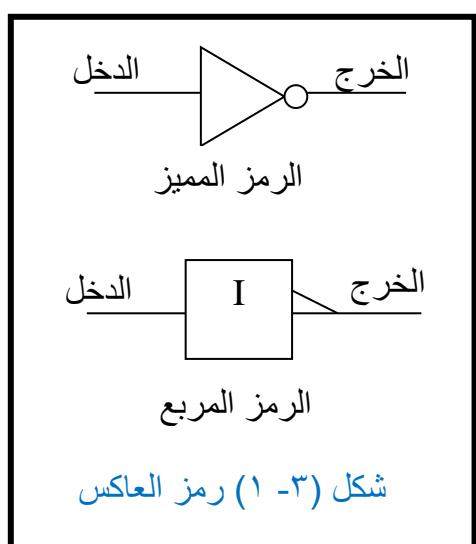

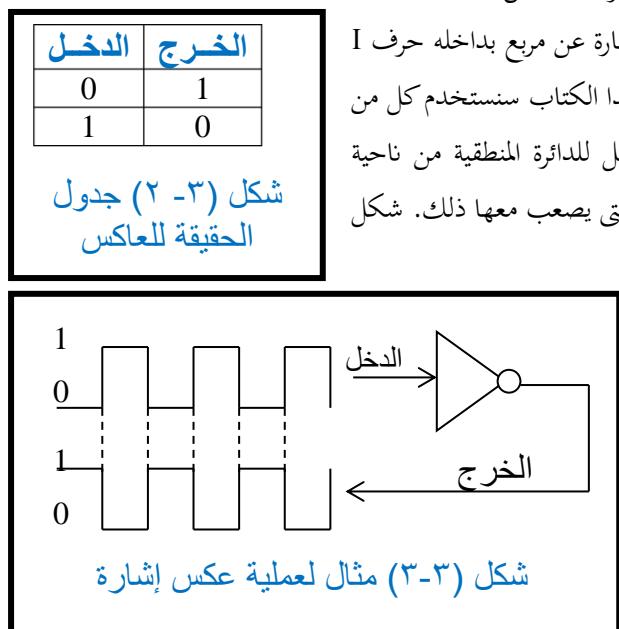

| ٣٩ | ٢-٣ بوابة النفي Not gate                                |

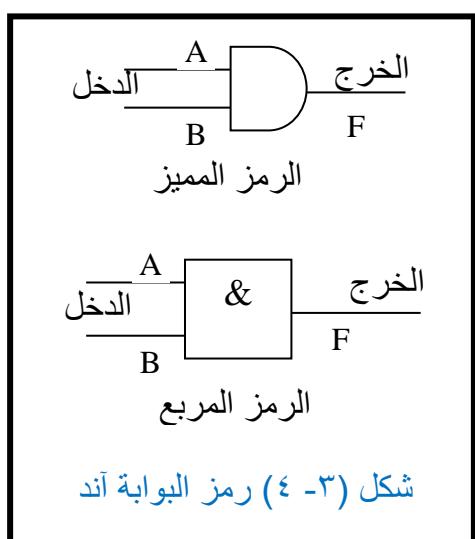

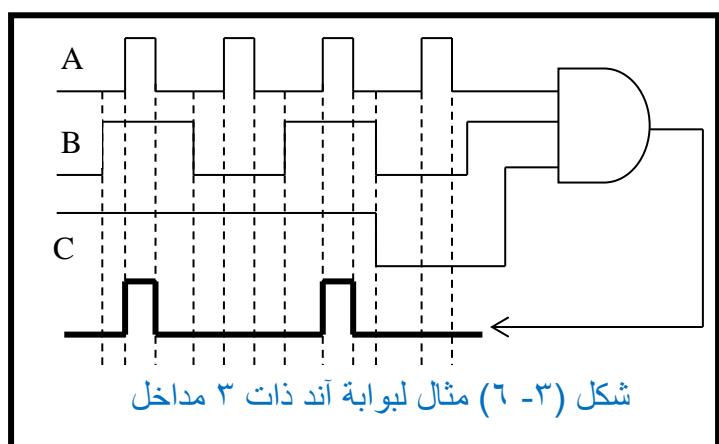

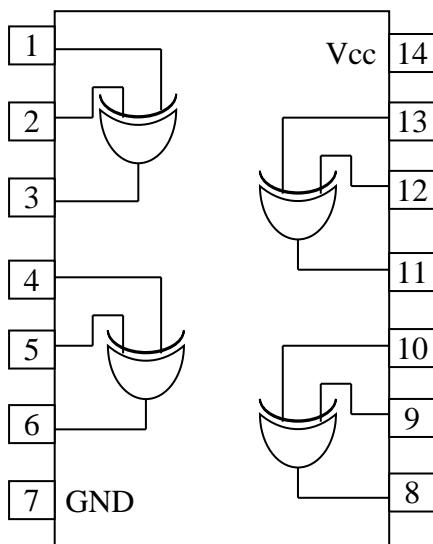

| ٤٠ | ٣-٣ البوابة آند AND gate                                |

| ٤١ | ٤-٣ البوابة أور OR gate                                 |

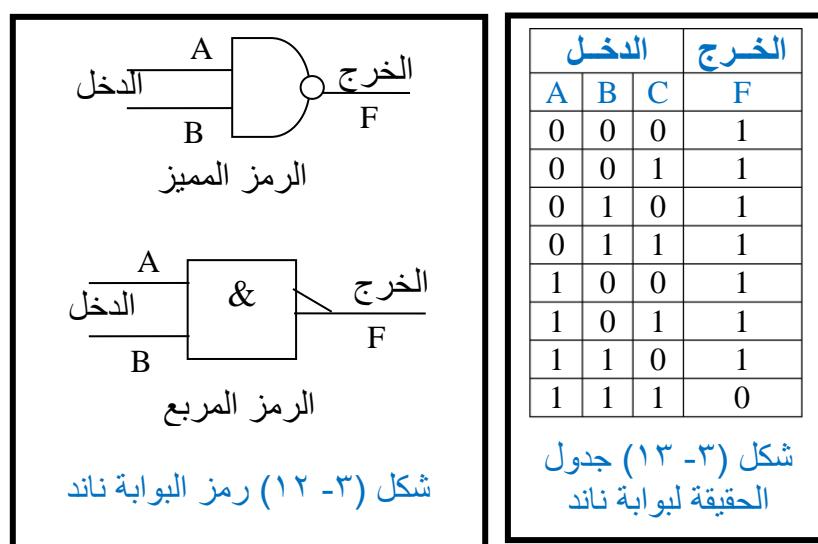

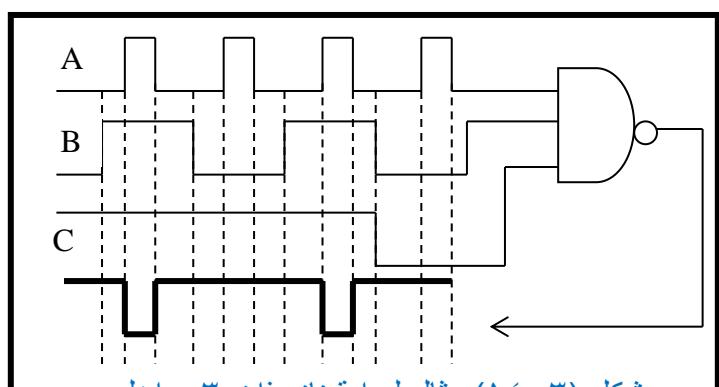

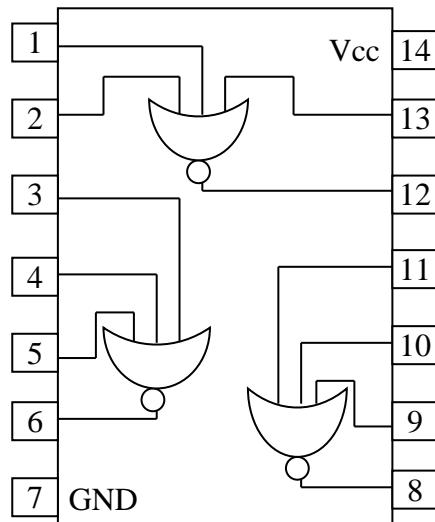

| ٤٢ | ٥-٣ البوابة ناند NAND gate                              |

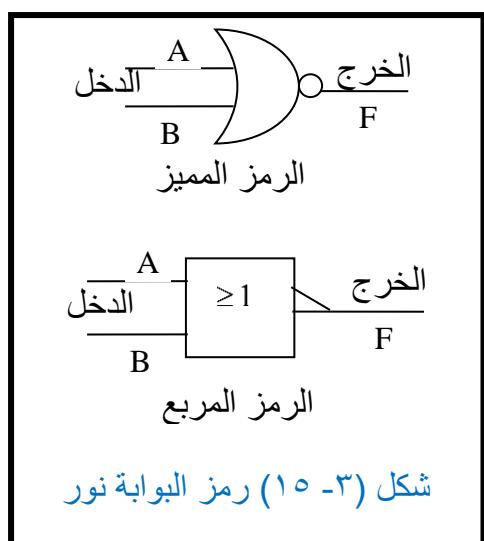

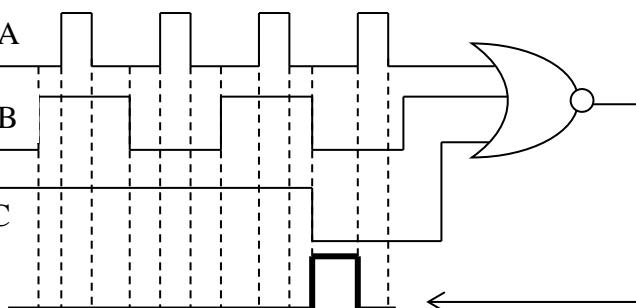

| ٤٣ | ٦-٣ البوابة نور NOR gate                                |

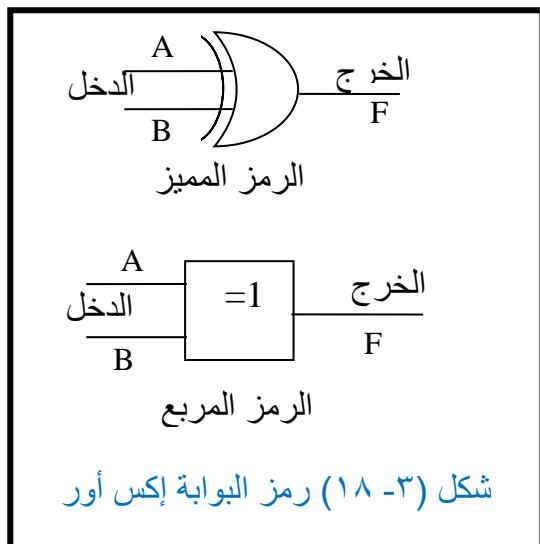

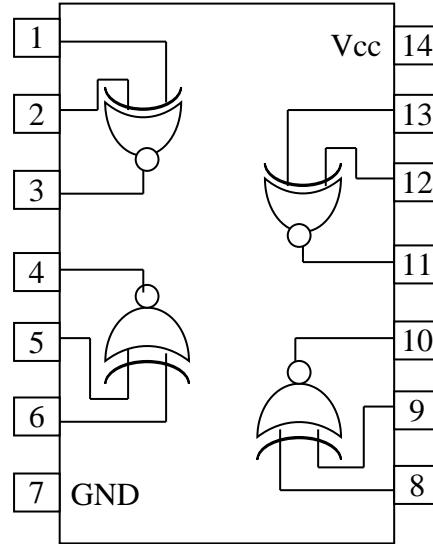

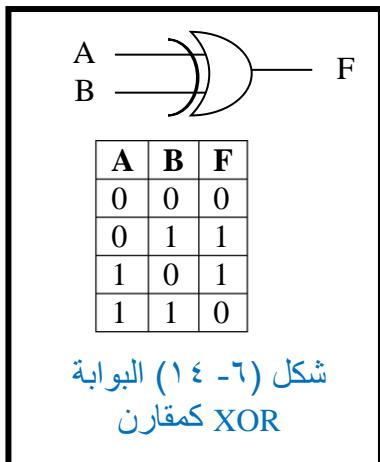

| ٤٤ | ٧-٣ البوابة إكس أور XOR gate                            |

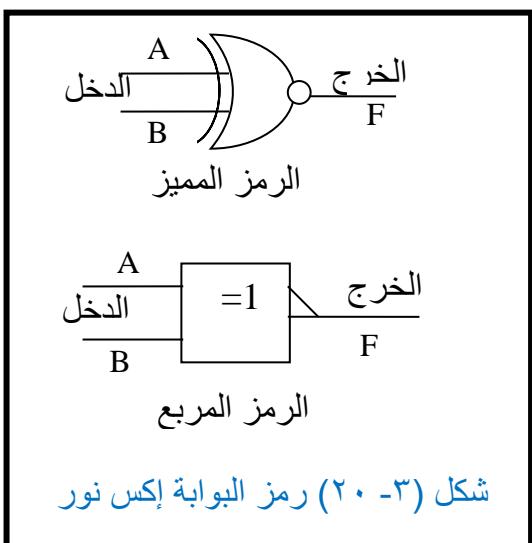

| ٤٤ | ٨-٣ البوابة إكس نور XNOR gate                           |

| ٤٥ | ٩-٣ شرائح العكس Inverter chips                          |

| ٤٦ | ١٠-٣ شرائح الآند AND gate chips                         |

| ٤٨ | ١١-٣ شرائح الأور OR gate chips                          |

| ٤٨ | ١٢-٣ شرائح الناند NAND gate chips                       |

| ٥١ | ١٣-٣ شرائح النور NOR gate chips                         |

| ٥٢ | ١٤-٣ شرائح الإكس أور والإكس نور XOR and XNOR gate chips |

| ٥٢ | ١٥-٣ تمارين                                             |

**الفصل الرابع: الجبر البوليني وتبسيط المعادلات المنطقية**

|    |                                                            |

|----|------------------------------------------------------------|

| ٥٤ | ٤ مقدمة                                                    |

| ٥٥ | ٤-٤ العمليات والتعبيرات المنطقية                           |

| ٥٥ | ٤-٣ قوانين الجبر المنطقي أو البوليني                       |

| ٥٦ | ٤-٤ نظريات ديمورجان Demorgans theorems                     |

| ٥٨ | ٤-٥ الحصول على المعادلة المنطقية لأى دائرة منطقية          |

| ٥٩ | ٤-٦ الحصول على جدول الحقيقة من المعادلة المنطقية           |

| ٥٩ | ٤-٧ تبسيط المعادلات المنطقية                               |

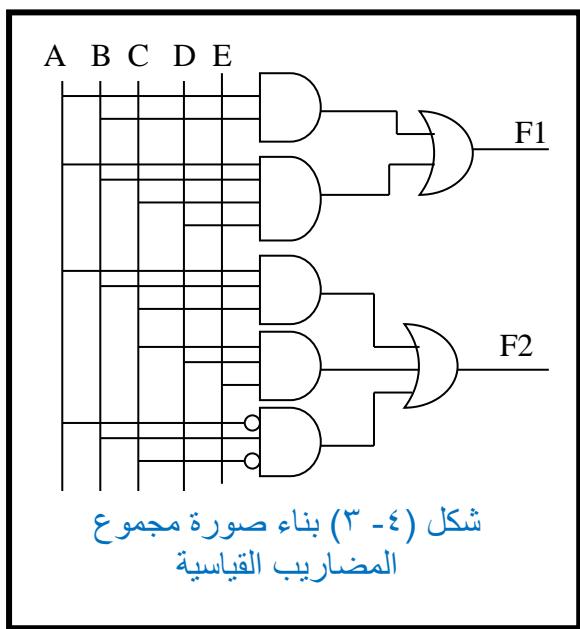

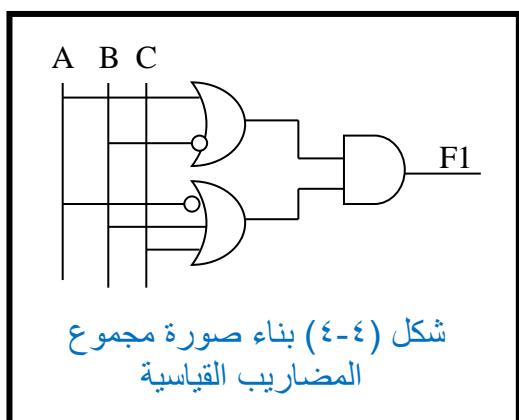

| ٦١ | ٤-٨ الصور القياسية للمعادلات المنطقية                      |

| ٦٣ | ٤-٩ جدول الحقيقة والمعادلات المنطقية                       |

| ٦٤ | ٤-١٠ الحصول على المعادلة المنطقية القياسية من جدول الحقيقة |

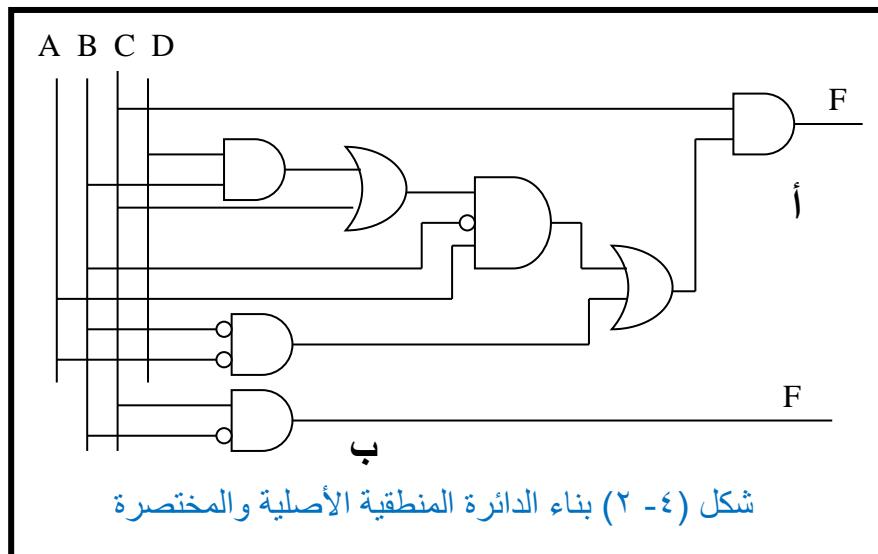

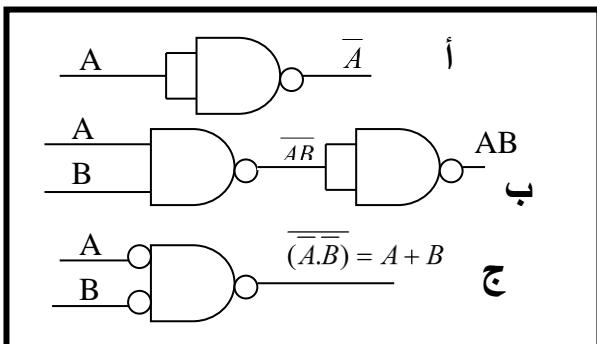

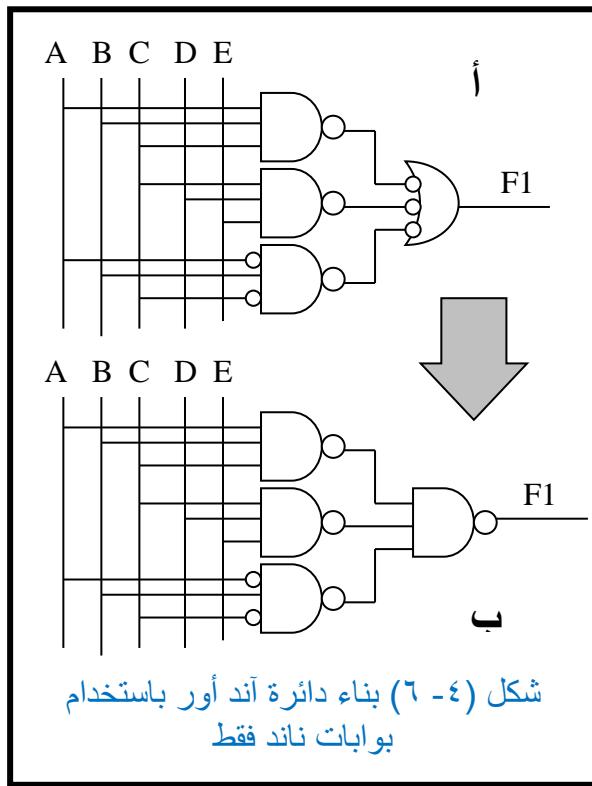

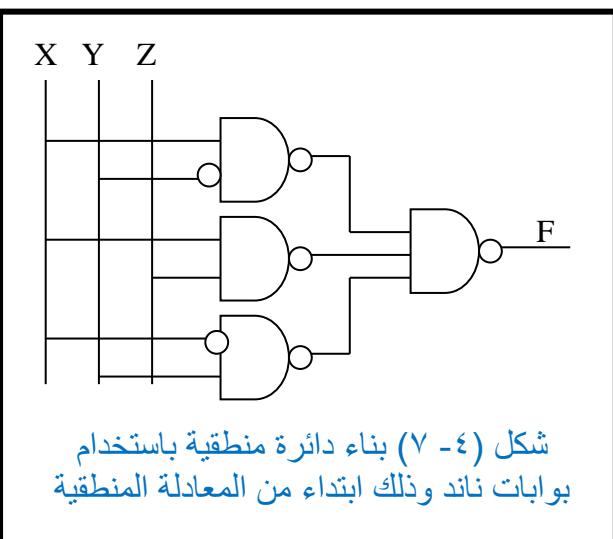

| ٦٥ | ٤-١١ بناء الدوائر المنطقية باستخدام بوابات ناند NAND فقط   |

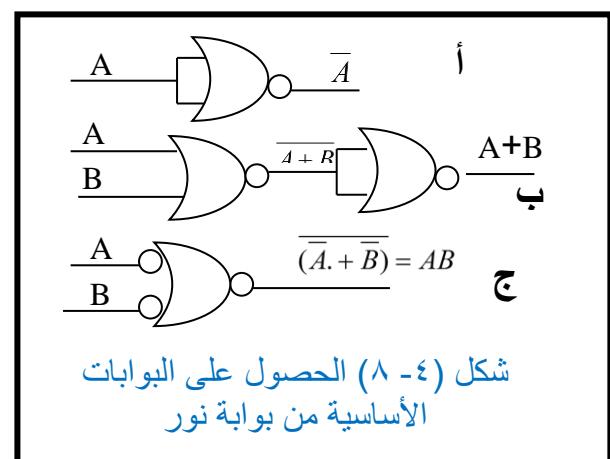

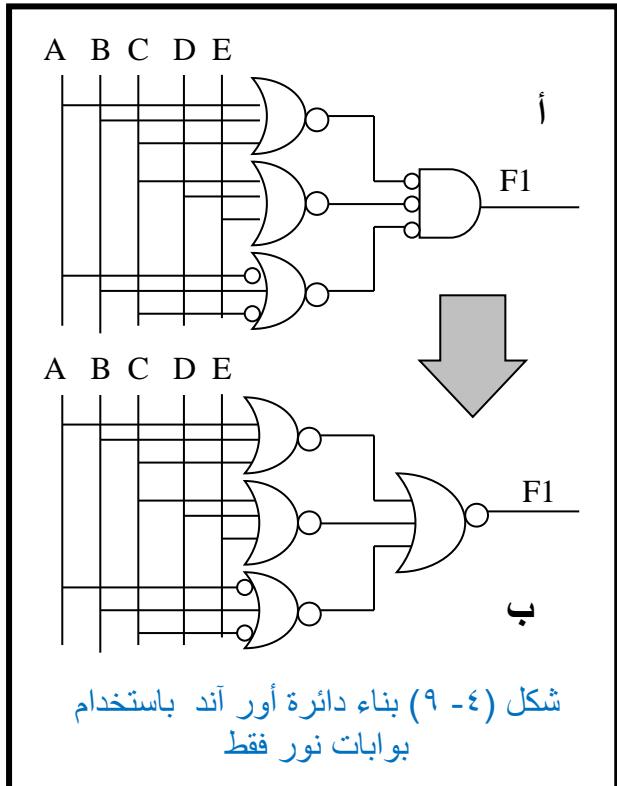

| ٦٦ | ٤-١٢ بناء الدوائر المنطقية باستخدام بوابات نور NOR فقط     |

| ٦٨ | ٤-١٣ اختصار الدوال المنطقية (خريطة كارنوف)                 |

٤-٤ تمارين

٧١

٧٣

**الفصل الخامس: محللات الشفرة والمشفرات**

٧٤

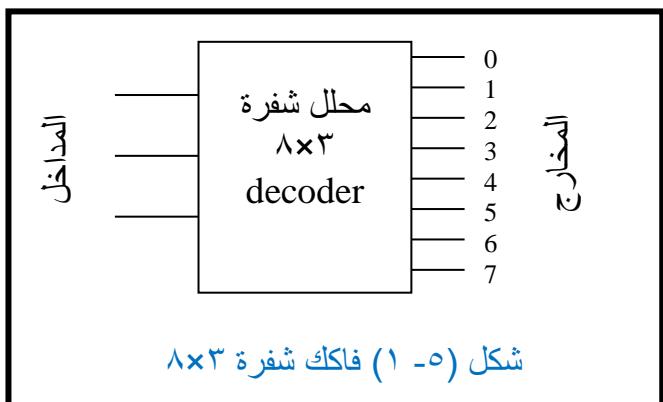

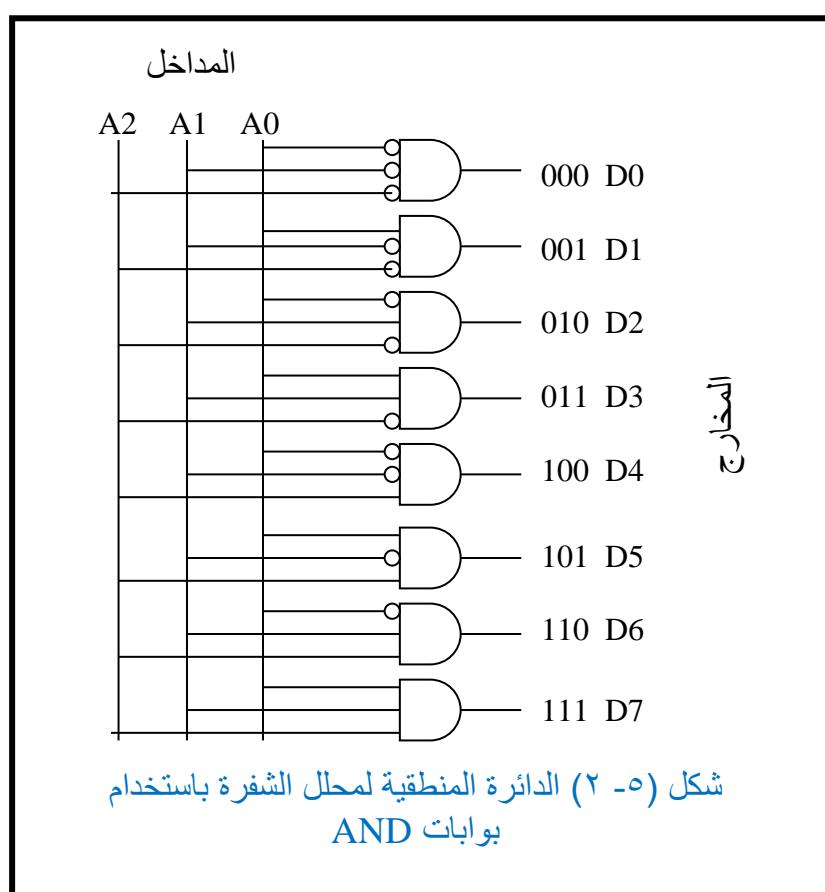

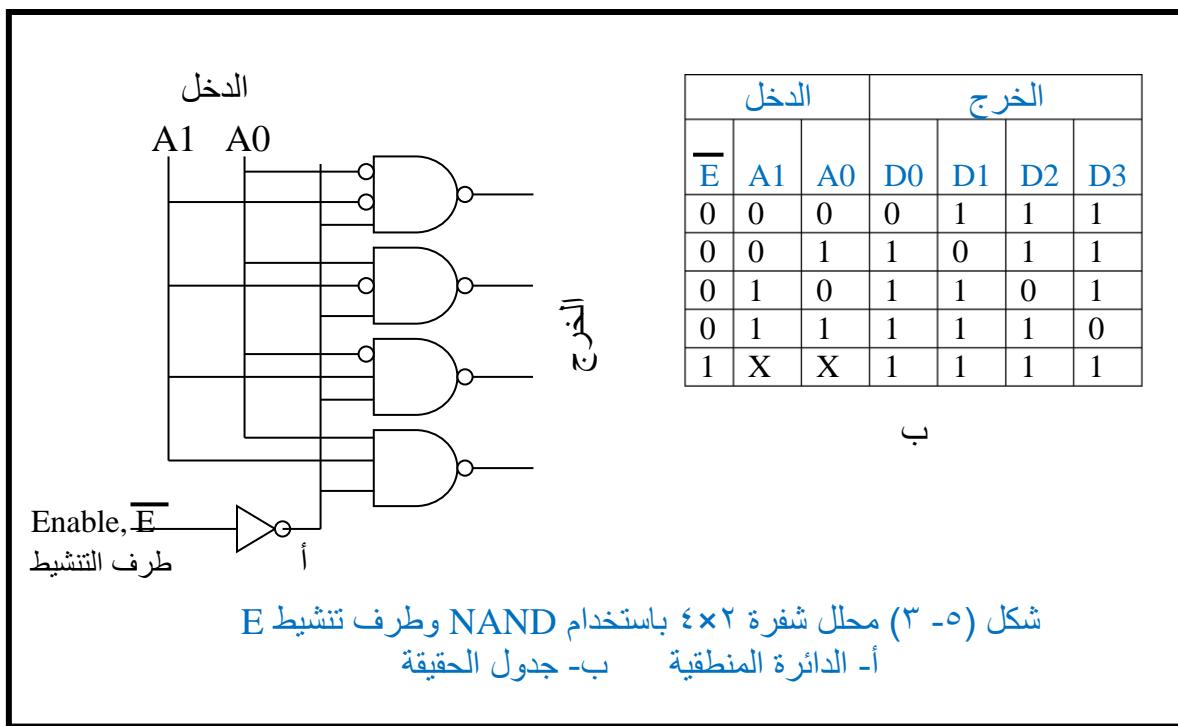

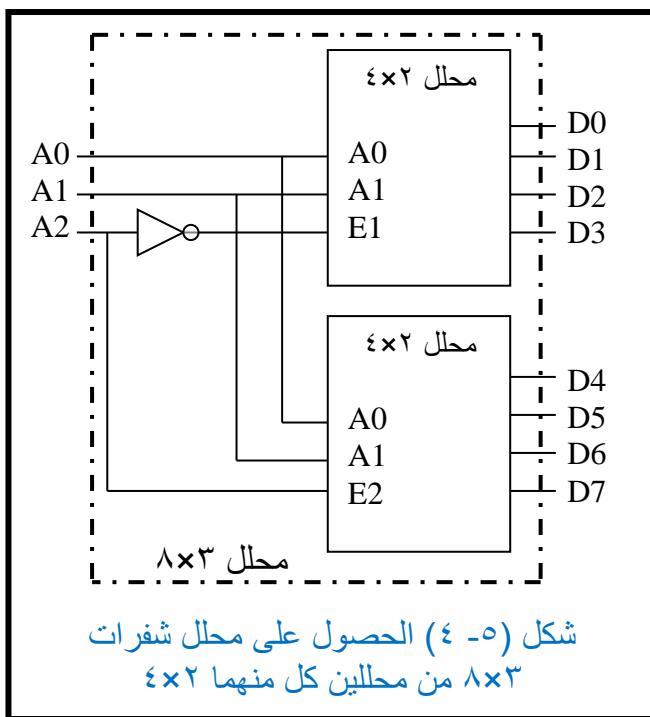

١-٥ محللات الشفرة Decoders

٧٧

٢-٥ الشرحقة ٧٤٤٤٢

٧٧

٣-٥ الشرحقة ٧٤٤٤٥

٧٨

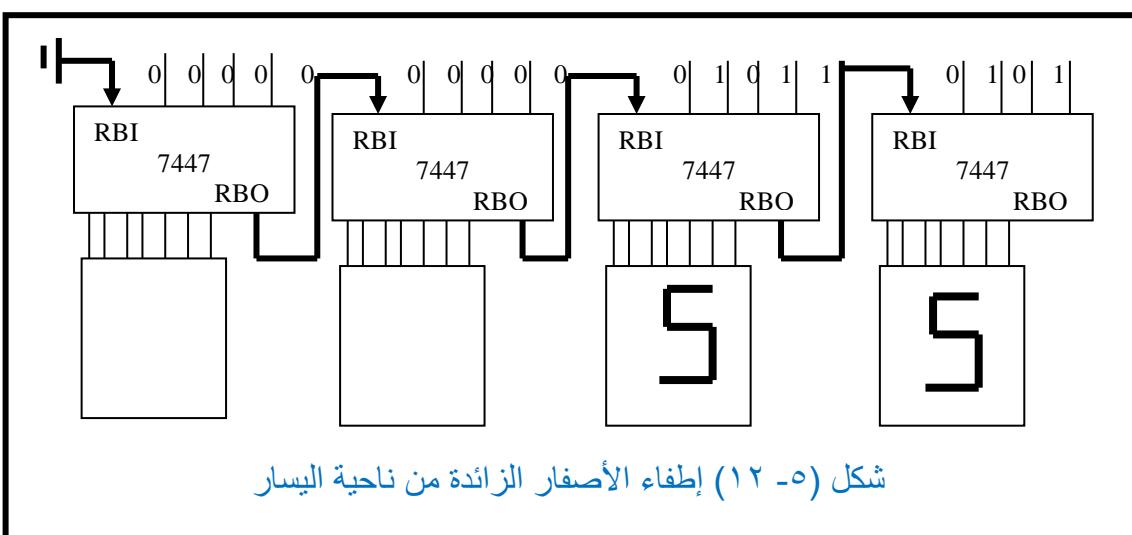

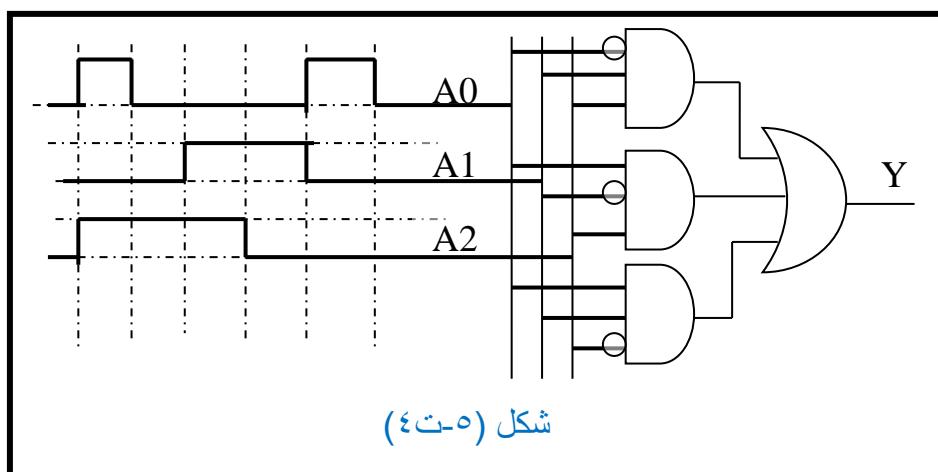

٤-٥ الشرائح ٧٤٤٤٦ و ٧٤٤٤٧ و ٧٤٤٤٨ و ٧٤٤٩

٨٢

٥-٥ الشرحقة ٧٤١٣٧

٨٣

٦-٥ الشرحقة ٧٤١٣٨

٨٤

٧-٥ الشرحقة ٧٤١٣٩

٨٥

٨-٥ الشرحقة ٧٤١٤٥

٨٦

٩-٥ الشرحقة ٧٤١٥٤

٨٦

١٠-٥ الشرحقة ٧٤١٥٥

٨٧

١١-٥ الشرحقة ٧٤١٥٦

٨٧

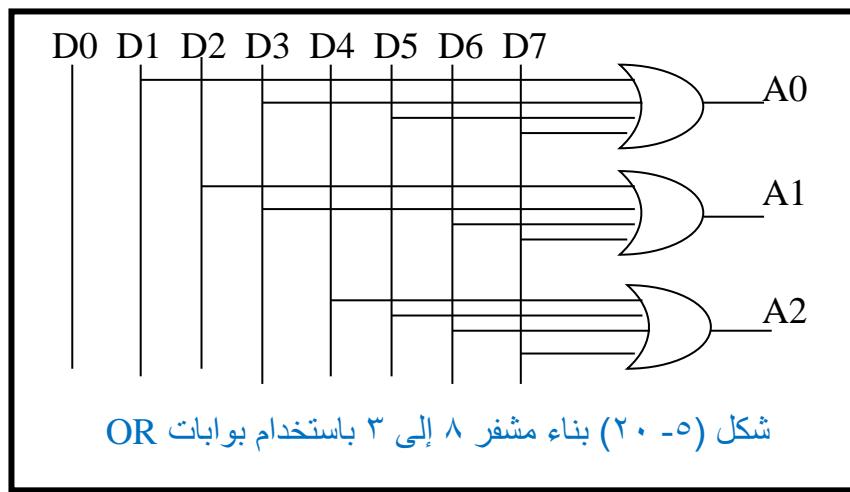

١٢-٥ المشفرات Encoders

٨٨

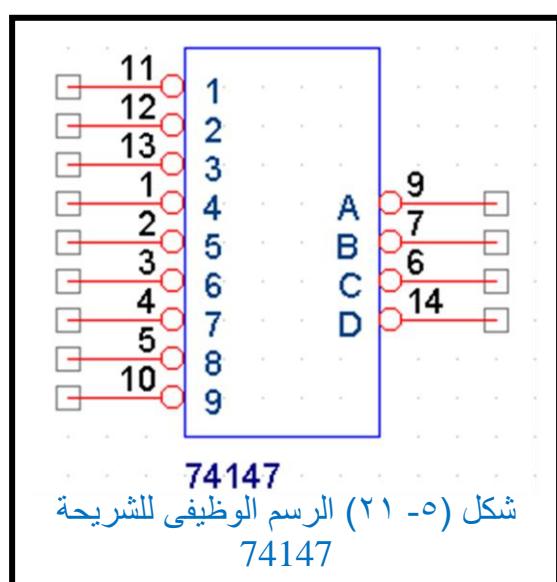

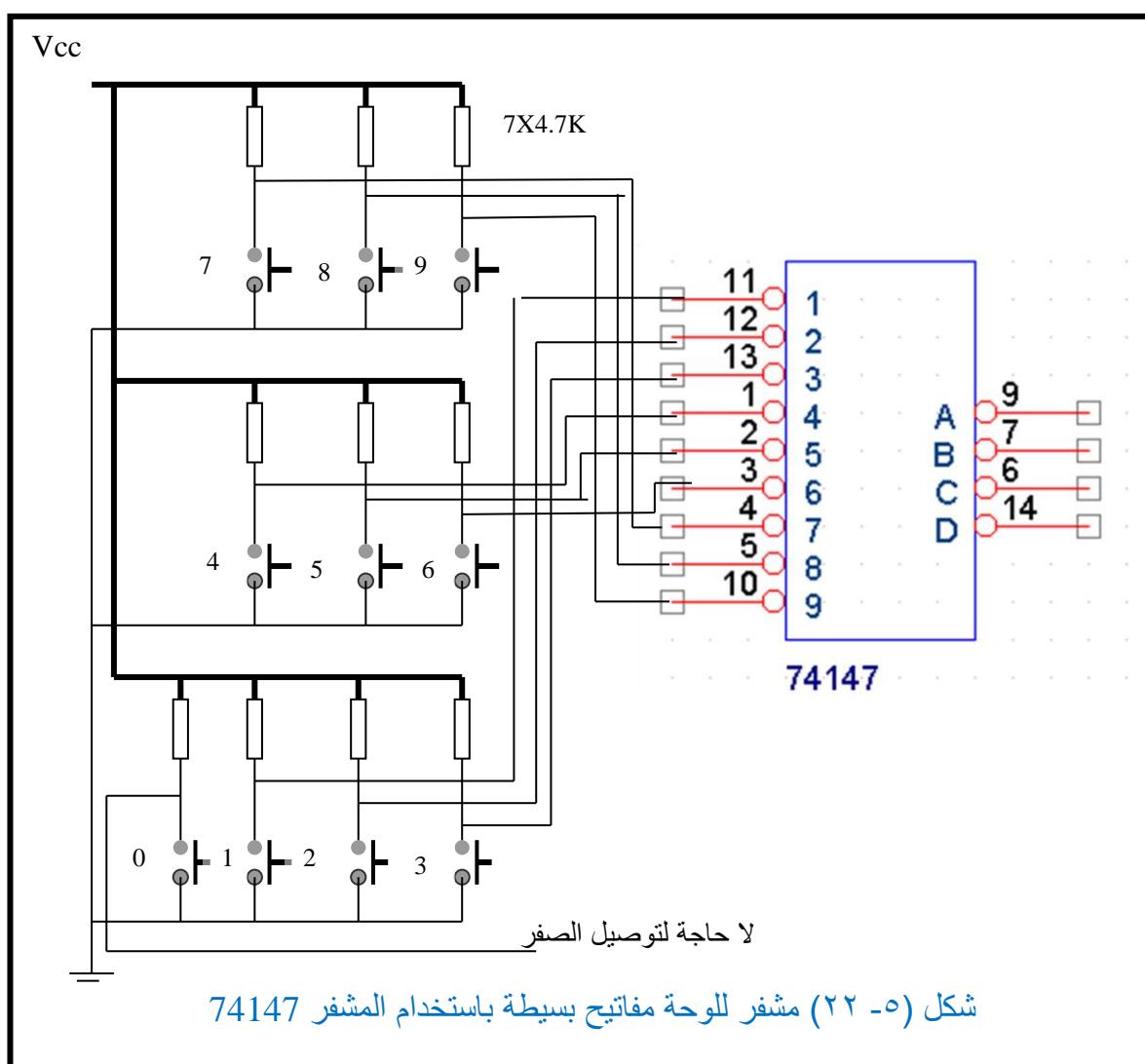

١٣-٥ الشرحقة ٧٤١٤٧

٩٠

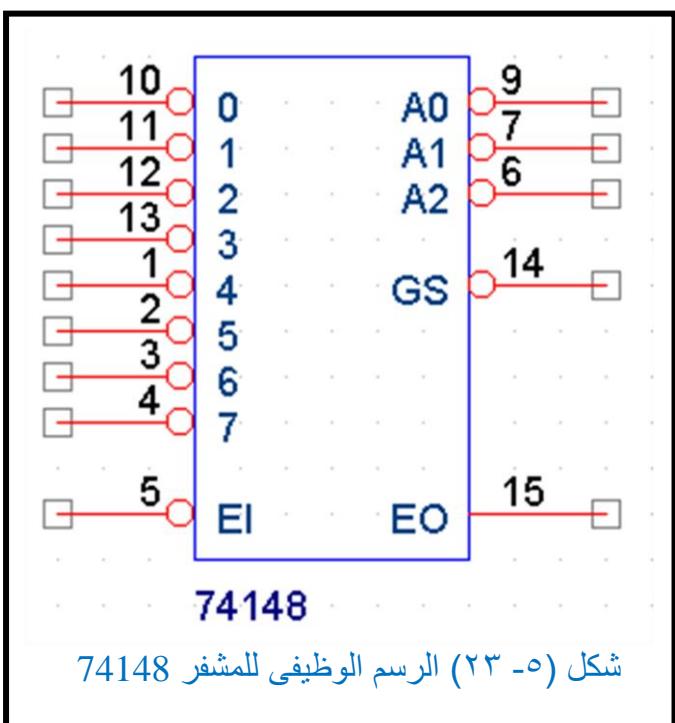

١٤-٥ الشرحقة ٧٤١٤٨

٩١

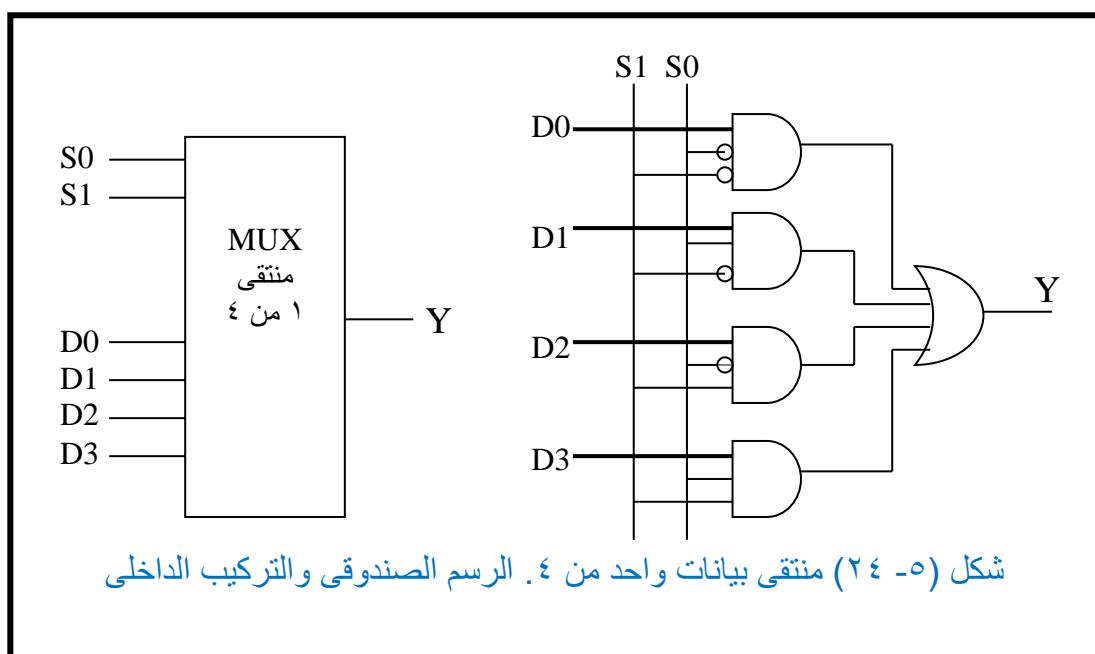

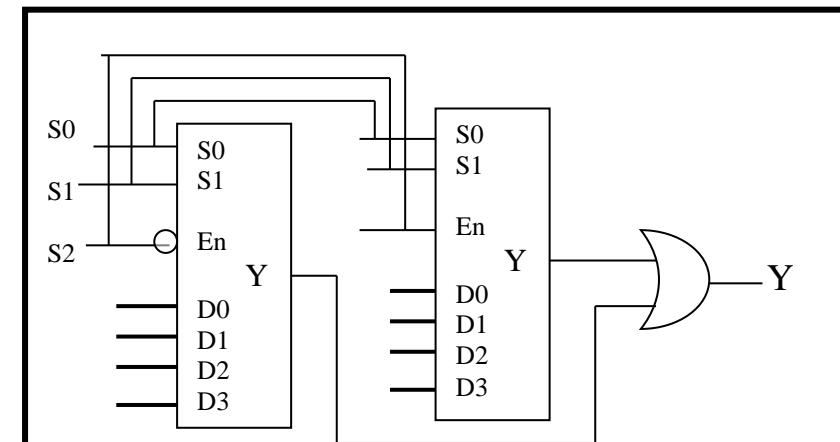

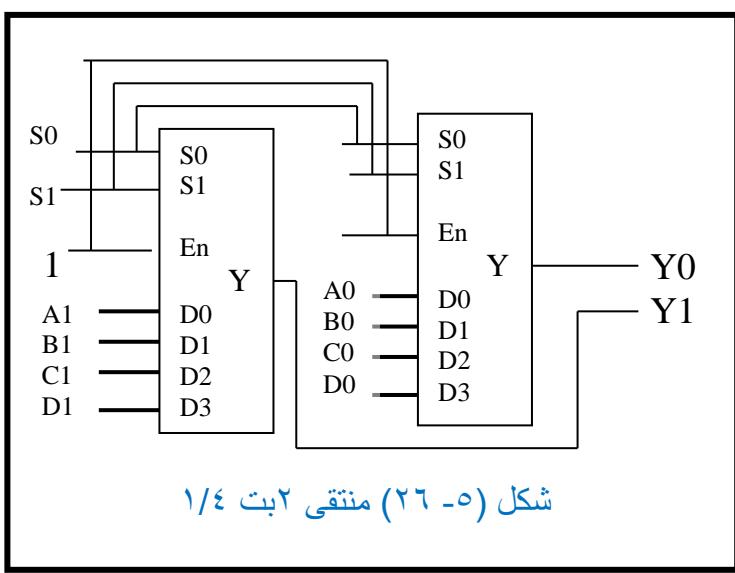

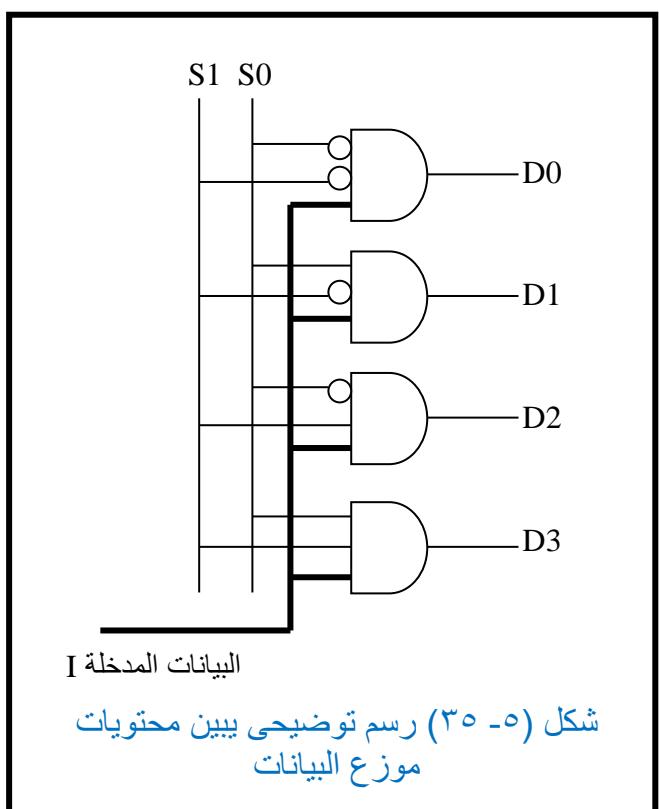

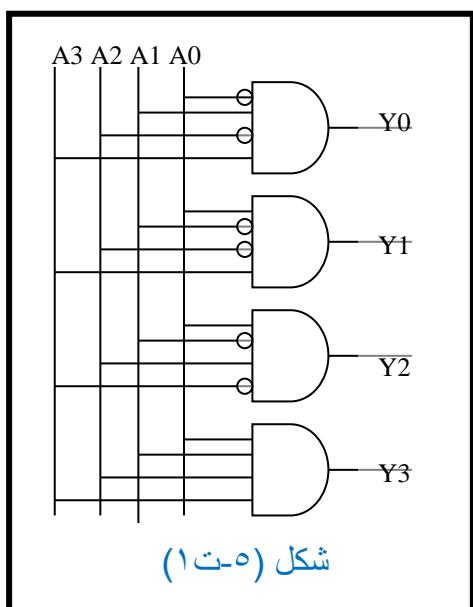

١٥-٥ منتقى البيانات Multiplexer

٩٣

١٦-٥ الشرحقة ٧٤١٥٠

٩٣

١٧-٥ الشرحقة ٧٤١٥١

٩٤

١٨-٥ الشرحقة ٧٤١٥٣

٩٥

١٩-٥ الشرائح ٧٤١٥٧ و ٧٤١٥٨

٩٦

٢٠-٥ الشرحقة ٧٤٢٥١

٩٧

٢١-٥ الشرحقة ٧٤٢٥٣

٩٧

٢٢-٥ الشرحقة ٧٤٢٥٨

٩٨

٢٣-٥ موزع البيانات Demultiplexer

٩٩

٢٤-٥ تمارين

١٠١

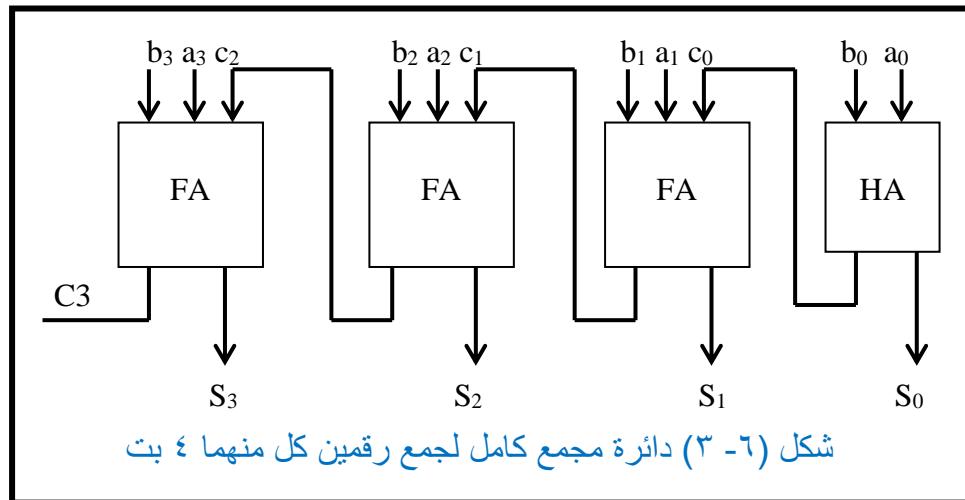

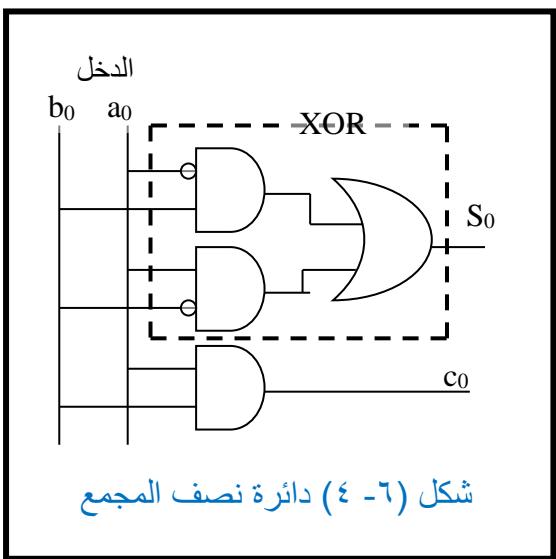

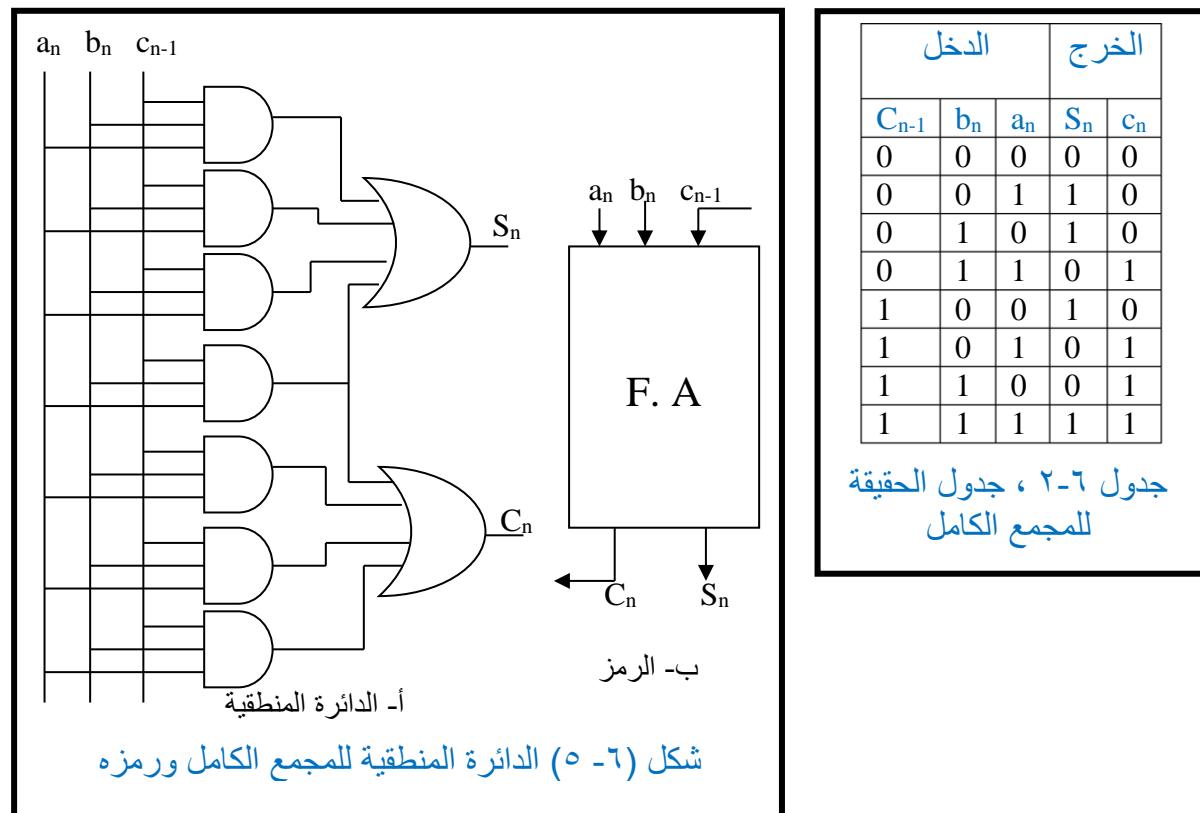

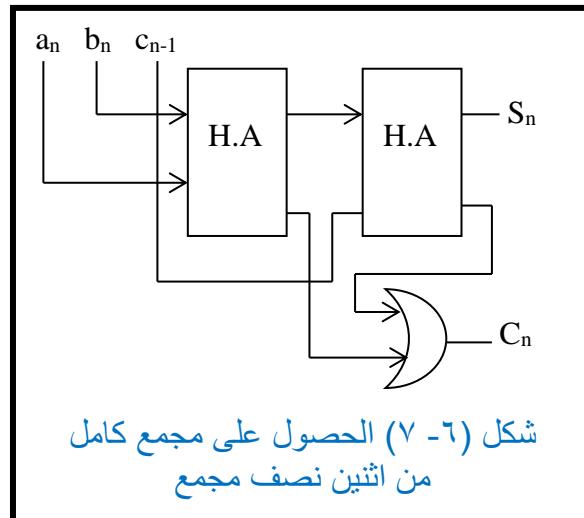

**الفصل السادس: دوائر الحساب Arithmetic circuits**

١٠٢

١-٦ مقدمة

١٠٢

٢-٦ دوائر الحساب

١٠٤

٣-٦ نصف الجمع Half adder

|     |                                             |

|-----|---------------------------------------------|

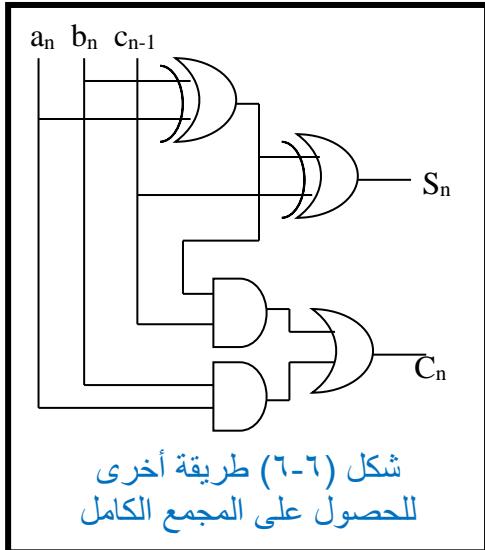

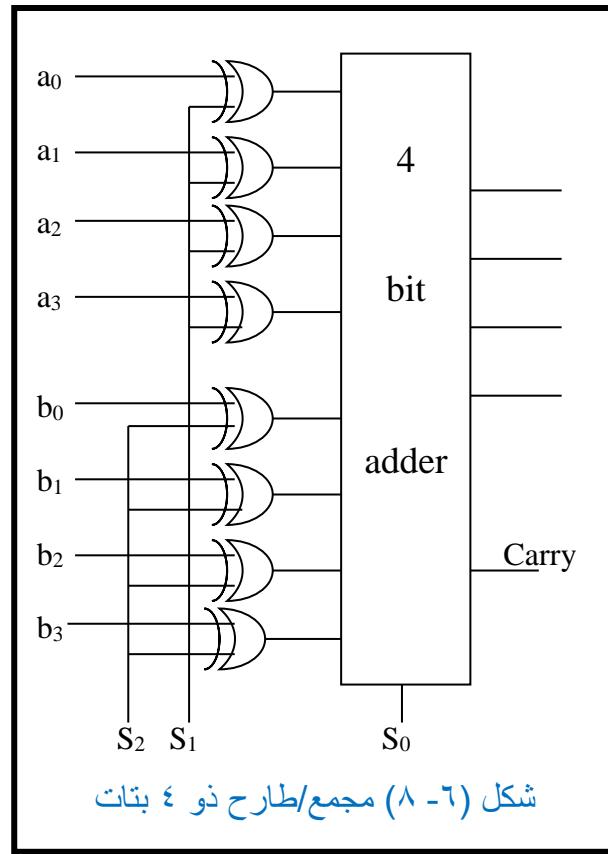

| ١٠٤ | ٦-٤ المجمع الكامل Full adder                |

| ١٠٥ | ٥-٦ الطرح الثنائي                           |

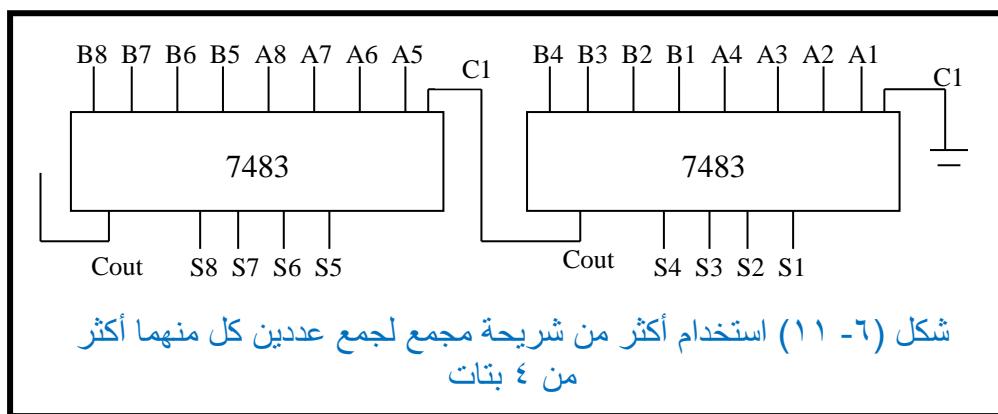

| ١٠٧ | ٦-٧ الشريحة ٧٤٨٣                            |

| ١٠٧ | ٧-٦ الشريحة ٧٤٢٨٣                           |

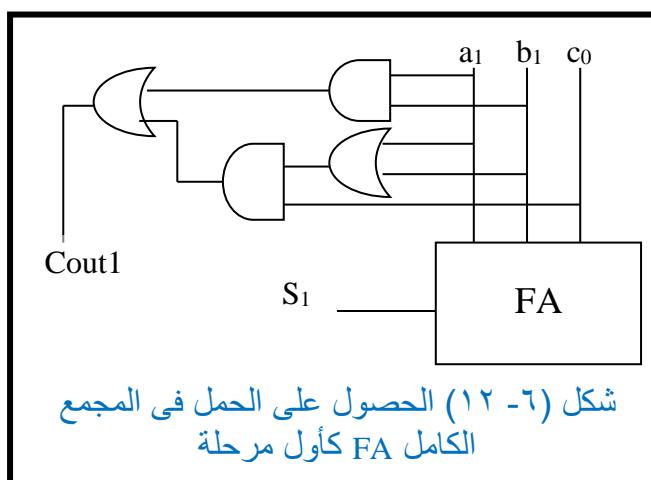

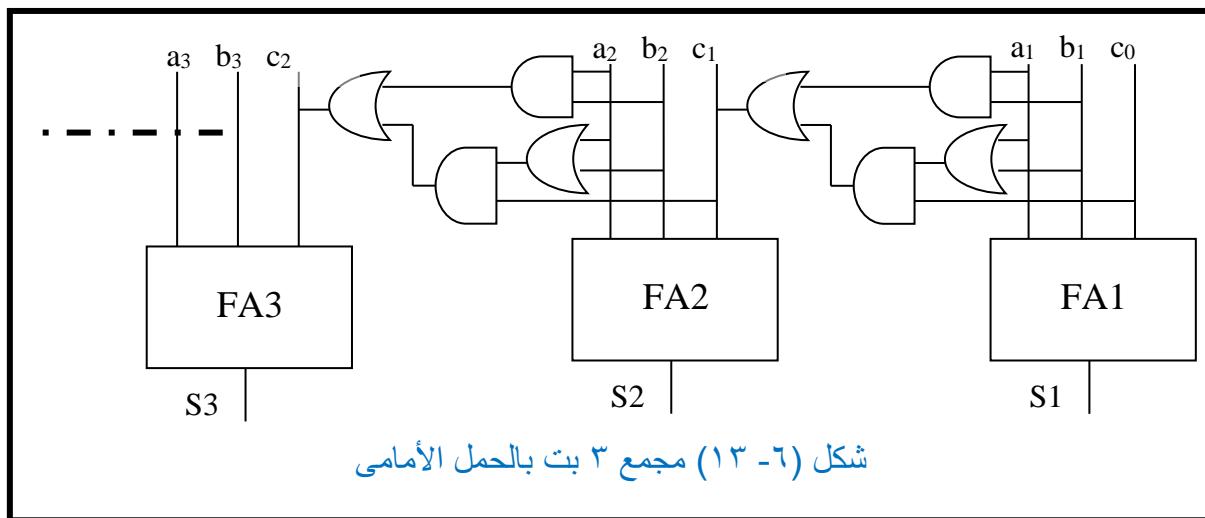

| ١٠٨ | ٦-٨ مجمع الحمل التموجي و مجمع الحمل الأمامي |

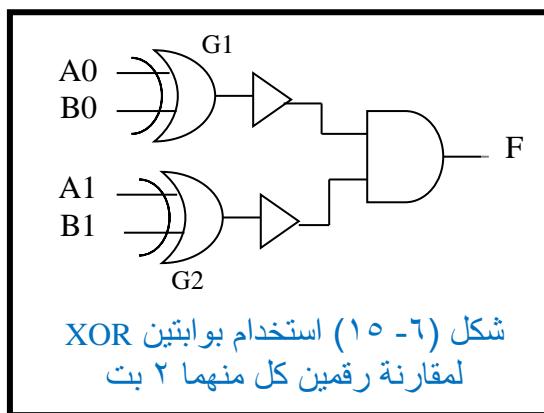

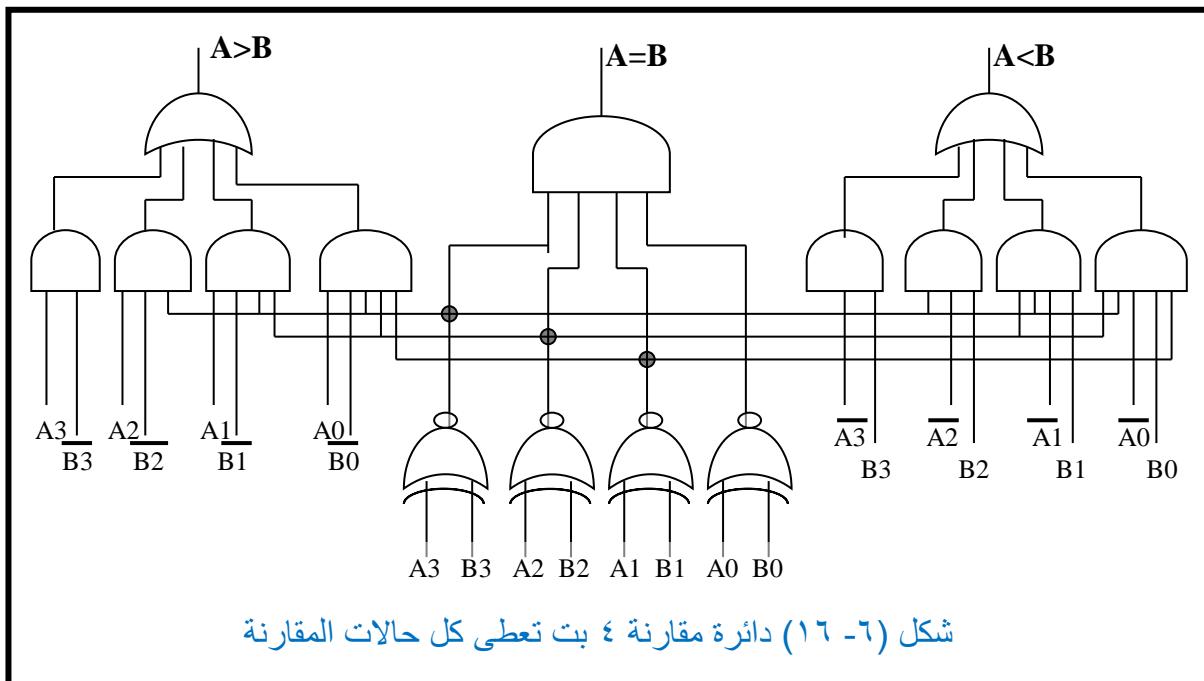

| ١٠٩ | ٩-٦ دوائر المقارنة                          |

| ١١١ | ٦-١٠ الشريحة ٧٤٨٥                           |

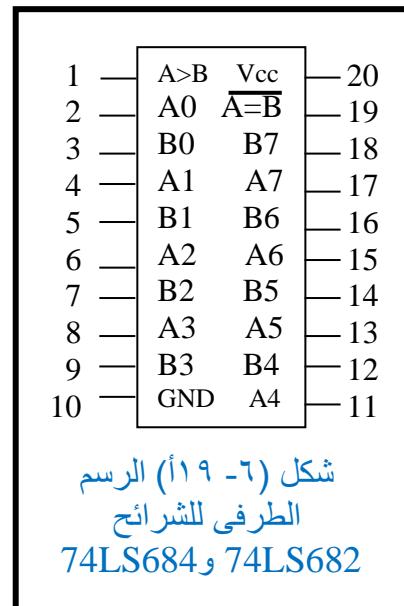

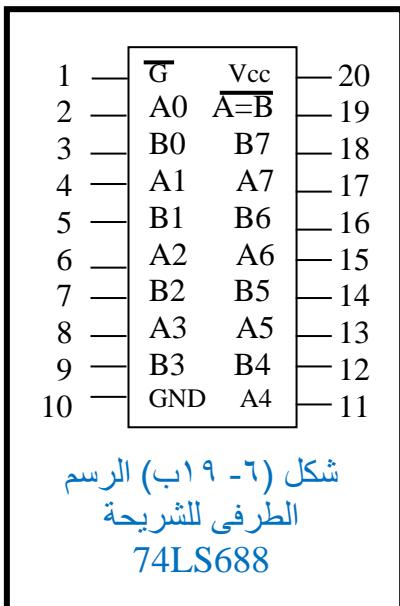

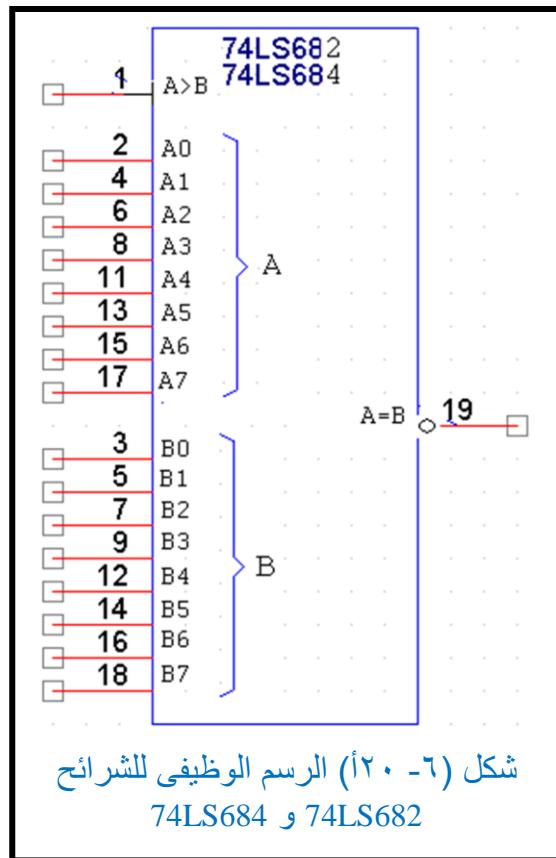

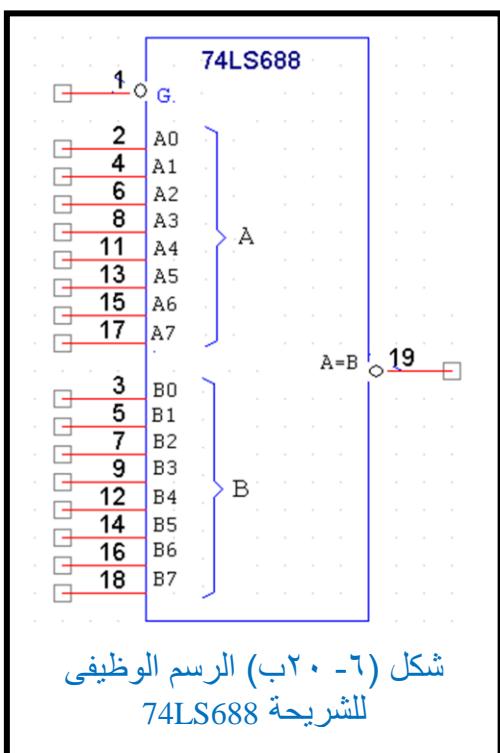

| ١١٢ | ٦-١١ الشريحة ٧٤٦٨٢ و ٧٤٦٨٤ و ٧٤٦٨٨          |

| ١١٣ | ٦-١٢ تمارين                                 |

**الفصل السابع: الماسكات والقلابات Latches and flip flops**

|     |                                                    |

|-----|----------------------------------------------------|

| ١١٥ | ١-٧ مقدمة                                          |

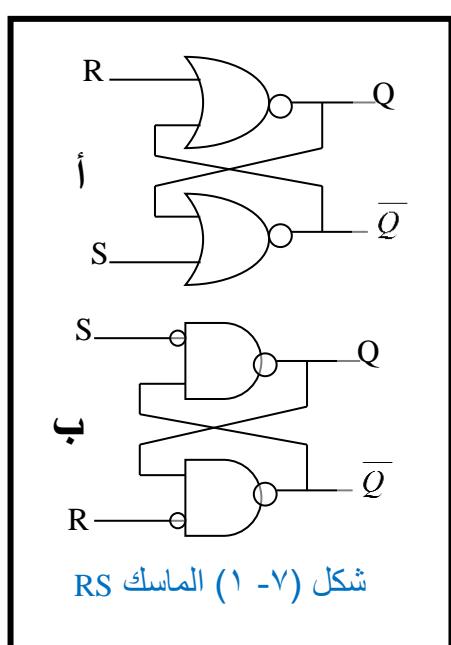

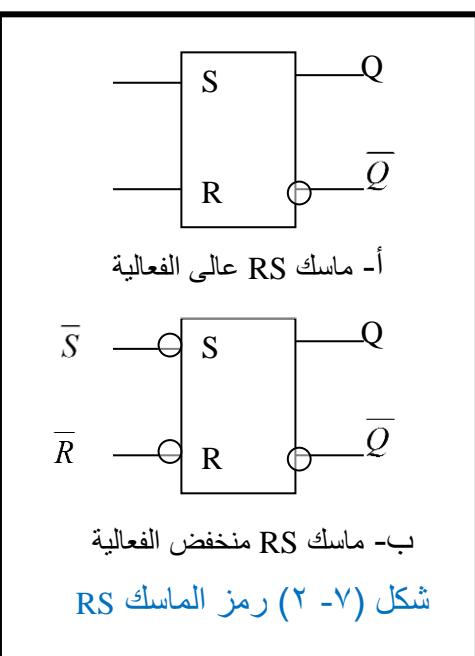

| ١١٦ | ٢-٧ الماسكات R-S                                   |

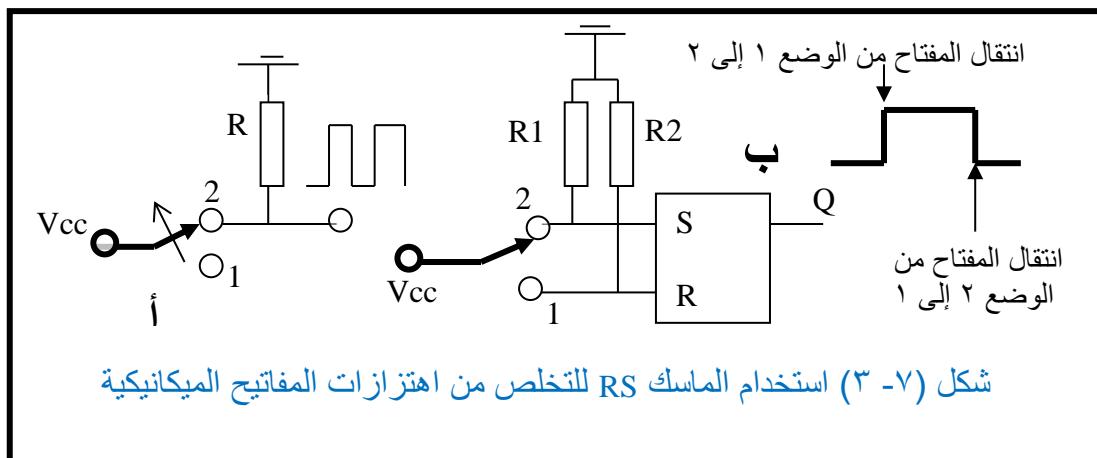

| ١١٧ | ١-٢-٧ الماسك RS كمزيل للاهتزازات                   |

| ١١٨ | ٣-٧ الشريحة 74279 ماسك RS رباعي                    |

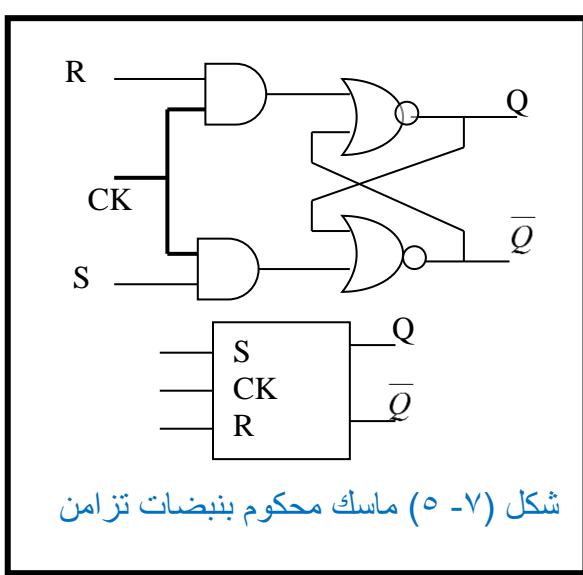

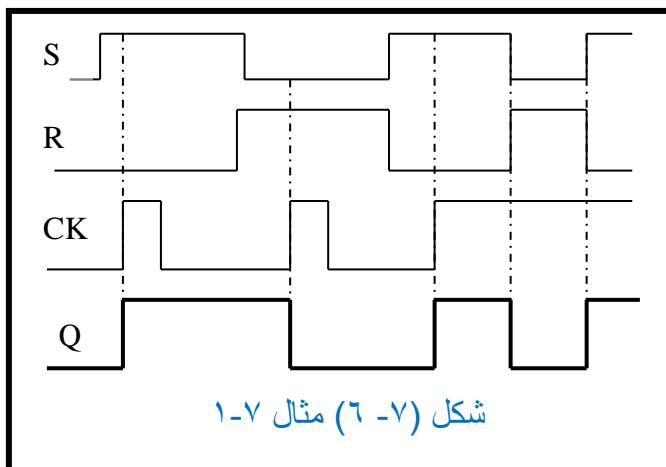

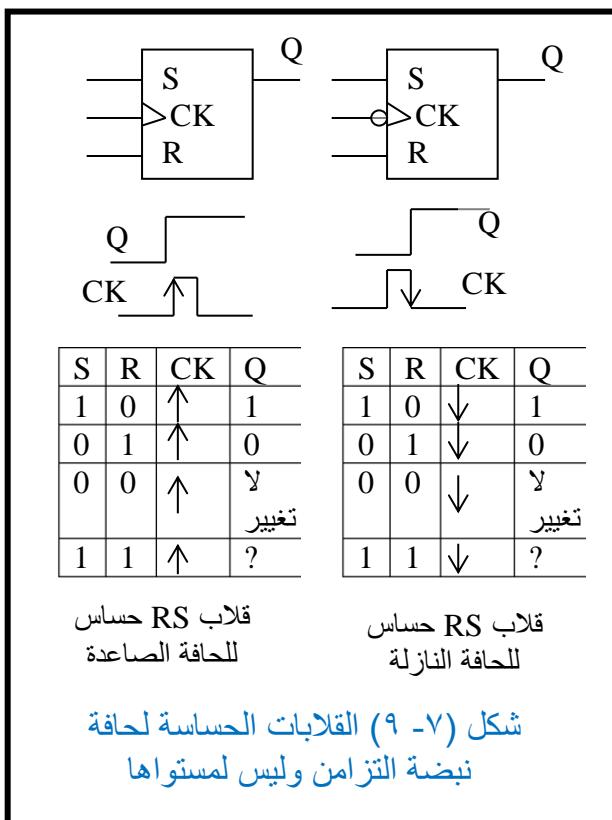

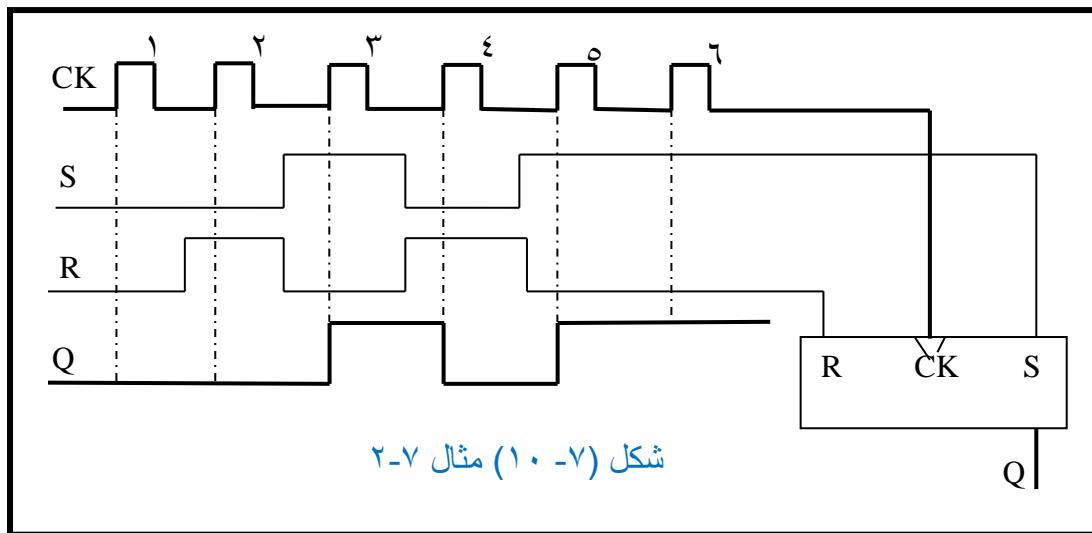

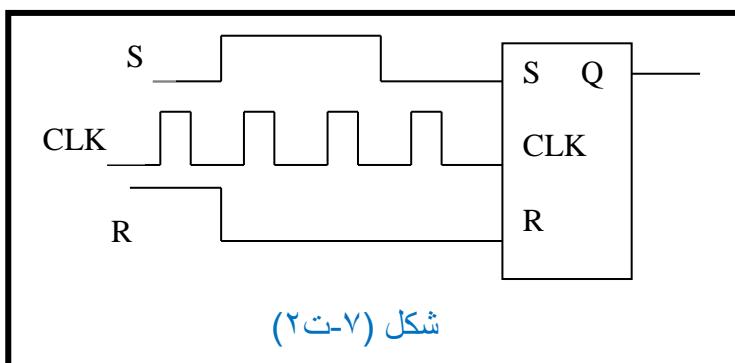

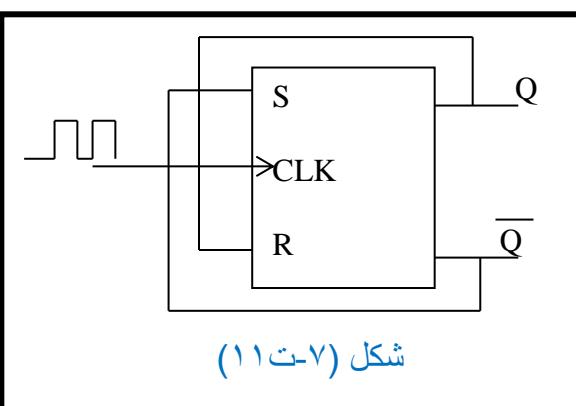

| ١١٨ | ٤-٧ الماسك RS المحكم بنبضات تزامن Clock            |

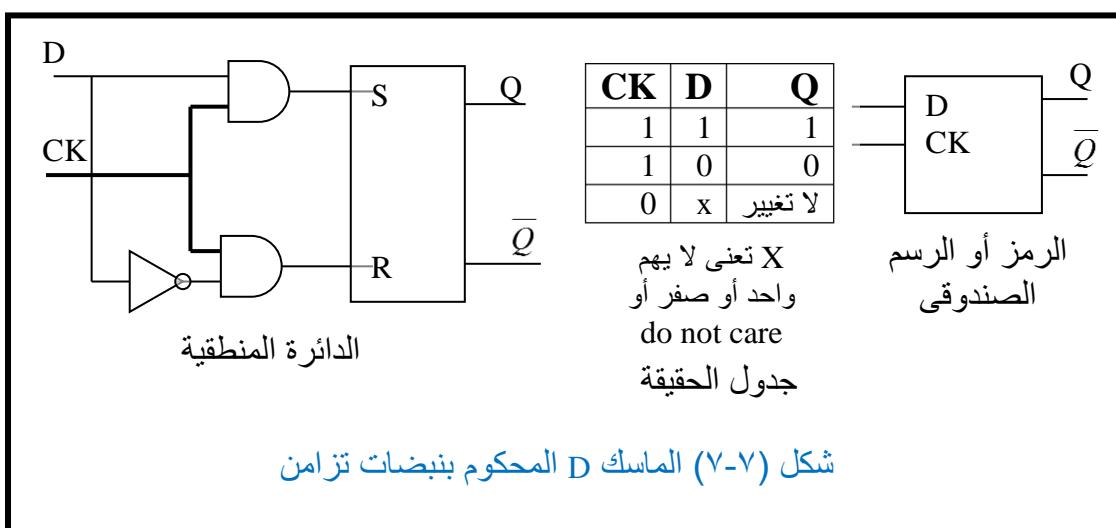

| ١١٩ | ٥-٧ الماسك D المحكم بنبضات التزامن                 |

| ١٢٠ | ٦-٧ الشريحة 7475 ماسك D رباعي                      |

| ١٢٠ | ٧-٧ القلابات Flip Flops                            |

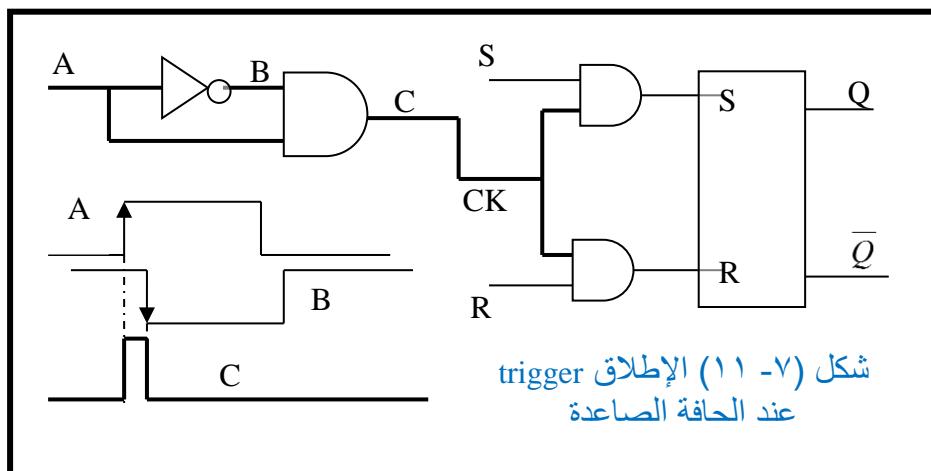

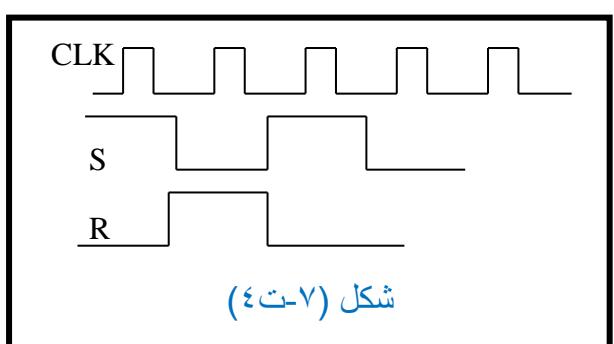

| ١٢٢ | ٨-٧ طريقة الإطلاق trigger عند أي الحافة            |

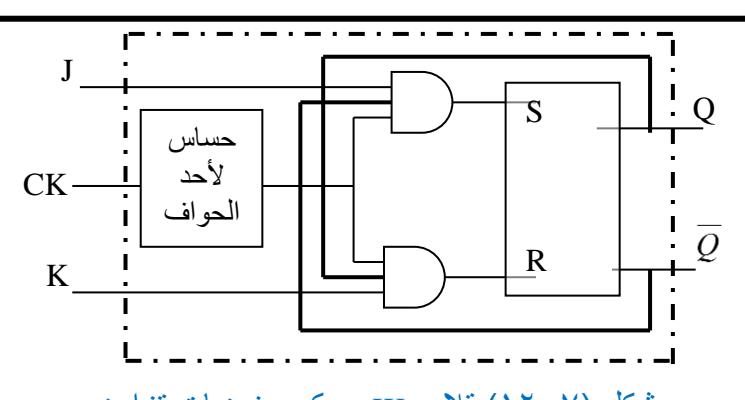

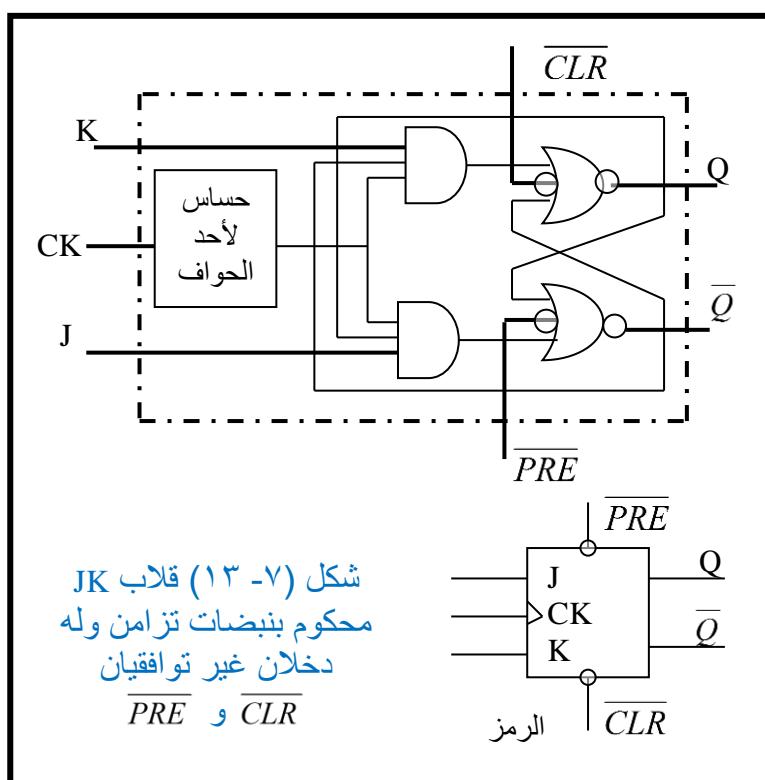

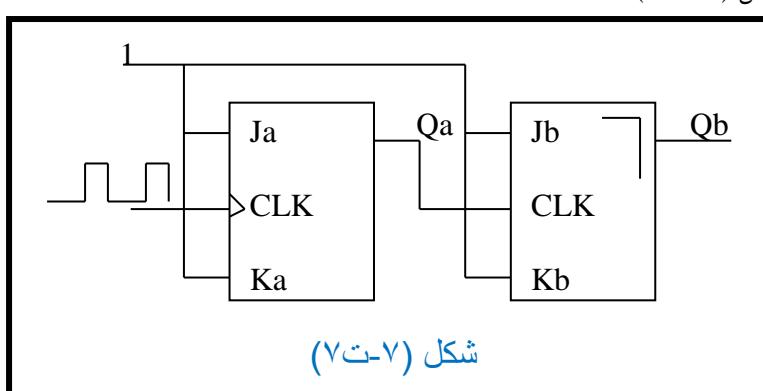

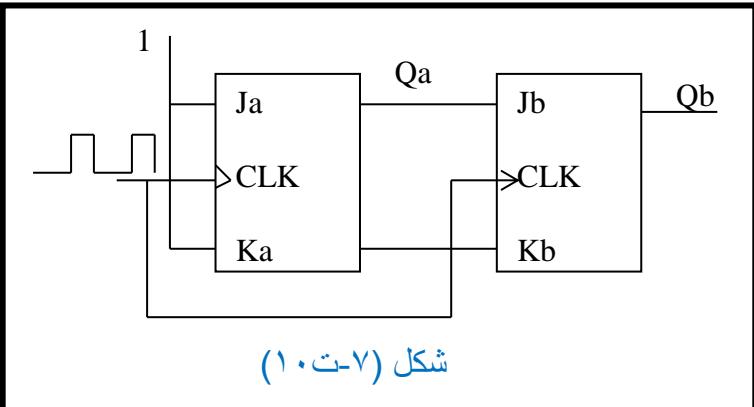

| ١٢٢ | ٩-٧ القلاب JK                                      |

| ١٢٣ | ١٠-٧ الدخول غير التوافقة Asynchronous Inputs       |

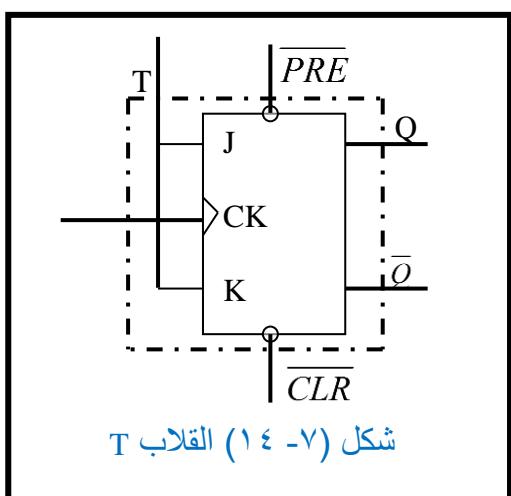

| ١٢٤ | ١١-٧ القلاب T                                      |

| ١٢٤ | ١٢-٧ الشريحة 74ls74 قلابان من النوع D              |

| ١٢٤ | ١٣-٧ الشريحة 74ls76 قلابان من النوع JK             |

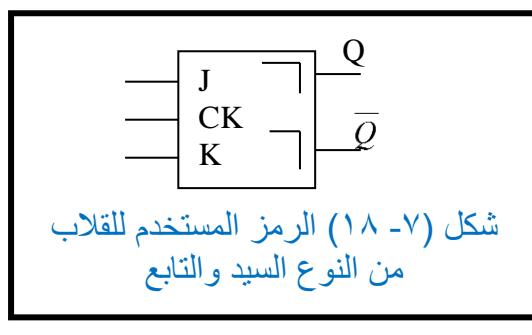

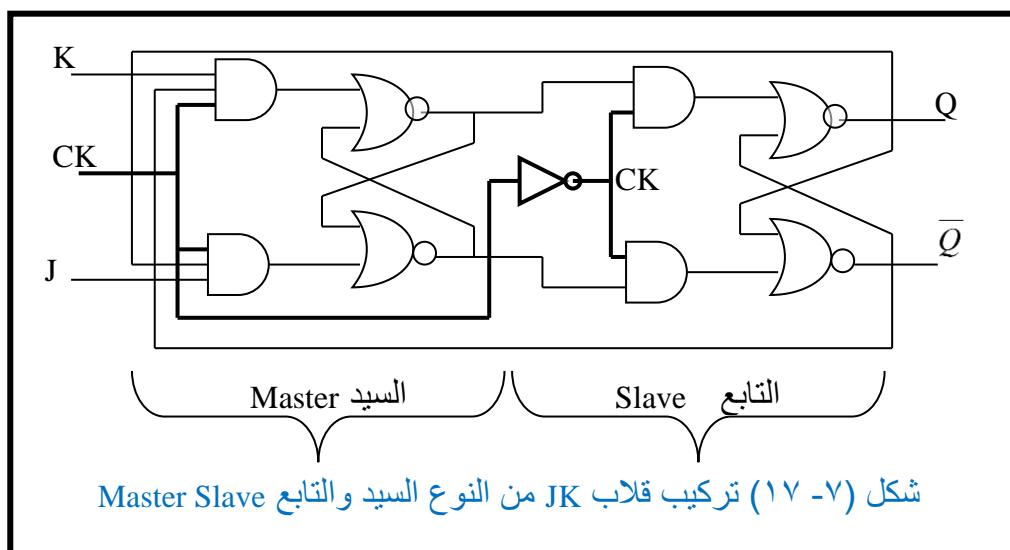

| ١٢٥ | ١٤-٧ قلاب السيد والعبد Master Slave Flip Flop      |

| ١٢٦ | ١٥-٧ الشريحة 7473 قلابان JK من نوع السيد والتتابع  |

| ١٢٦ | ١٦-٧ الشريحة 74107 قلابان JK من نوع السيد والتتابع |

| ١٢٧ | ١٧-٧ الشريحة 74109 قلابان JK حساس للحافة الصاعدة   |

| ١٢٨ | ١٨-٧ الشريحة 74112 قلابان JK حساس للحافة النازلة   |

| ١٢٨ | ١٩-٧ الشريحة 74113 قلابان JK حساس للحافة النازلة   |

| ١٢٨ | ٢٠-٧ الشريحة 74116 ماسكان ذو ٤ بت لكل منها         |

|     |                                                                  |

|-----|------------------------------------------------------------------|

| ١٢٩ | ٧-٢١ الشريحة 74173 أربع قلابات من النوع D ، ثلاثة المنطق         |

| ١٢٩ | ٧-٢٢ الشريحة 74174 ستة قلابات من النوع D                         |

| ١٣٠ | ٧-٢٣ الشريحة 74175 أربع قلابات من النوع D                        |

| ١٣٠ | ٧-٢٤ الشريحة 74273 ثمان قلابات من النوع D                        |

| ١٣٠ | ٧-٢٥ الشريحة 74373 و 74374 ثمان قلابات من النوع D ، ثلاثة المنطق |

| ١٣١ | ٧-٢٦ بعض الخواص المهمة للقلابات                                  |

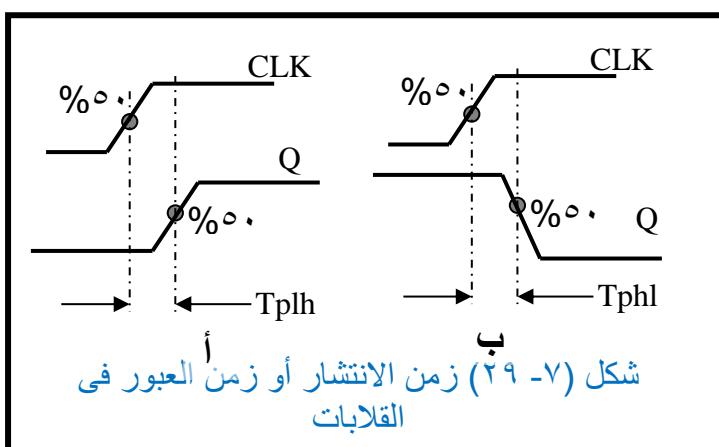

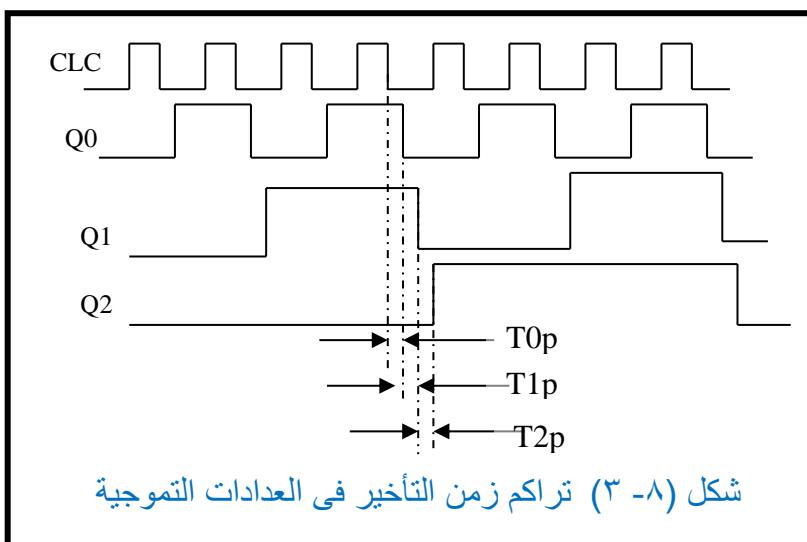

| ١٣١ | ٧-٢٧ زمن الانتشار أو زمن العبور Propagation delay time           |

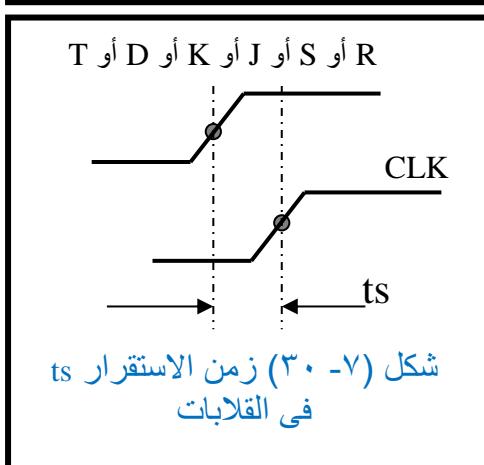

| ١٣٢ | ٧-٢٨ زمن الاستقرار Set up time                                   |

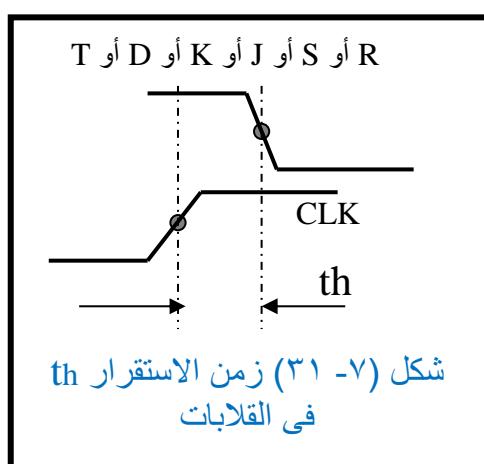

| ١٣٢ | ٧-٣ زمن المسلح Hold time                                         |

| ١٣٢ | ٧-٤ أقصى قيمة لتردد الساعة                                       |

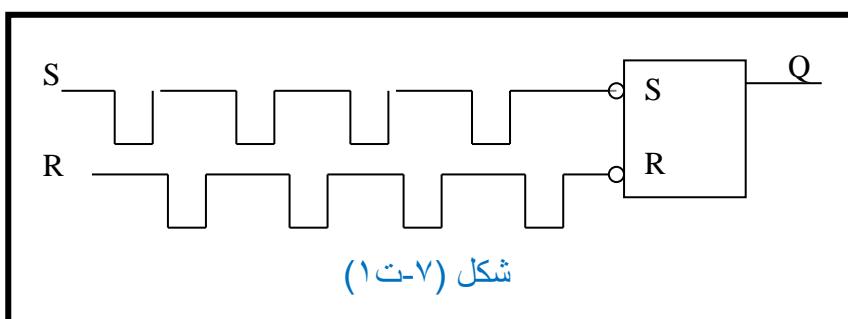

| ١٣٢ | ٧-٥ تطبيقات القلابات                                             |

| ١٣٣ | ٧-٦ تمارين                                                       |

## Digital Counters

|     |                                                               |

|-----|---------------------------------------------------------------|

| ١٣٥ | <b>الفصل الثامن: العدادات الرقمية</b>                         |

| ١٣٦ | ٨-١ مقدمة                                                     |

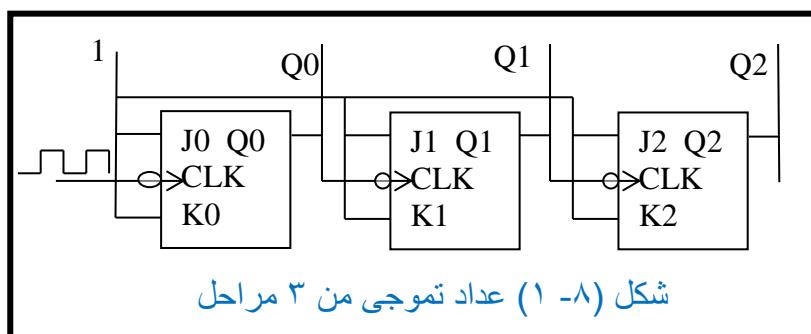

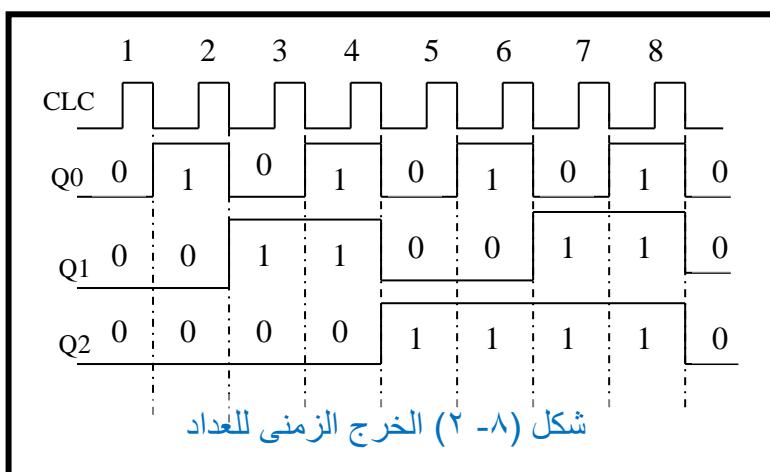

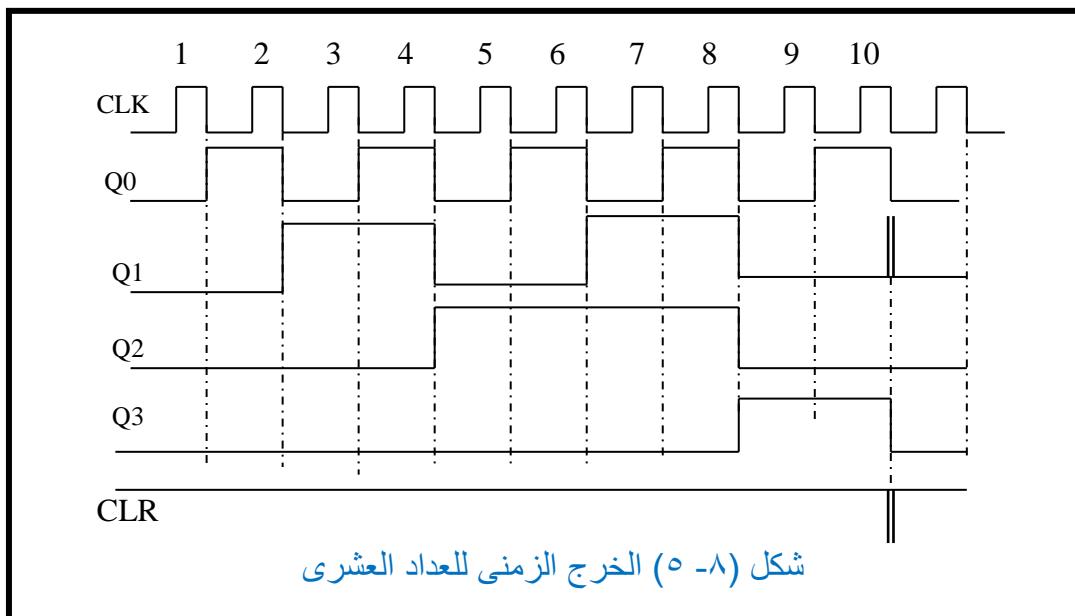

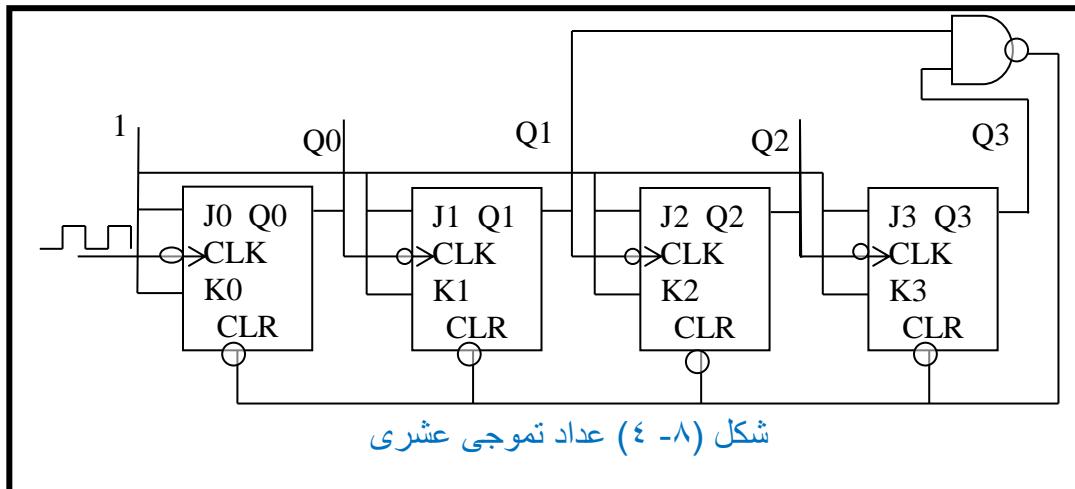

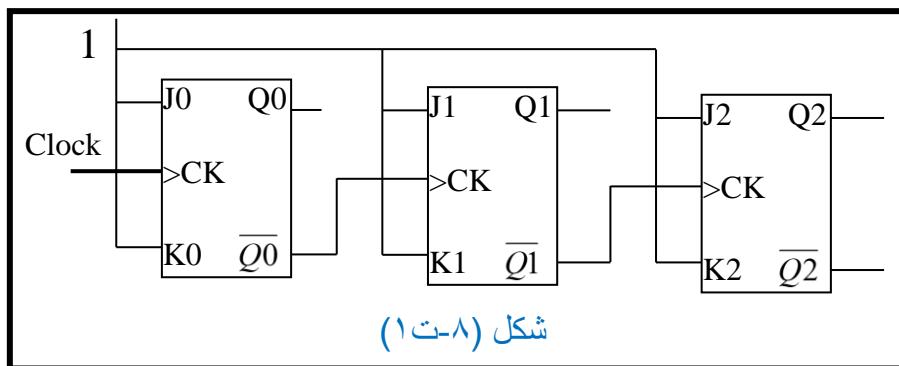

| ١٣٦ | ٨-٢ العدادات التموجية أو الغير توافقية                        |

| ١٣٧ | ٨-٣ عدادات تموجية لأى قاعدة                                   |

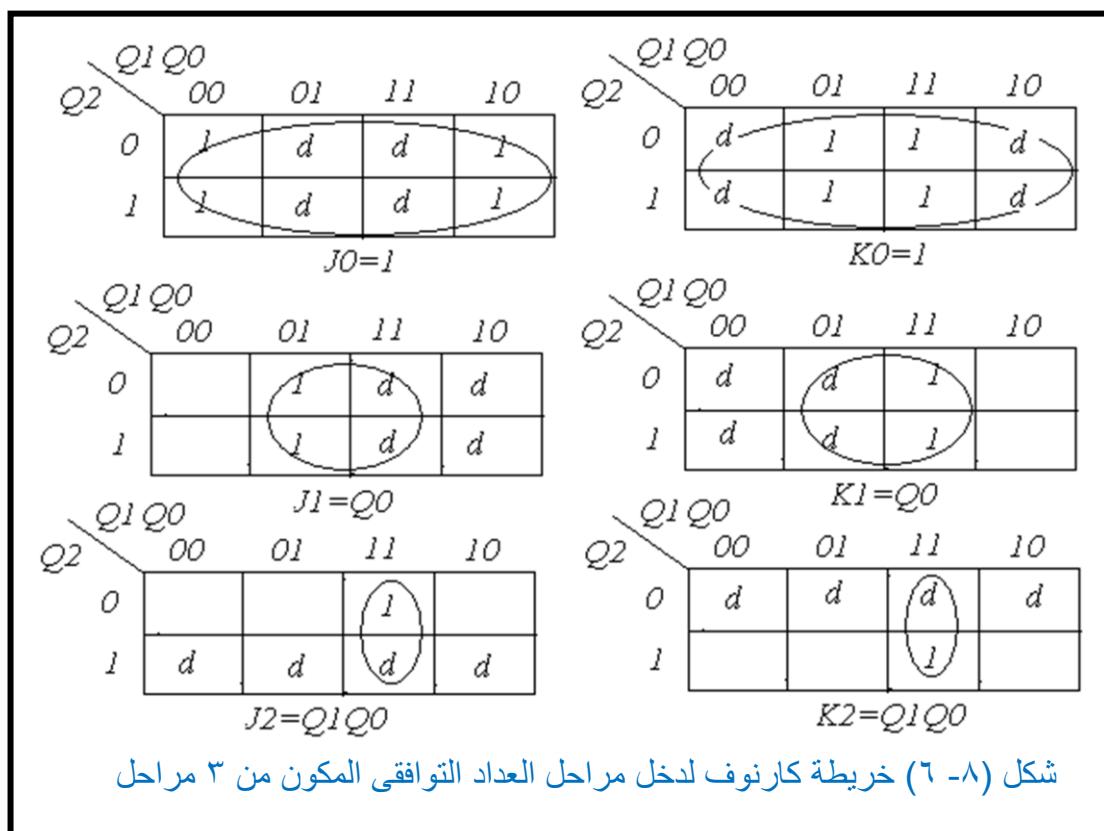

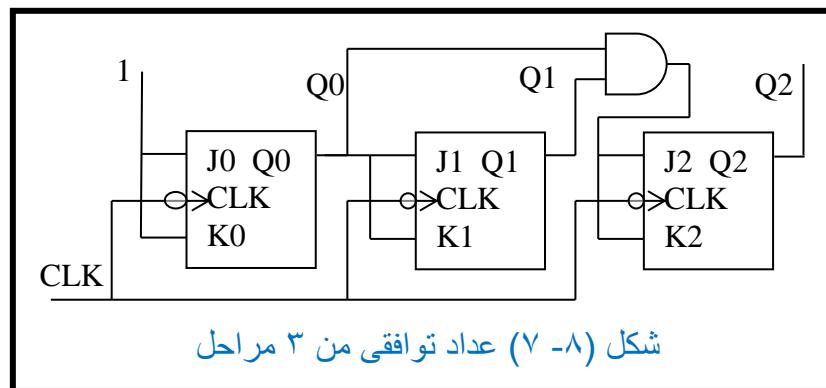

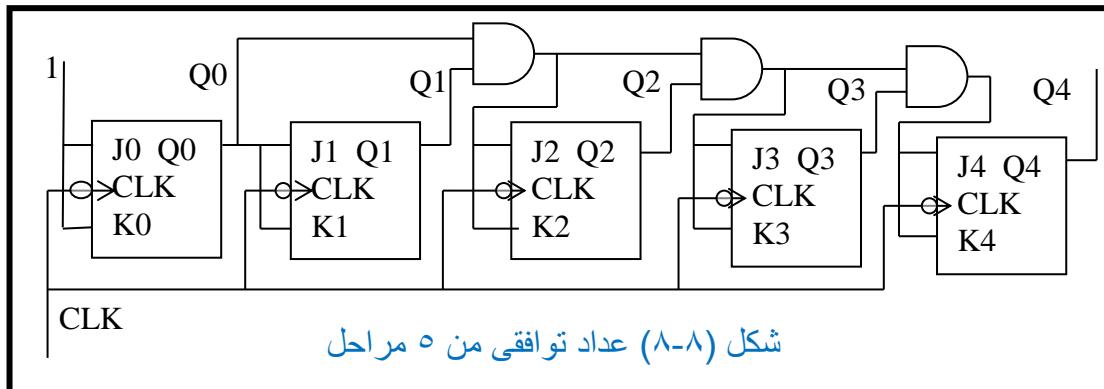

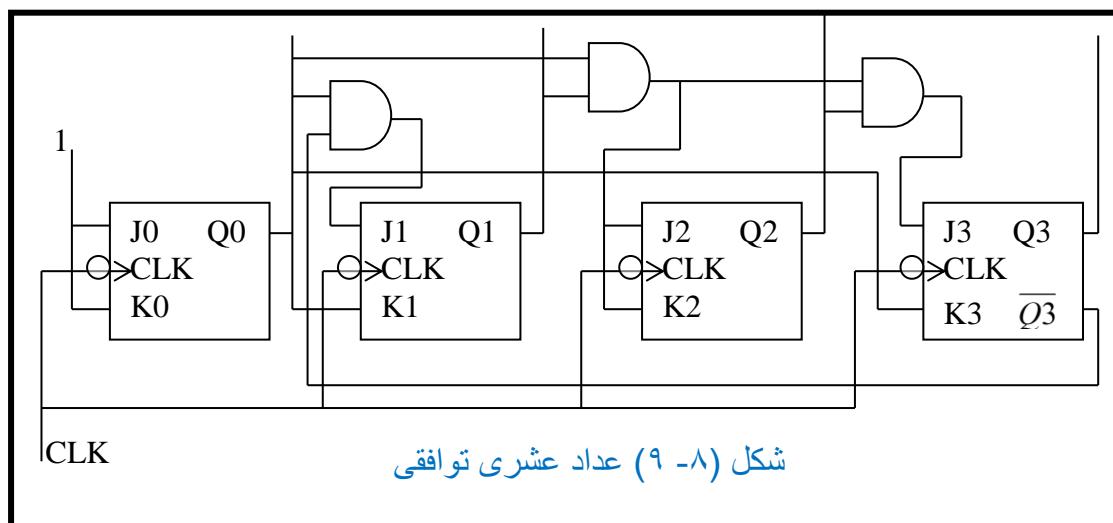

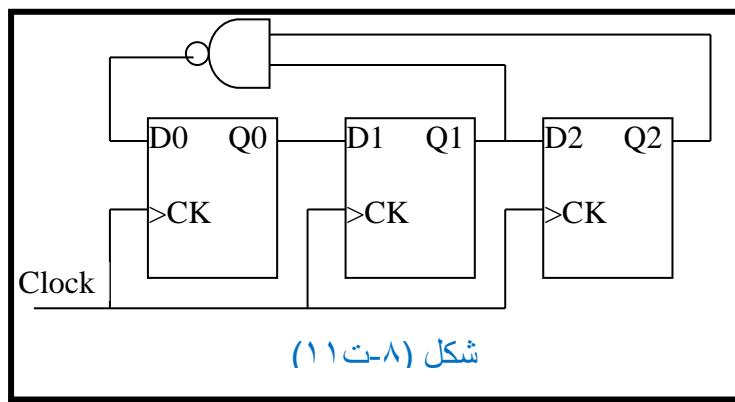

| ١٣٩ | ٨-٤ العداد التوافقي                                           |

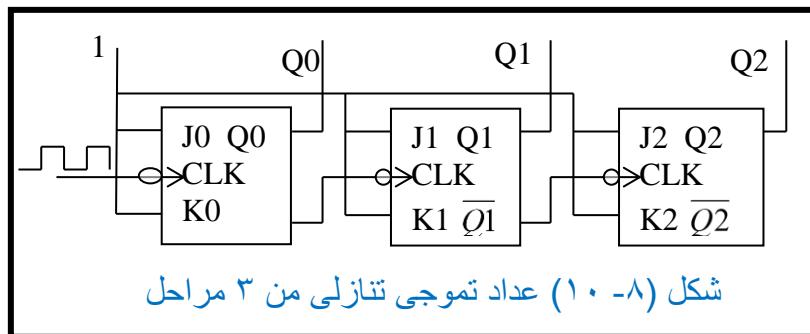

| ١٤٢ | ٨-٥ العدادات التنازليه                                        |

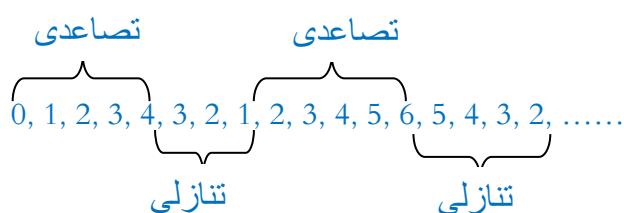

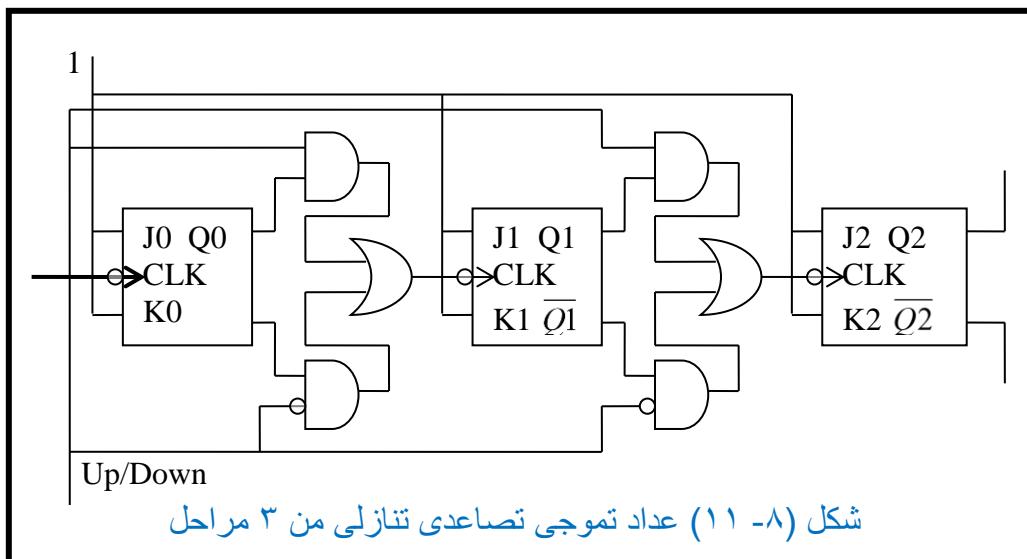

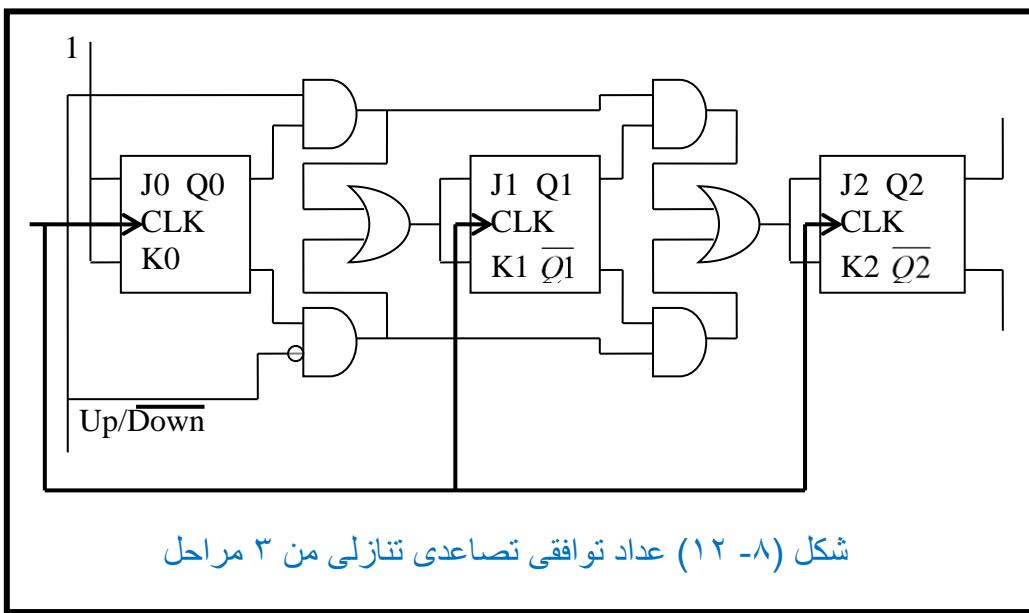

| ١٤٣ | ٨-٦ العدادات التصاعدية التنازليه                              |

| ١٤٤ | ٨-٧ الشريحة 7490 عداد عشري تموجي                              |

| ١٤٥ | ٨-٨ الشريحة 7492 عداد تموجي قاسم على ١٢                       |

| ١٤٦ | ٨-٩ الشريحة 7493 عداد تموجي ٤ مراحل                           |

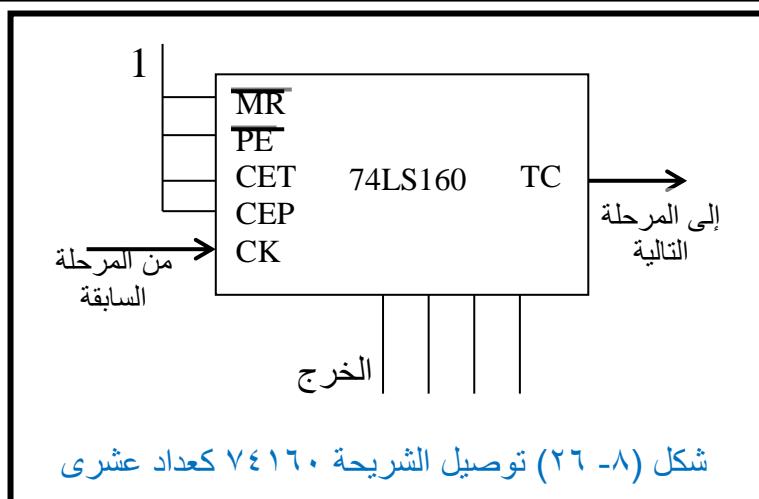

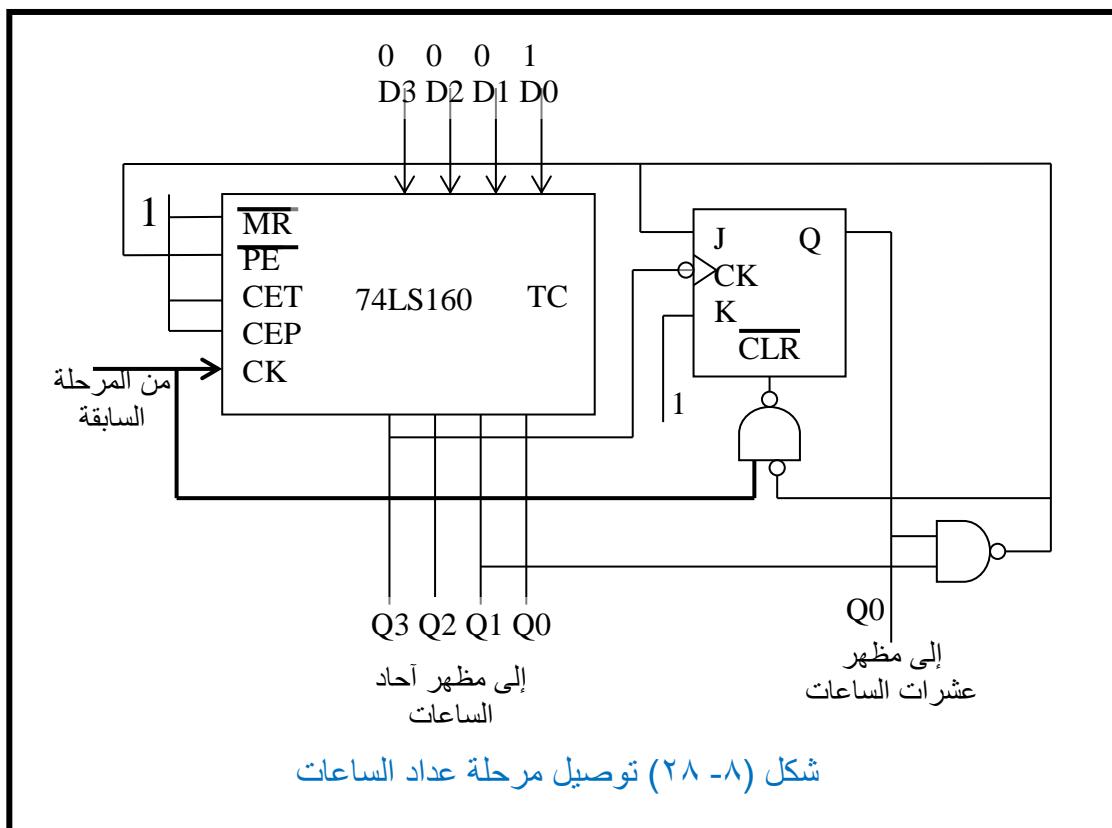

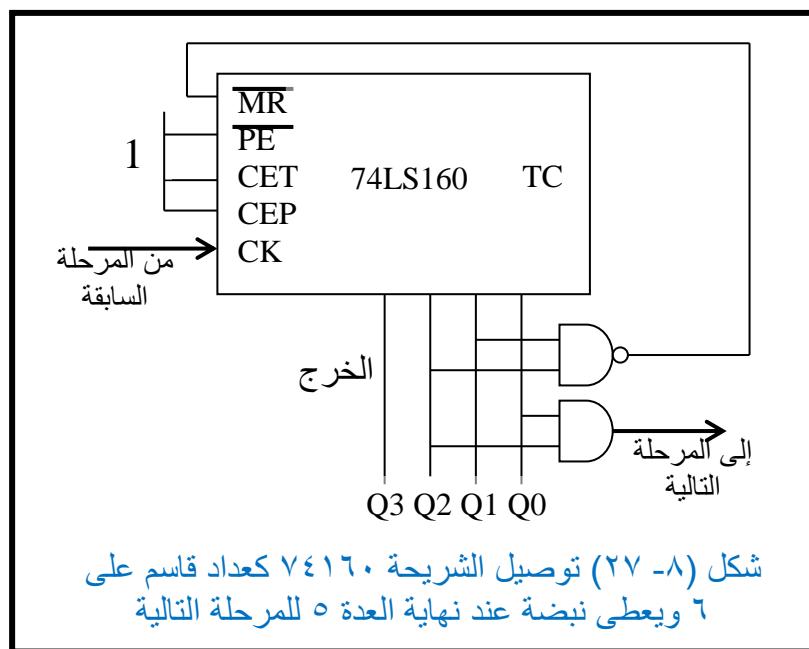

| ١٤٧ | ٨-١٠ الشريحة 74160 و 74162 عداد توافقى عشري                   |

| ١٤٧ | ٨-١١ الشريحة 74161 و 74163 عدادات توافقية من ٤ مراحل          |

| ١٤٨ | ٨-١٢ الشريحة 74LS168 و 74LS169 عدادات توافقية تصاعدية/تنازليه |

| ١٤٩ | ٨-١٣ الشريحة 74190 و 74191 عدادات توافقية تصاعدية/تنازليه     |

| ١٥٠ | ٨-١٤ الشريحة 74192 و 74193 عدادات تصاعدية/تنازل               |

| ١٥١ | ٨-١٥ الشريحة 74LS197 عداد تموجي ٤ مراحل                       |

| ١٥١ | ٨-١٦ الشريحة 74LS290 عداد عشري تموجي                          |

| ١٥٢ | ٨-١٧ الشريحة 74LS293 عداد ثنائى تموجي ٤ مراحل                 |

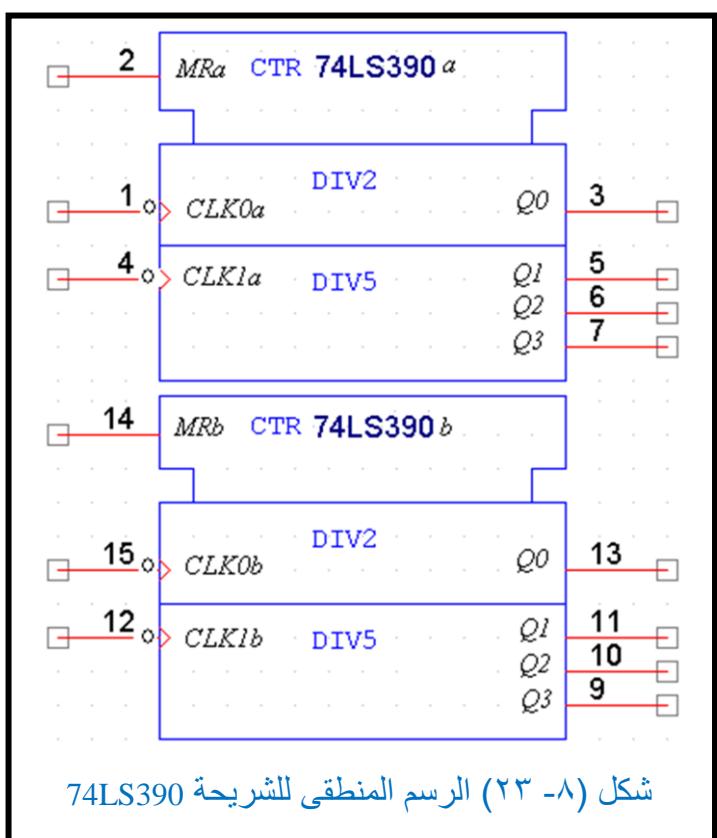

| ١٥٣ | ٨-١٨ الشريحة 74LS390 عدادان عشريان تموجيان                    |

|     |                                                             |

|-----|-------------------------------------------------------------|

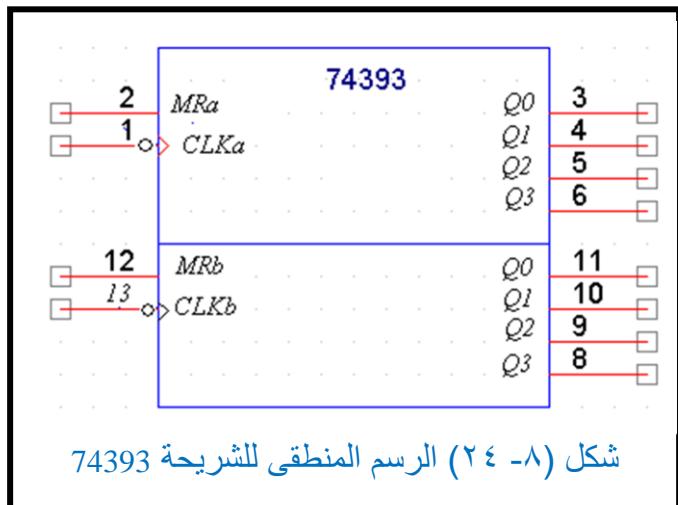

| ١٥٣ | ١٩-٨ الشريحة 74LS393 عدادان ثنائيان توجيهان كل منها ٤ مراحل |

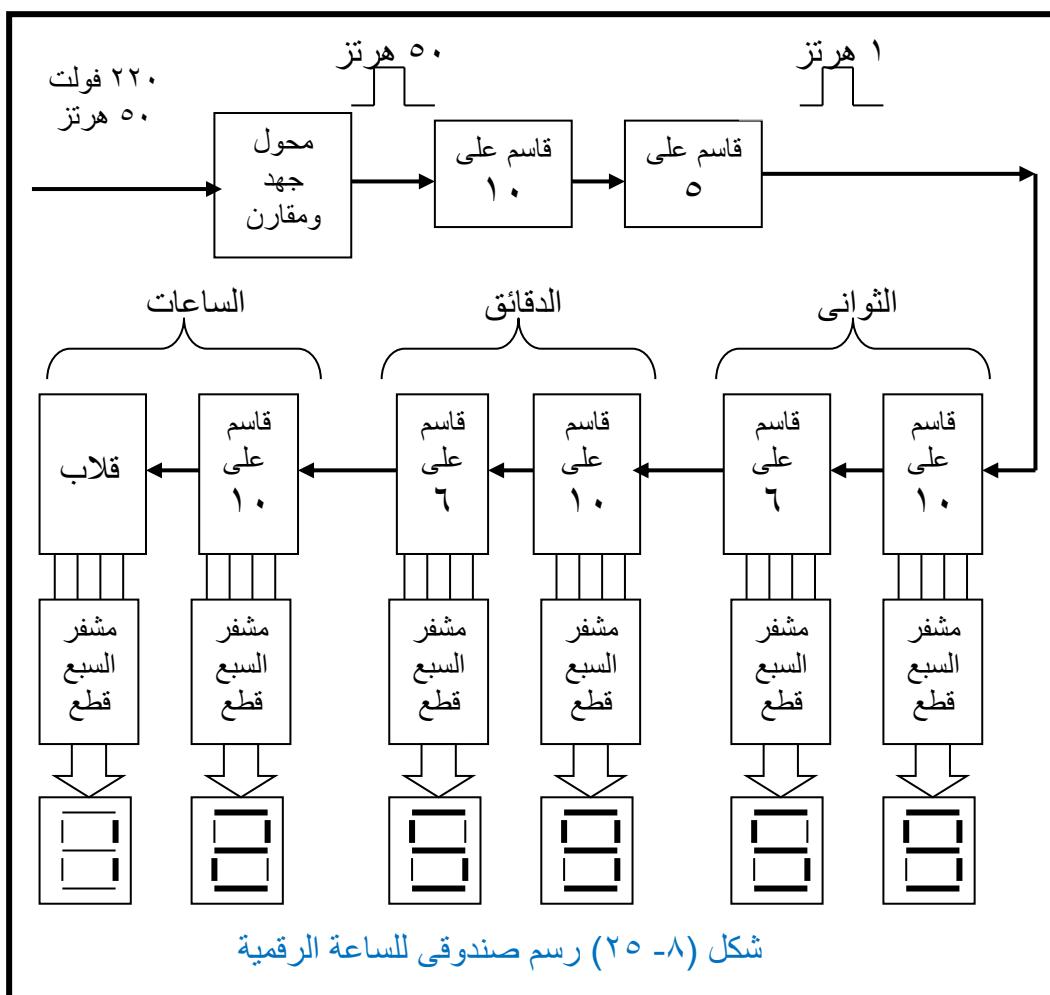

| ١٥٤ | ٢٠-٨ تطبيقات العدادات                                       |

| ١٥٧ | ٢١-٨ تمارين                                                 |

**الفصل التاسع: مسجلات الإزاحة Shift Registers**

|     |                                                                       |

|-----|-----------------------------------------------------------------------|

| ١٦٠ | ١-٩ مقدمة                                                             |

| ١٦٠ | ٢-٩ وحدة بناء مسجل الإزاحة                                            |

| ١٦٠ | ٣-٩ العمليات المختلفة على محتويات مسجل الإزاحة                        |

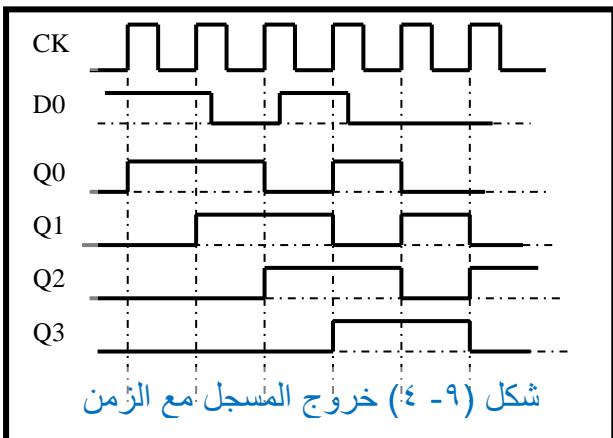

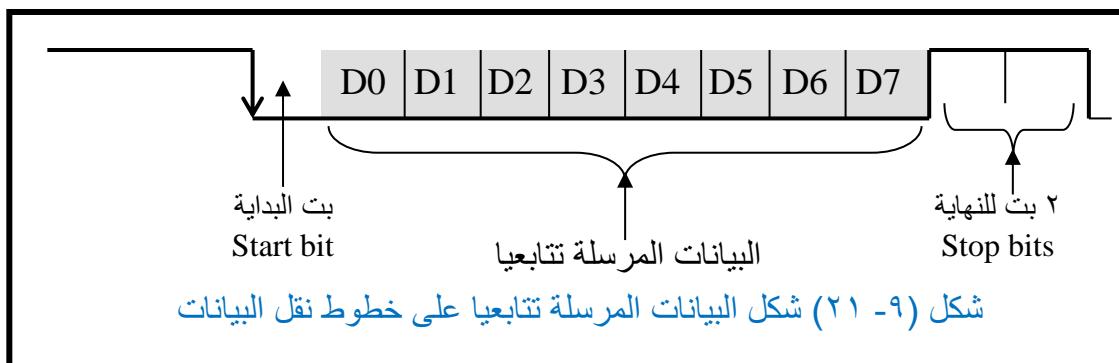

| ١٦١ | ٤-٩ الإدخال والإخراج المتتالي للبيانات                                |

| ١٦٢ | ٥-٩ إدخال البيانات على التوالى وإخراجها على التوازى                   |

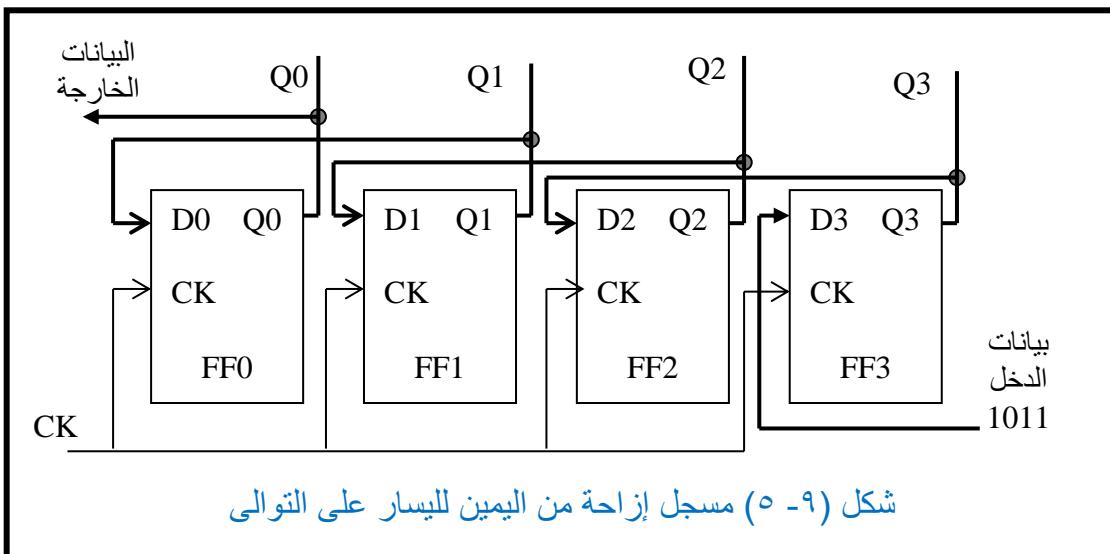

| ١٦٢ | ٦-٩ الإزاحة على التوالى من اليمين لليسار                              |

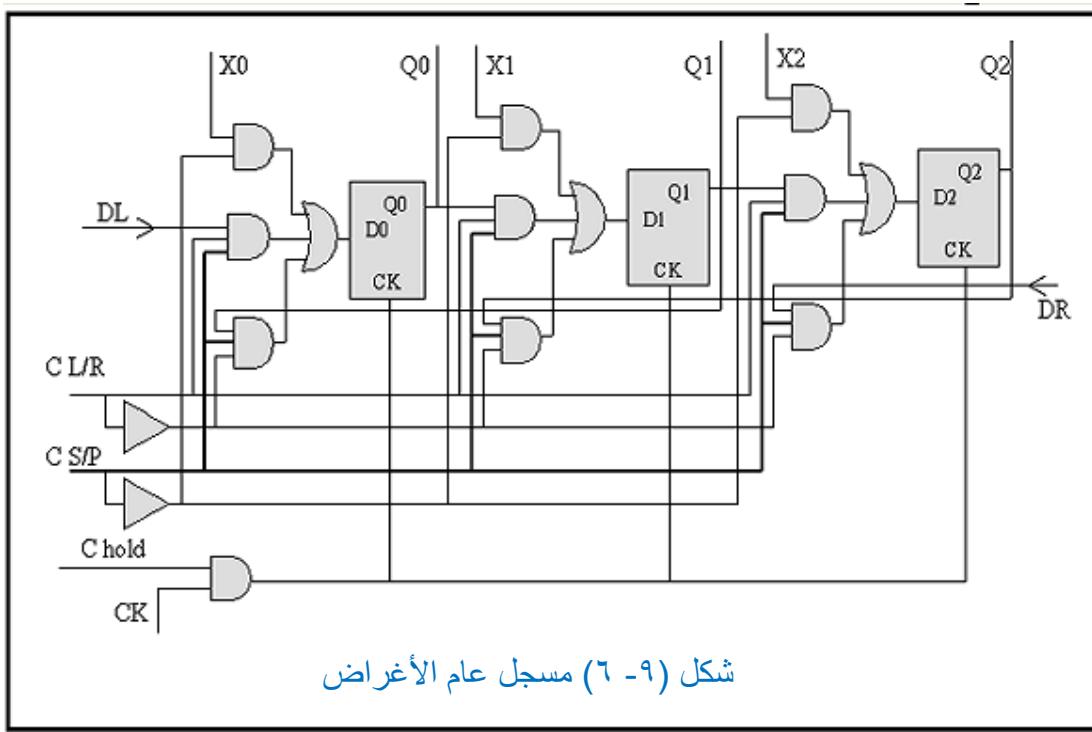

| ١٦٢ | ٧-٩ مسجل الإزاحة عام الأغراض                                          |

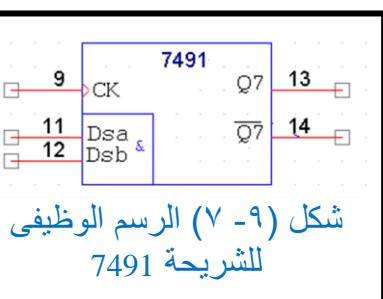

| ١٦٣ | ٨-٩ الشريحة 7491 مسجل إزاحة توالى ٨ بت                                |

| ١٦٣ | ٩-٩ الشريحة 7494 مسجل ٤ بت إدخال توازى أو توالى ، إخراج توالى         |

| ١٦٤ | ١٠-٩ الشريحة 7495 مسجل ٤ بت إدخال توازى أو توالى ، إخراج توالى        |

| ١٦٥ | ١١-٩ الشريحة 7496 مسجل ٥ بت إدخال توازى أو توالى إخراج توالى أو توازى |

| ١٦٦ | ١٢-٩ الشريحة 74164 مسجل ٨ بت إدخال توالى ، إخراج توازى                |

| ١٦٧ | ١٣-٩ الشريحة 74165 مسجل ٨ بت إدخال توالى أو توازى ، إخراج توالى       |

| ١٦٧ | ١٤-٩ الشريحة 74166 مسجل ٨ بت إدخال توالى أو توازى ، إخراج توالى       |

| ١٦٧ | ١٥-٩ الشريحة 74194 مسجل متعدد الأغراض ٤ بت ثنائى الاتجاه              |

| ١٦٨ | ١٦-٩ الشريحة 74195 مسجل ٤ بت ، دخل توازى خرج توالى                    |

| ١٦٩ | ١٧-٩ الشريحة 74199 مسجل ٨ بت ، دخل توازى خرج توالى                    |

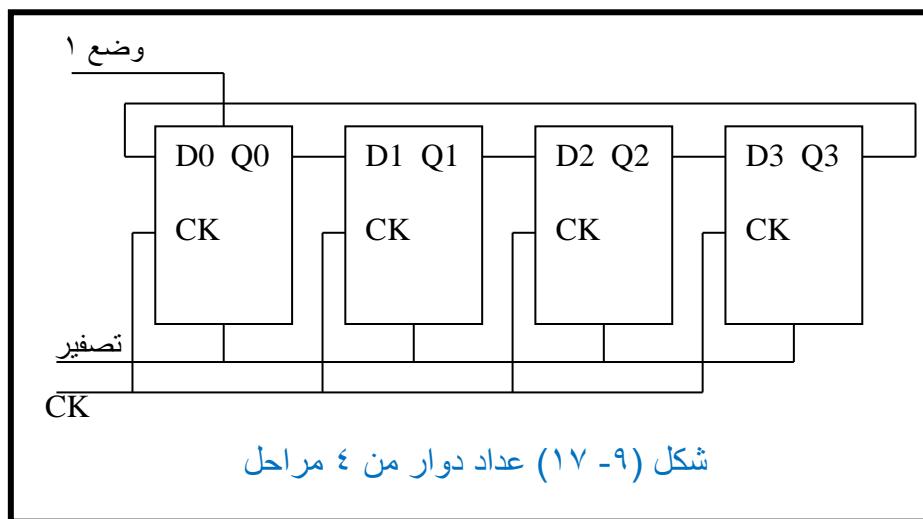

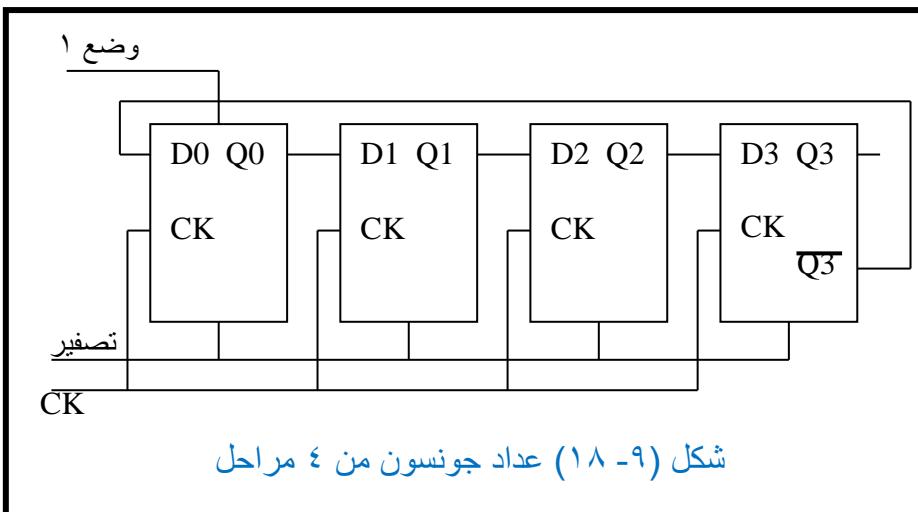

| ١٧٠ | ١٨-٩ العدادات الدوارة                                                 |

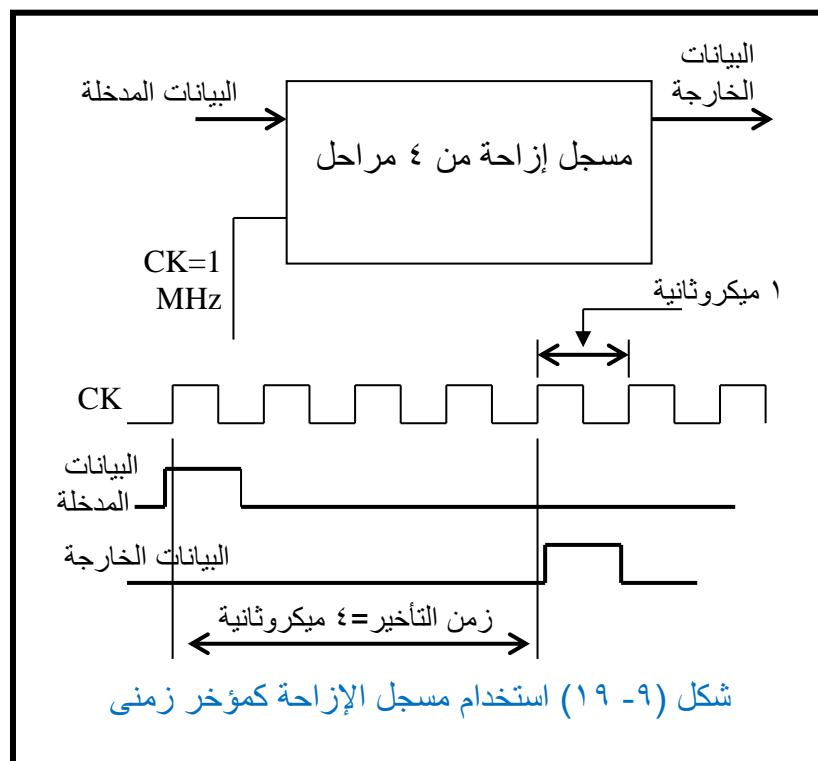

| ١٧١ | ١٩-٩ تطبيقات مسجلات الإزاحة                                           |

| ١٧٤ | ٢٠-٩ تمارين                                                           |

**الفصل العاشر: الذاكرة**

|     |            |

|-----|------------|

| ١٧٥ | ١-١٠ مقدمة |

| ١٧٦ |            |

|     |                                                                                   |

|-----|-----------------------------------------------------------------------------------|

| ١٧٦ | ٤-١ وحدة تخزين البيانات (البت والبait والورد)                                     |

| ١٧٧ | ٣-١ العمليات الأساسية على الذاكرة                                                 |

| ١٨٠ | ٤-١ ذاكرة الاتصال العشوائي                                                        |

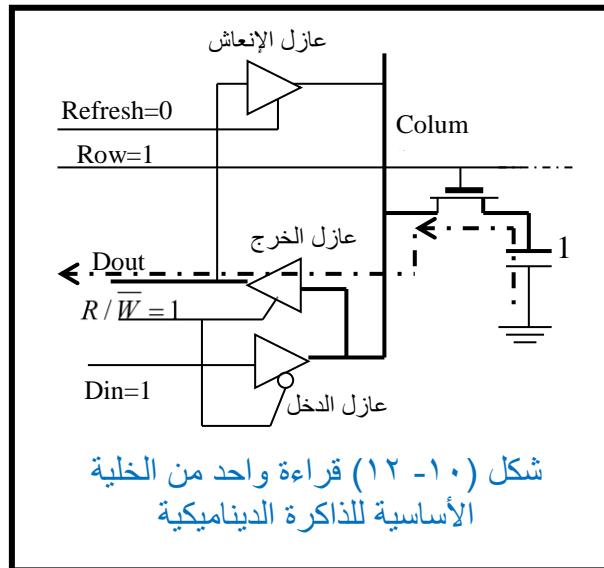

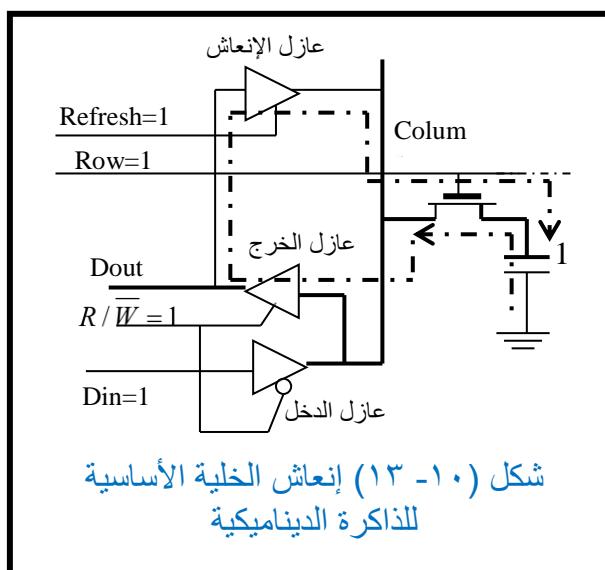

| ١٨٣ | ٥-١ ذاكرة الاتصال العشوائي الديناميكية                                            |

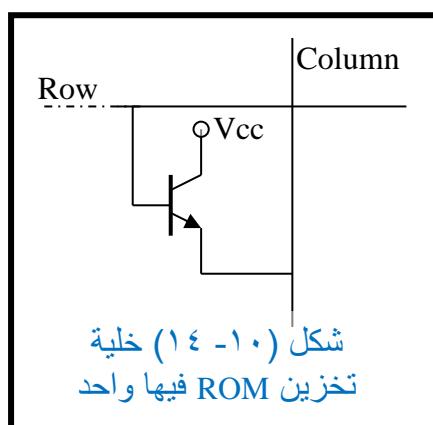

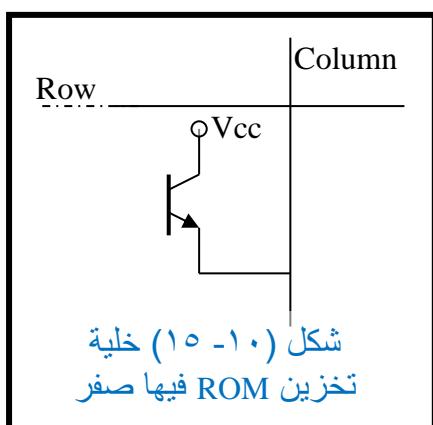

| ١٨٥ | ٦-١ ذاكرة القراءة فقط                                                             |

| ١٨٨ | ٧-١ الشريحة ٢١١٤ ذاكرة استاتيكية ١ كيلو × ٤ بت                                    |

| ١٨٨ | ٨-١ الشريحة ٦١١٦ ذاكرة استاتيكية ٢ كيلو بait                                      |

| ١٨٨ | ٩-١ الشريحة ٦٢٦٤ ذاكرة استاتيكية ٨ كيلو بait                                      |

| ١٨٩ | ١٠-١ الشريحة ٦٢٢٥٦ ذاكرة استاتيكية ٣٢ كيلو بait                                   |

| ١٩٠ | ١١-١ الشريحة ٢٧١٦ ذاكرة ٢ EEPROM كيلوبايت                                         |

| ١٩١ | ١٢-١ الشريحة ٢٧٣٢ ذاكرة ٤ EEPROM كيلوبايت                                         |

| ١٩١ | ١٣-١ الشريحة ٢٧٦٤ ذاكرة ٨ EEPROM كيلوبايت والشريحة ٢٧٢٥٦ ذاكرة ٢٢ EEPROM كيلوبايت |

| ١٩٢ | ١٤-١ تمارين                                                                       |

**الفصل الحادى عشر: دوائر التوقيت Timers**

|     |                                                  |

|-----|--------------------------------------------------|

| ١٩٤ |                                                  |

| ١٩٥ | ١-١ مقدمة                                        |

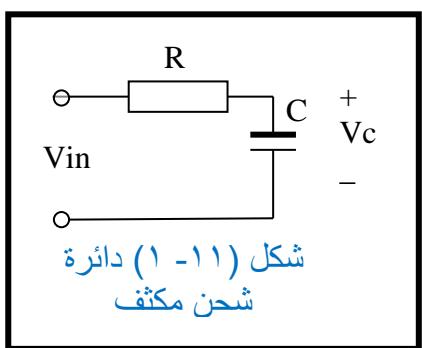

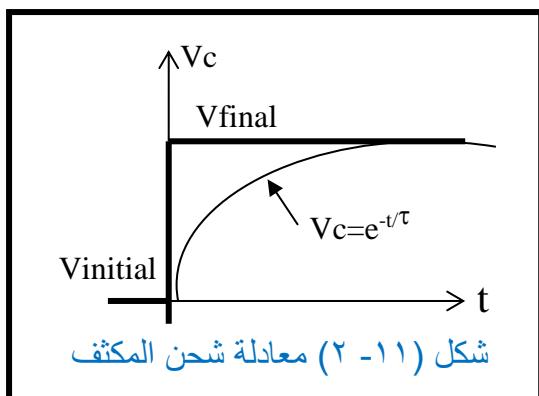

| ١٩٥ | ٢-١ معادلة الجهد على مكثف في دائرة مقاومة ومكثف  |

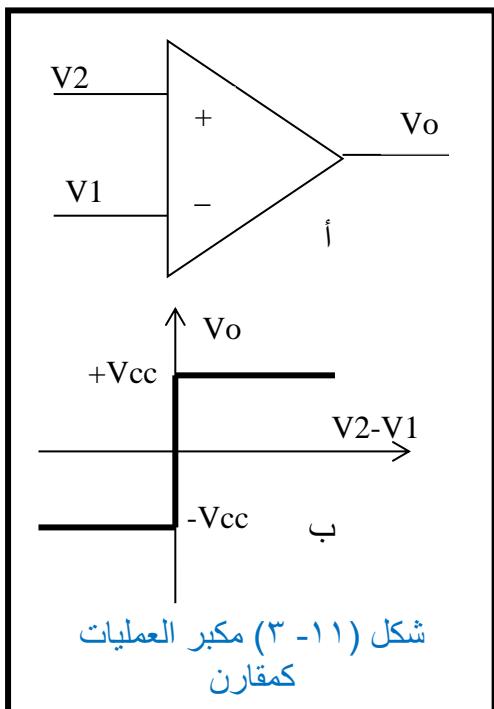

| ١٩٦ | ٣-١ المقارن Comparator                           |

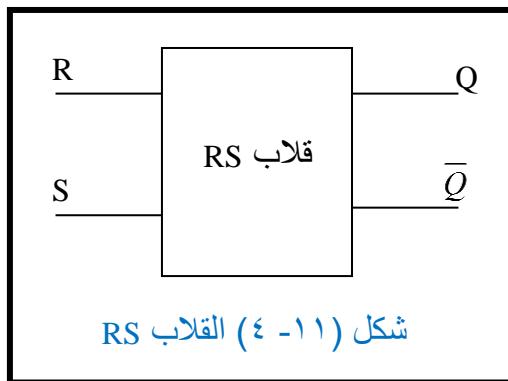

| ١٩٦ | ٤-١ القلاب Flip Flop                             |

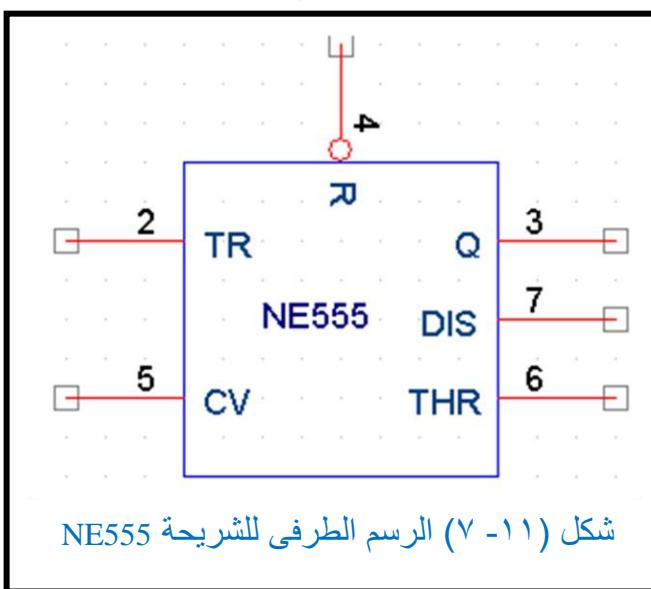

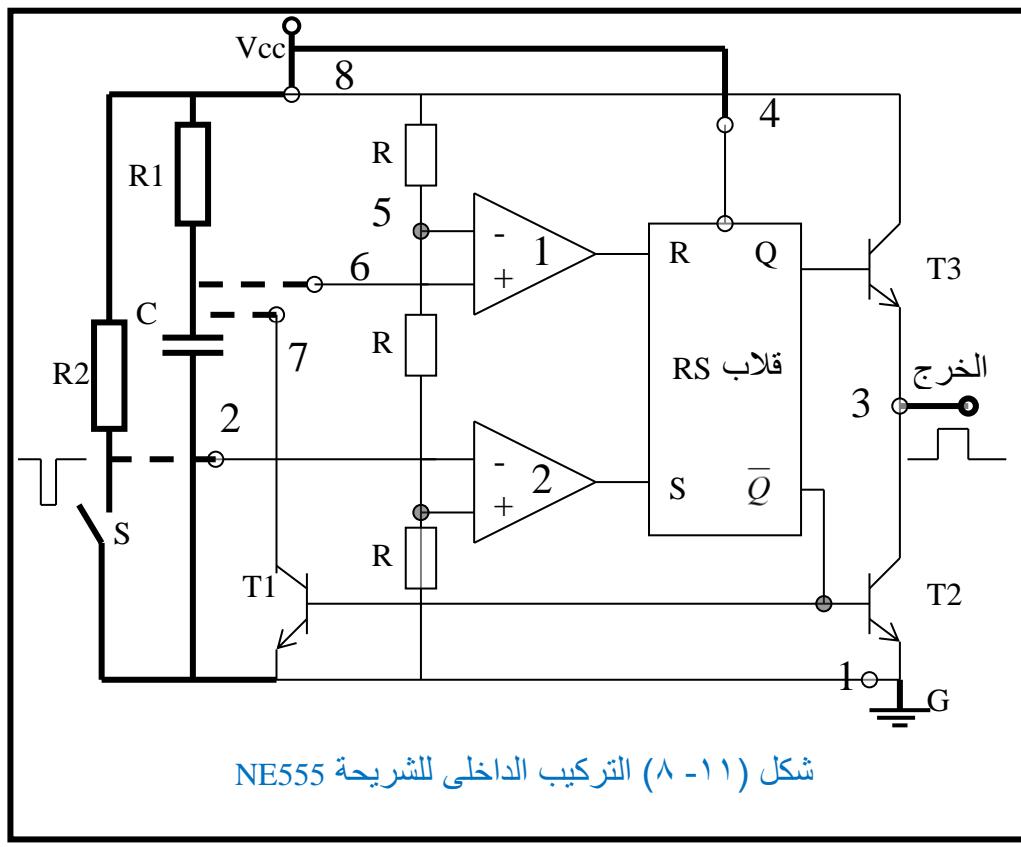

| ١٩٨ | ٥-١ التركيب الداخلى وطريقة التشغيل للشريحة NE555 |

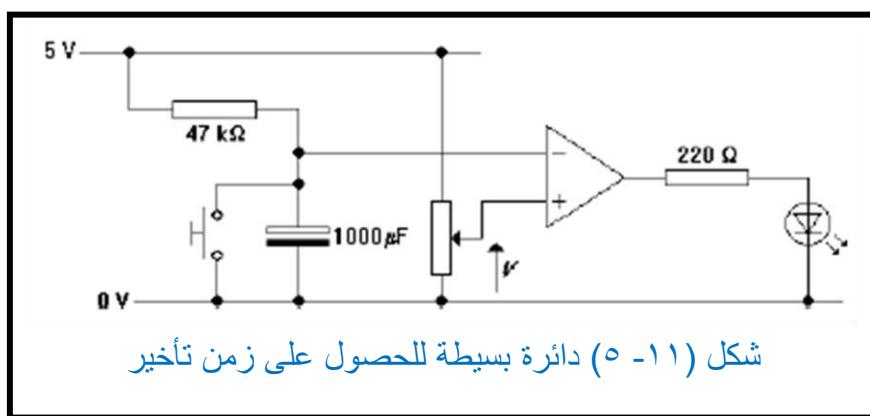

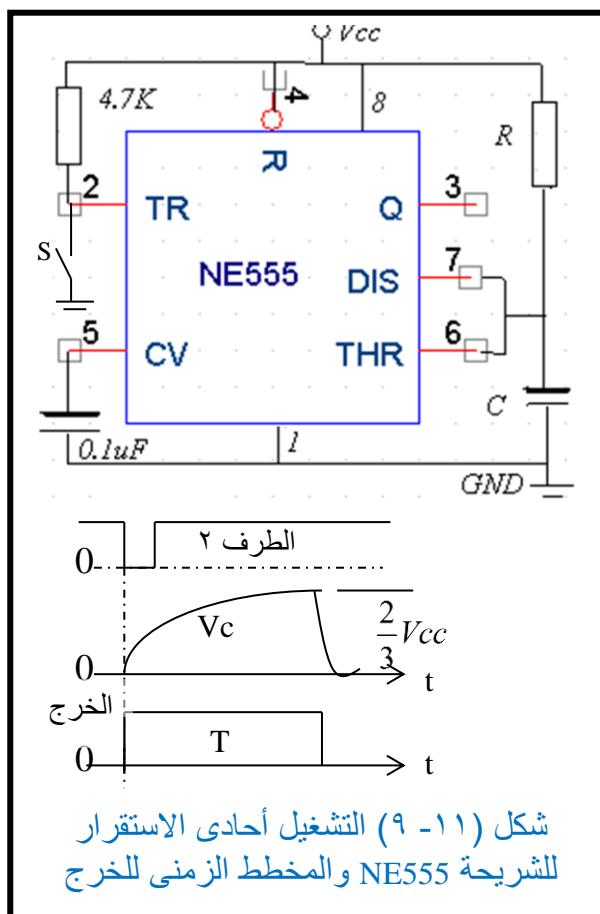

| ١٩٩ | ٦-١ طريقة التشغيل أحادية الثبات                  |

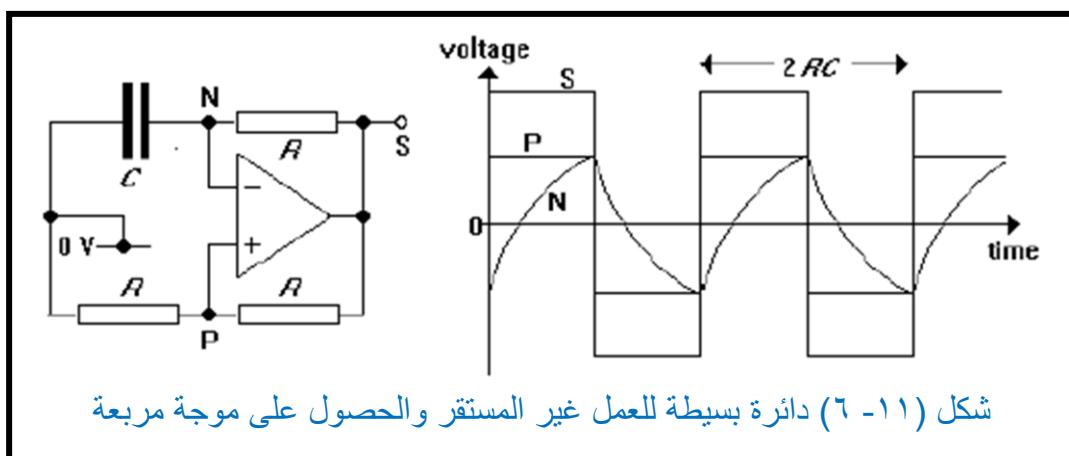

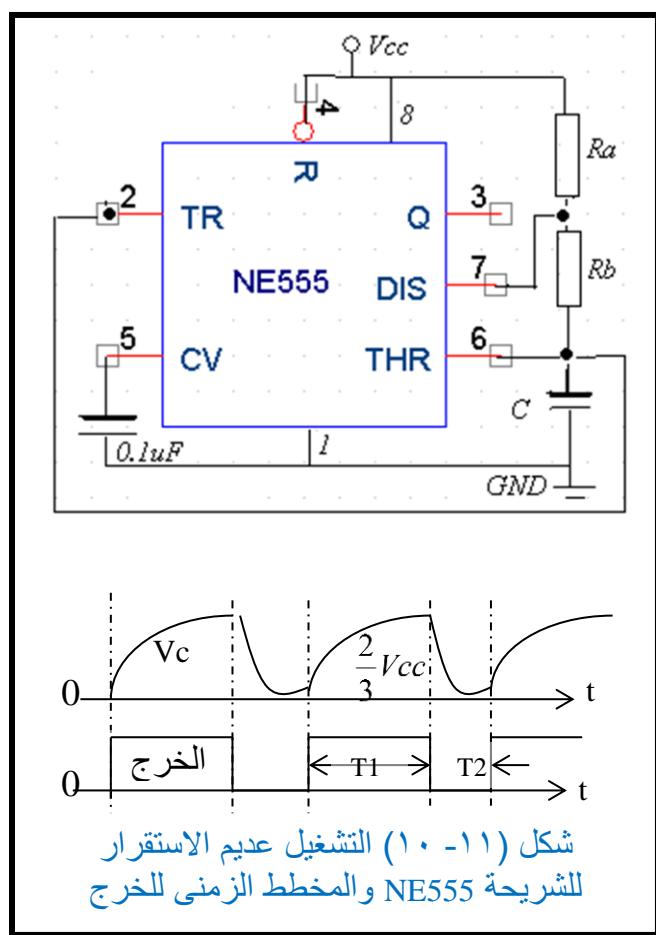

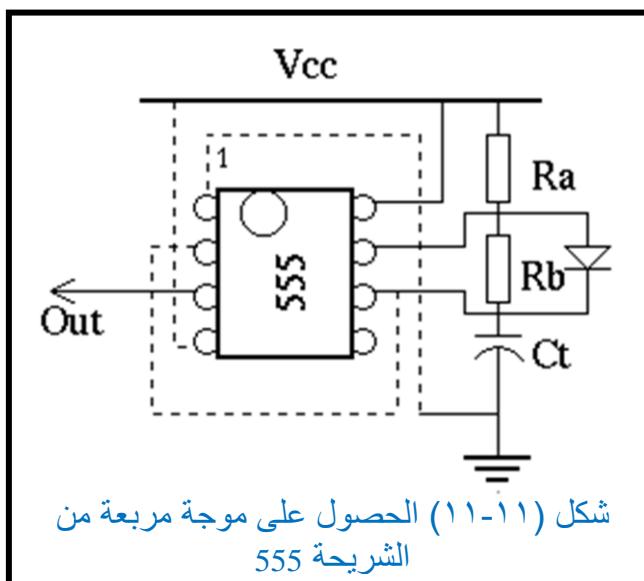

| ٢٠٢ | ٧-١ طريقة التشغيل عديمة الاستقرار                |

| ٢٠٤ | ٨-١ المؤقتات ذات العدادات Timer Counters         |

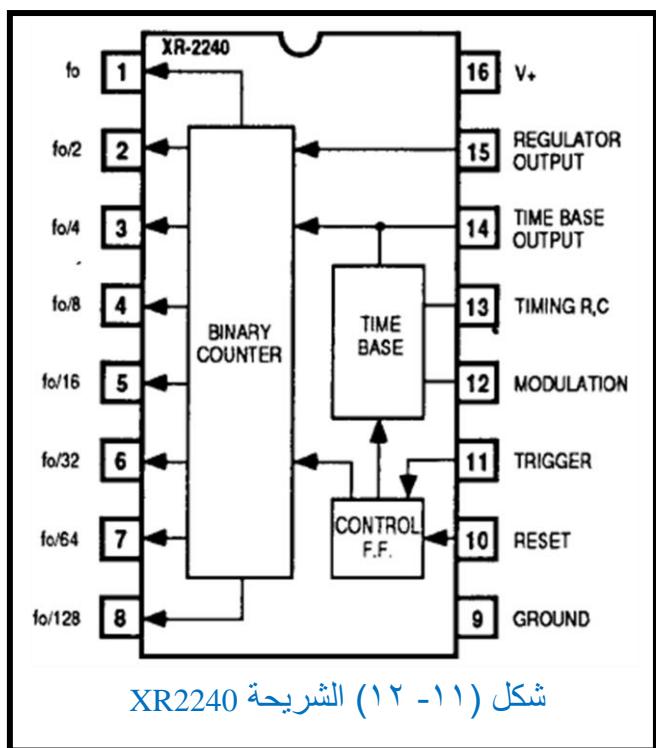

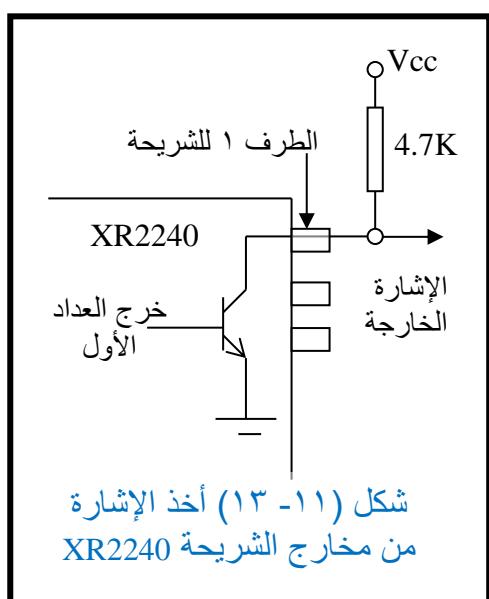

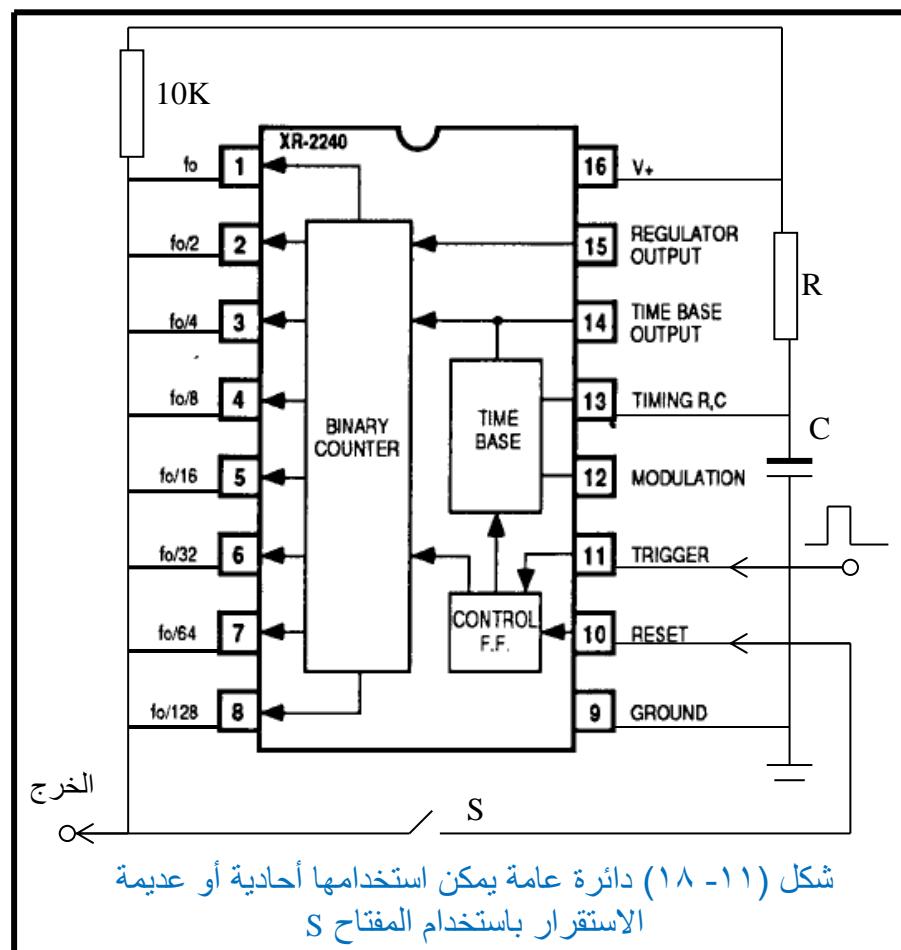

| ٢٠٥ | ٩-١ الشريحة XR2240 المؤقت بعداد Timer Counter    |

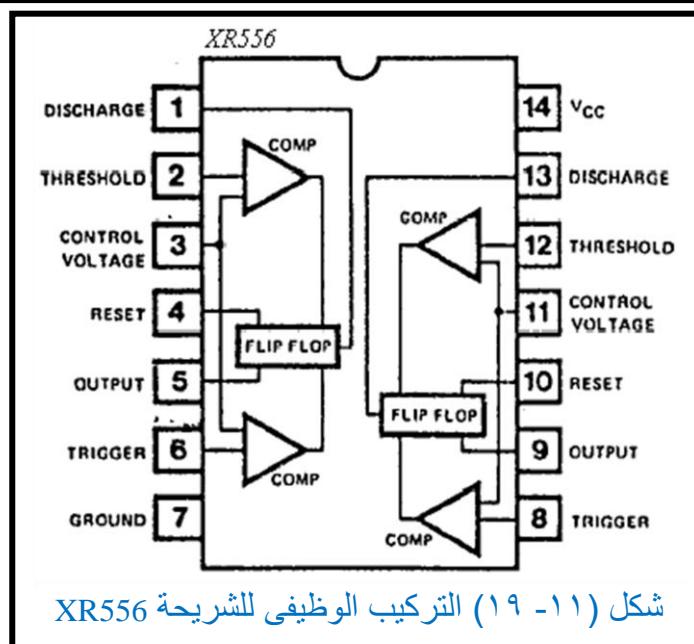

| ٢٠٧ | ١٠-١١ الشريحة XR 556                             |

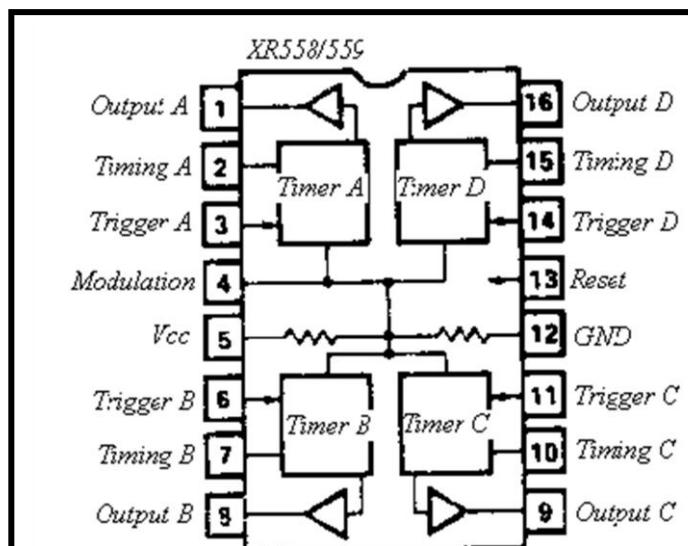

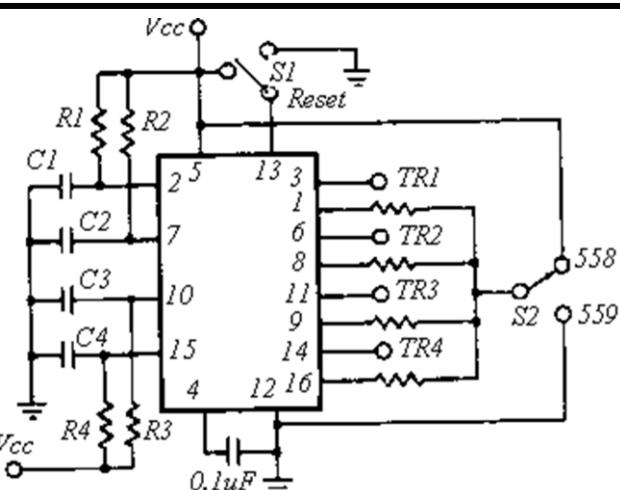

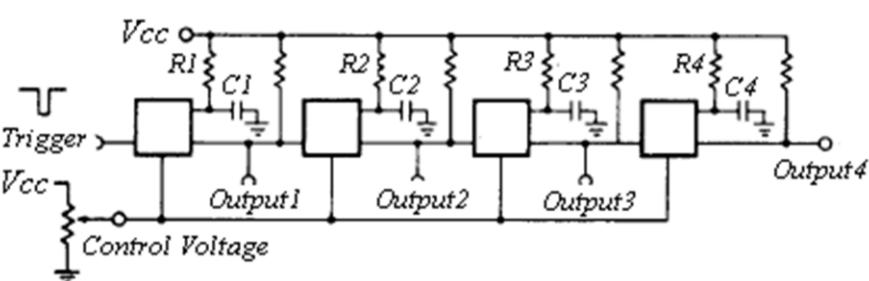

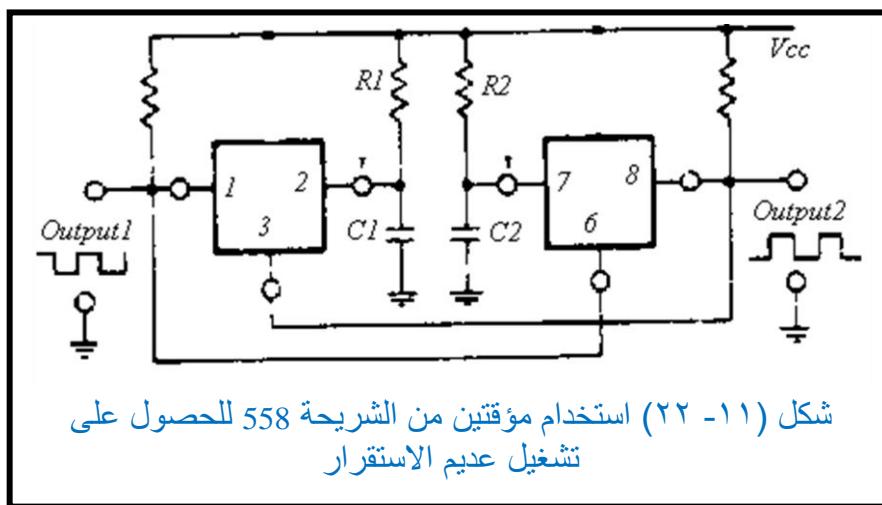

| ٢٠٩ | ١١-١١ الشريحتان 558/559                          |

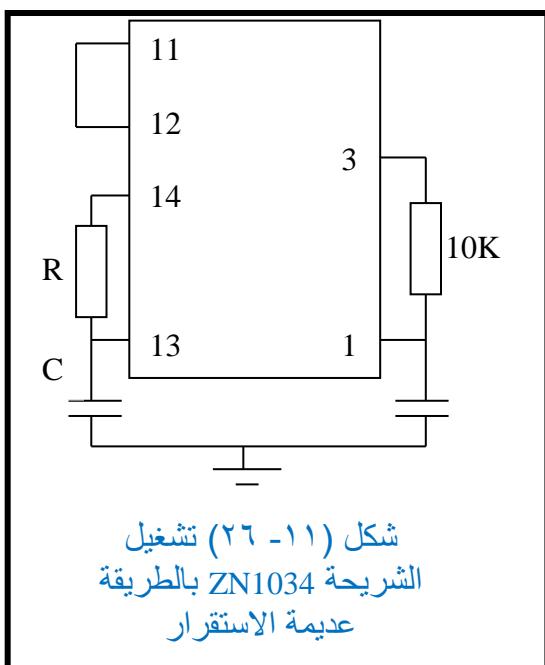

| ٢١١ | ١٢-١١ الشريحة ZN1034                             |

| ٢١٢ | ١٣-١١ تمارين                                     |

**الفصل الثانى عشر: البوابات ثلاثة المنطق Tristate logic gates**

|     |            |

|-----|------------|

| ٢١٤ |            |

| ٢١٥ | ١-١٢ مقدمة |

|     |                                                                      |

|-----|----------------------------------------------------------------------|

| ٢١٥ | ٤-١٢ ما هو المنطق الثلاثي ، ولماذا ؟                                 |

| ٢١٦ | ٣-١٢ الشريحة ٧٤١٢٥ أربع بوابات ثلاثة المنطق                          |

| ٢١٧ | ٤-١٢ الشريحة ٧٤١٢٦ أربع بوابات ثلاثة المنطق                          |

| ٢١٧ | ٥-١٢ الشريحة ٧٤٢٤٠ ثمانية بوابات ثلاثة المنطق                        |

| ٢١٨ | ٦-١٢ الشريحة ٧٤٢٤١ ثمانية بوابات ثلاثة المنطق                        |

| ٢١٨ | ٧-١٢ الشريحتان ٧٤٢٤٢ و ٧٤٢٤٣ أربع بوابات ثلاثة المنطق ثنائية الاتجاه |

| ٢١٨ | ٨-١٢ الشريحة ٧٤٢٤٤ ثمانية بوابات ثلاثة المنطق                        |

| ٢١٩ | ٩-١٢ الشريحة ٧٤٢٤٥ ثمانية بوابات ثلاثة المنطق ثنائية الاتجاه         |

| ٢٢١ |                                                                      |

القاموس

# الفصل الأول

١

أسسیات عامة

General Principles

## ١-١ مقدمة

**سنقدم** في هذا الفصل بعض المعلومات الأساسية التي تحتاجها عادة عند تصميم أي دائرة إلكترونية مثل أنواع المقاومات المتوفرة في السوق وكيفية تصنيفها وكيفية قراءتها ونفس الشيء سيكون بالنسبة للمكثفات. سنعرض أيضاً للأشكال المختلفة للشرايع الإلكترونية وكيفية عد أطراها. بعد ذلك سنعرض للفرق بين الأنظمة الرقمية والأنظمة الانسية أو التماثلية وأهمية استخدام الإشارات والأنظمة الرقمية في عالم من الرقائق نعيشه الآن. سنتختم هذا الفصل بعرض سريع للأجهزة المستخدمة في بناء واختبار الدوائر الإلكترونية.

## ١-٢ المقاومات الكهربية Resistances

### أولاً: المقاومات الثابتة القيمة

شكل (١-١) مقاومات كهربائية مختلفة القدرة من

ربع إلى واحد وات

شكل (٢-١) أحد أشكال المقاومات ذات الوات العالي

توجد المقاومة الكهربائية في أشكال متعددة منها المقاومات الثابتة القيمة والمتغيرة القيمة. توجد المقاومات الثابتة في أحجام كثيرة على حسب القدرة الكهربية لكل مقاومة. القدرة الكهربية يقصد بها حاصل ضرب التيار المار في المقاومة في فرق الجهد الموجود على المقاومة ويكدر ذلك عادة بالوات. توجد مثلاً مقاومات ربع وثلث ونصف وواحد واثنين وات، وأخرى تتحمل أكثر من وات وبالذات المقاومات المكونة من سلك ملفوف والتي تصل قدرها إلى ٢٠٠ وات. تتميز المقاومات ذات الوات العالي بكبير حجمها ويكتب عليها في العادة قيمتها بالأوم والقدرة التي تتحملها. شكل (١-١) يبين بعض هذه المقاومات التي تقدر قدرها بربع وثلث ونصف وواحد وات ابتداء من أصغر مقاومة.

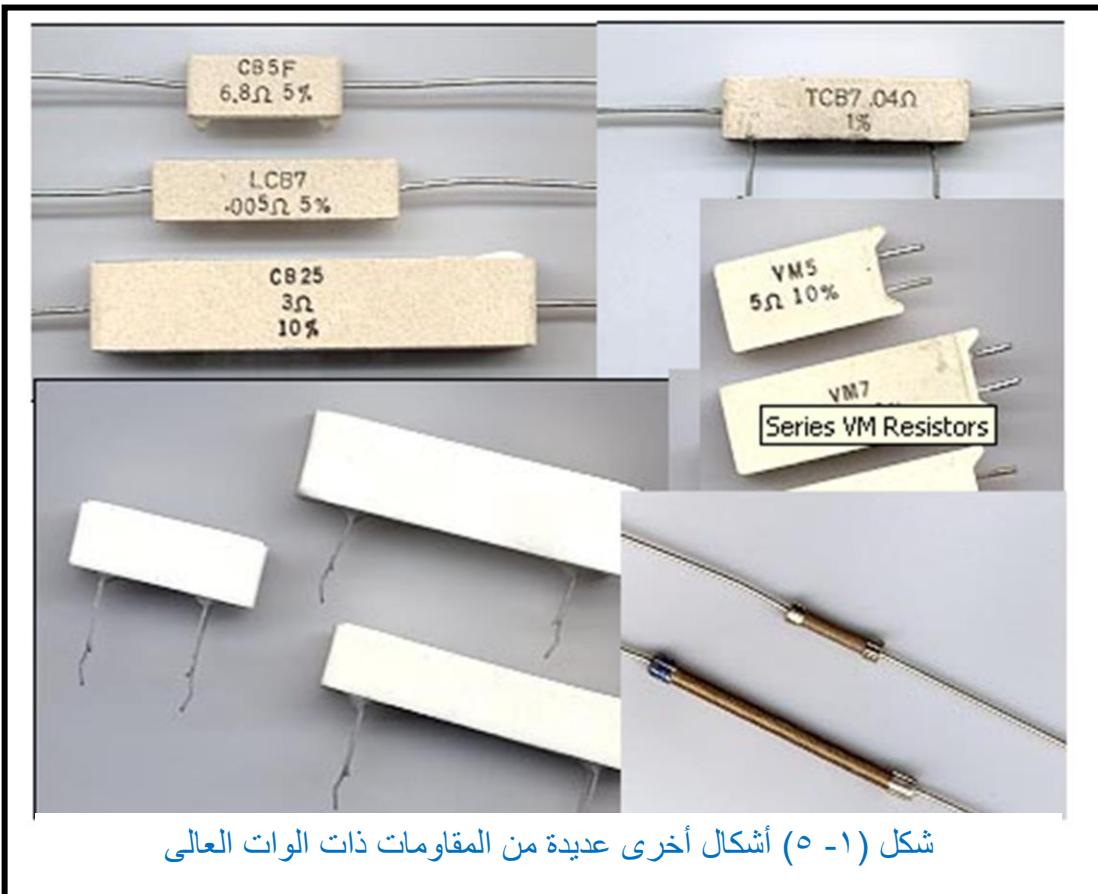

الأشكال (٢-١ و ٣-١ و ٤-١ و ١-٥) تبين أشكالاً مختلفة من المقاومات ذات الوات العالي. تتميز هذه المقاومات بدققتها العالية حيث أنها في العادة تكون

ذات قيمة قليلة. فقيمة هذه المقاومات تبدأ أحياناً من  $1\text{ }\mu\text{A}$  و تصل إلى  $150\text{ }\mu\text{A}$  و هذه قيمة قليلة تحتاج لدقة عالية في التصنيع.

المقاومات الموجودة في شكل (١ - ٣) تتميز بأن لها غالباً معدنها يكون في الغالب من الألومونيوم وذلك للمساعدة في تسريب درجة الحرارة العالية التي من الممكن أن تتولد في المقاومة نفسها. قيم هذه المقاومات تكون مكتوبة عليها في الغالب كما في الشكل.

شكل (١ - ٣) شكل آخر من المقاومات ذات الوات العالى المغلفة بمعدن لزيادة تسرب الحرارة

شكل (١ - ٤) أشكال أخرى للمقاومات ذات الوات العالى

شكل (١ - ٥) أشكال أخرى عديدة من المقاومات ذات الوات العالى

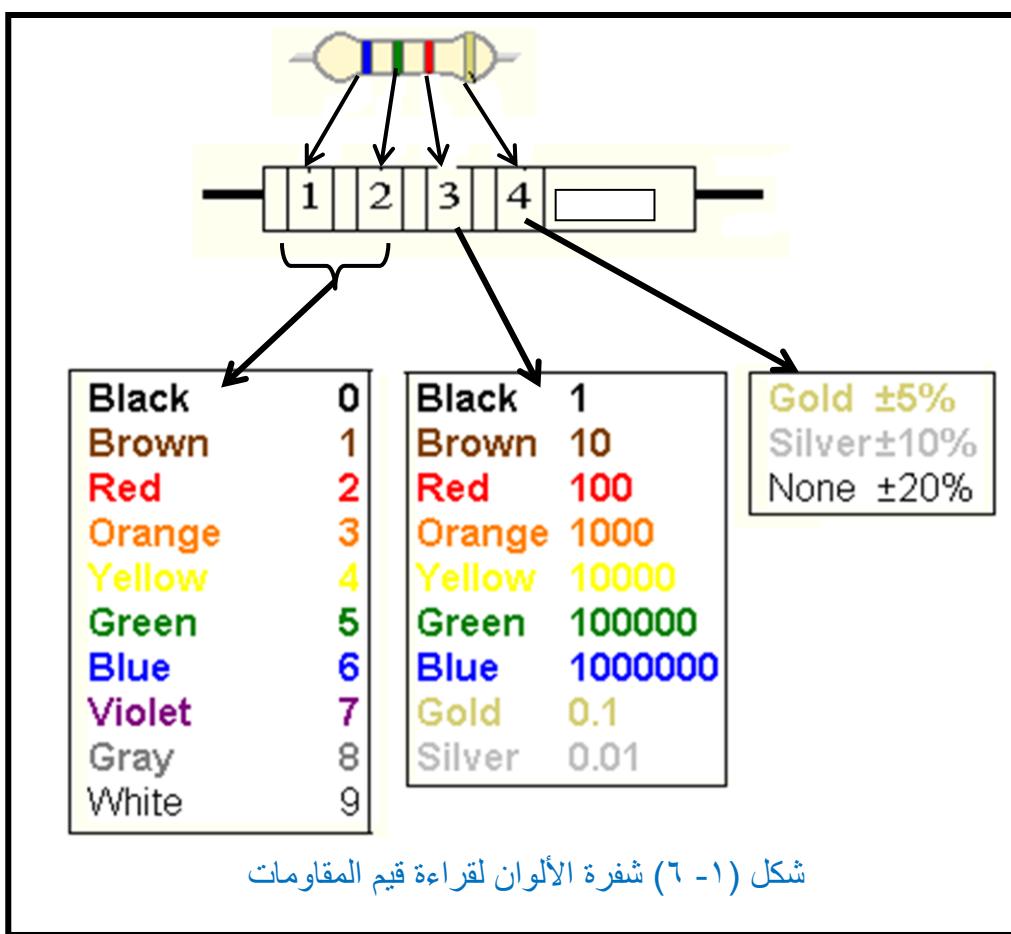

إذا كانت المقاومات ذات الوات العالى مكتوب عليها قيمتها، فماذا عن المقاومات ذات الوات المنخفض كيف نقرأ قيمتها؟ هذه المقاومات تكتب عليها قيمتها بطريقة مختلفة تماماً وفي صورة شفرة من الحلقات الملونة كما في شكل (١ - ٦). تتكون شفرة القيمة لأى مقاومة من ٤ حلقات بألوان مختلفة حول جسم المقاومة كما في شكل (١ - ٦). الحلقتين الأولى والثانية من جهة اليسار تحددان أول رقمين في المقاومة على حسب جدول الألوان الموجود في شكل (١ - ٦). إذا كانت الحلقة الأولى زرقاء كما في الشكل فأول رقم في المقاومة هو ٦، وإذا كانت الحلقة الثانية خضراء كما في الشكل أيضاً، فالرقم الثاني هو ٥. وعلى ذلك فأول رقمين في قيمة هذه المقاومة هما ٦٥. الحلقة الثالثة على جسم المقاومة تحديد عدد الأصفار بعد الرقمين السابقين. فإذا كانت هذه الحلقة حمراء كما في الشكل فإن ذلك يعني أننا يجب أن نضع صفرتين على يمين الرقمين السابقين أو أن نضربهما في مائة لتصبح قيمة المقاومة ٦٥٠٠ أوم أو ٦,٥ كيلوأوم. الحلقة الرابعة على جسم المقاومة تحديد دقة تصنيعها، فاللون الذهبي يعني أن هذه المقاومة مصنوعة بدقة مقدارها ٥٪ أي أن قيمة المقاومة ستكون ٦٥٠٠ أوم زائد أو ناقص ٥٪ من هذه القيمة، وفي حالة عدم وجود حلقة رابعة فإن ذلك يعني أن الدقة هي ٢٠٪ كما هو موضح في شكل (١ - ٦).

بعض المقاومات تحتوى حلقة خامسة على يمين حلقة الدقة. هذه الحلقة تعنى الإعتمادية أو الثقة reliability في هذه المقاومة. شكل (١ - ٧) يبين مثلاً لأحد هذه المقاومات وجدول الألوان الذى يحدد مدى هذه الثقة في المقاومة بعد

تشغيلها ١٠٠٠ ساعة. فمثلاً اللون البرتقالي يعني أن حد الثقة في هذه المقاومة هو ١٪ وهذا يعني أن احتمال أن هذه المقاومة ستفشل في الأداء بعد فترة عمل ١٠٠٠ ساعة هو ١٪، بمعنى آخر أن مقاومة من كل ١٠٠٠ مقاومة تفشل في الأداء بعد فترة عمل مقدارها ١٠٠٠ ساعة. هناك ٤ ألوان فقط لتمثيل حد الثقة في المقاومة وهي البنى والأحمر والبرتقالي والأصفر كما في شكل (١-٧) حيث نلاحظ أنها آخر حلقة من ناحية اليمين على جسم المقاومة. كلمة أخيره نقولها هنا وهي أنه عند مسك المقاومة بين أصابعك لتقرأ قيمتها، دائماً إبحث عن حلقة الدقة أولاً التي تكون

ذهبية أو فضي واجعلها ناحية اليمين ثم ابدأ في قراءة الحلقات من اليسار كما أشرنا. إذا كانت هذه المقاومة لا تحتوى حلقة للدقة فاجعل المساحة الفاصلة من جسم المقاومة التي لا تحتوى حلقات ألوان ناحية اليمين ثم ابدأ.

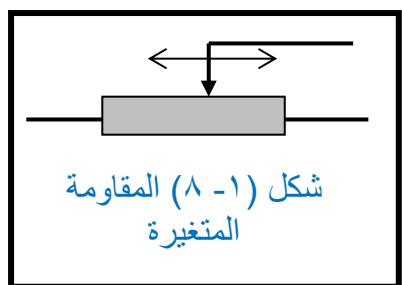

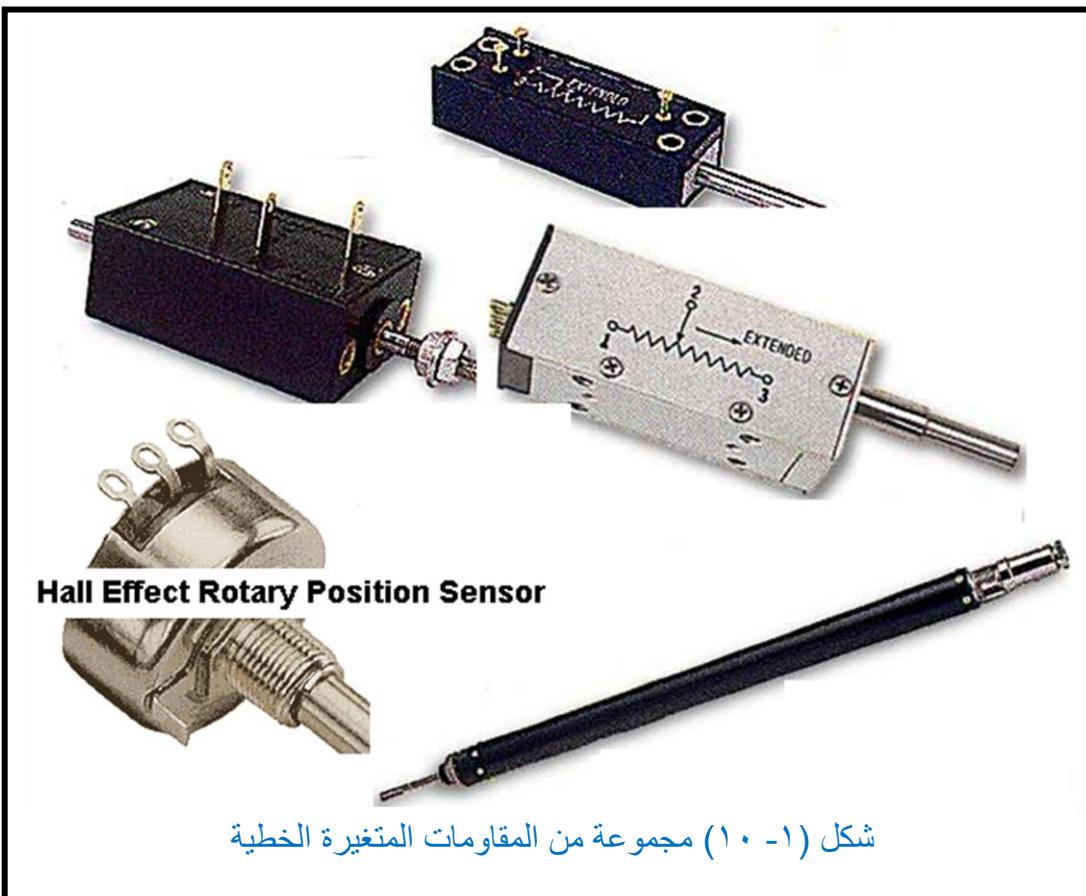

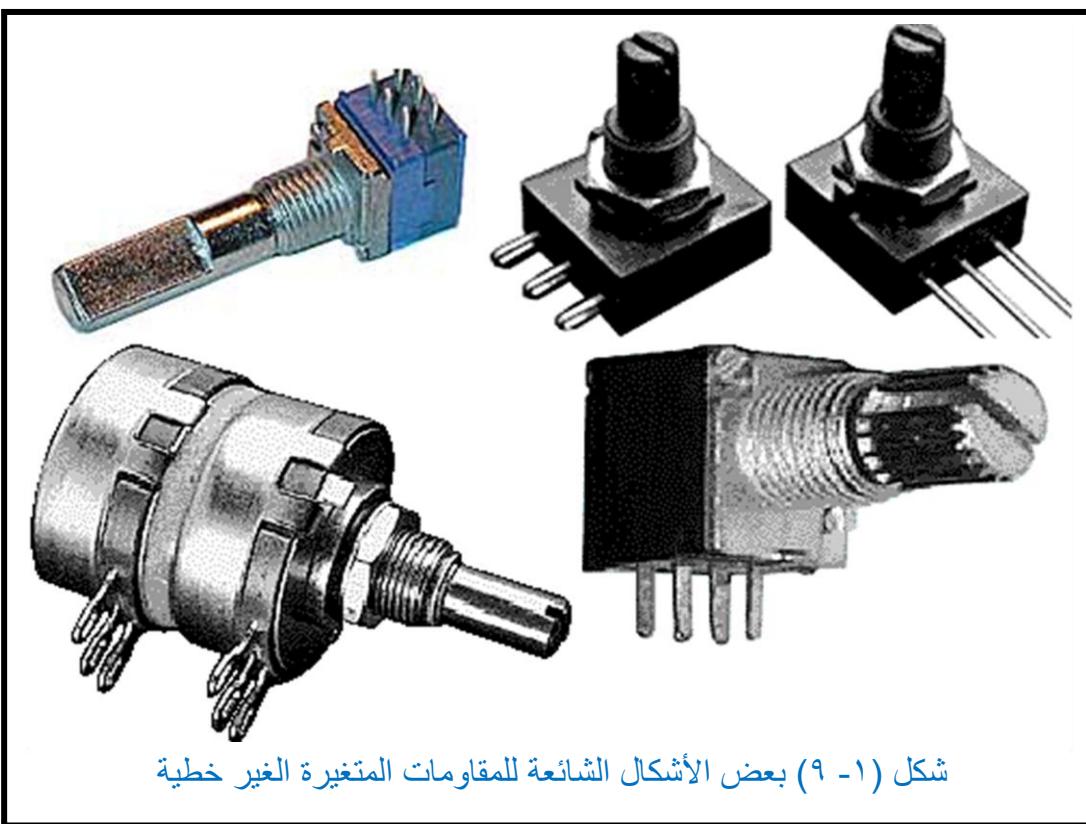

توجد المقاومات المتغيرة في أشكال وقيم عديدة وفي الغالب تكون الأشكال مناسبة لطبيعة الوضع أو المكان الذي تستخدم فيه هذه المقاومة. فمقاومة التحكم في شدة الصوت مثلاً تختلف في الشكل عن مقاومة التحكم في سرعة مотор من حيث الشكل فقط. المقاومات المتغيرة تكون عبارة عن طرف منزلي يتحرك بين طرفين ثابتين كما في شكل (١-٨). العلاقة بين حركة المنزلي والتغير الحادث في قيمة المقاومة تكون خطية أو غير خطية. في حالة العلاقة غير الخطية فإن التغير في قيمة المقاومة لا يقابل تغير خطى في حركة منزلي المقاومة وهذا هو النوع الشائع من المقاومات المتغيرة وهي رخصة الشمن. النوع الثاني من المقاومات المتغيرة هو النوع الخطى والذي يعني أن أي تغير في حركة المنزلي يعطى تغير في قيمة المقاومة متناسب خطياً مع هذه الحركة. هذا النوع أغلبى سعراً من النوع السابق ويستخدم في التطبيقات التي تحتاج لتغييرات دقيقة في قيمة المقاومة. شكل (١-٩) يبين العديد من الأشكال المتاحة في السوق من المقاومات المتغيرة. شكل (١-١٠) يبين مجموعة من المقاومات الخطية. هناك أشكال عديدة أخرى لا يتسع المكان لحصرها هنا.

## ثانياً: المقاومات المتغيرة

### Potentiometer

توجد المقاومات المتغيرة في أشكال وقيم عديدة وفي الغالب تكون الأشكال مناسبة لطبيعة الوضع أو المكان الذي تستخدم فيه هذه المقاومة. فمقاومة التحكم في شدة الصوت مثلاً تختلف

في الشكل عن مقاومة التحكم في سرعة مotor من حيث الشكل فقط. المقاومات المتغيرة تكون عبارة عن طرف منزلي يتحرك بين طرفين ثابتين كما في شكل (١-٨). العلاقة بين حركة المنزلي والتغير الحادث في قيمة المقاومة تكون خطية أو غير خطية. في حالة العلاقة غير الخطية فإن التغير في قيمة المقاومة لا يقابل تغير خطى في حركة منزلي المقاومة وهذا هو النوع الشائع

من المقاومات المتغيرة وهي رخصة الشمن. النوع الثاني من المقاومات المتغيرة هو النوع الخطى والذي يعني أن أي تغير في حركة المنزلي يعطى تغير في قيمة المقاومة متناسب خطياً مع هذه الحركة. هذا النوع أغلبى سعراً من النوع السابق ويستخدم في التطبيقات التي تحتاج لتغييرات دقيقة في قيمة المقاومة. شكل (١-٩) يبين العديد من الأشكال المتاحة في السوق من المقاومات المتغيرة. شكل (١-١٠) يبين مجموعة من المقاومات الخطية. هناك أشكال عديدة أخرى لا يتسع المكان لحصرها هنا.

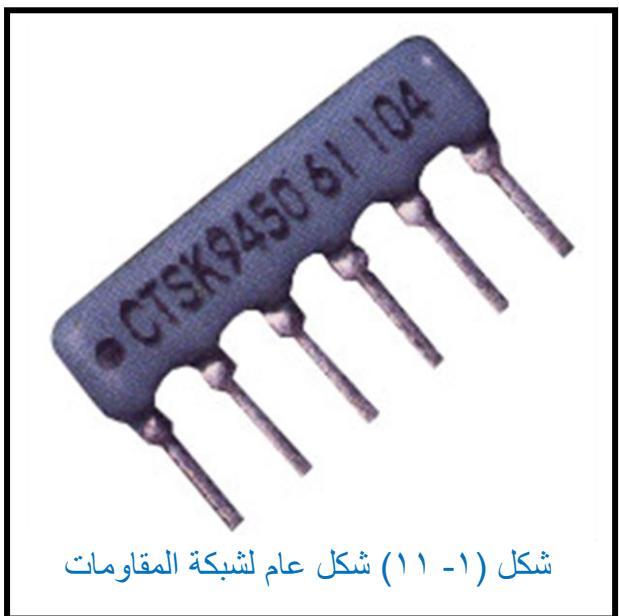

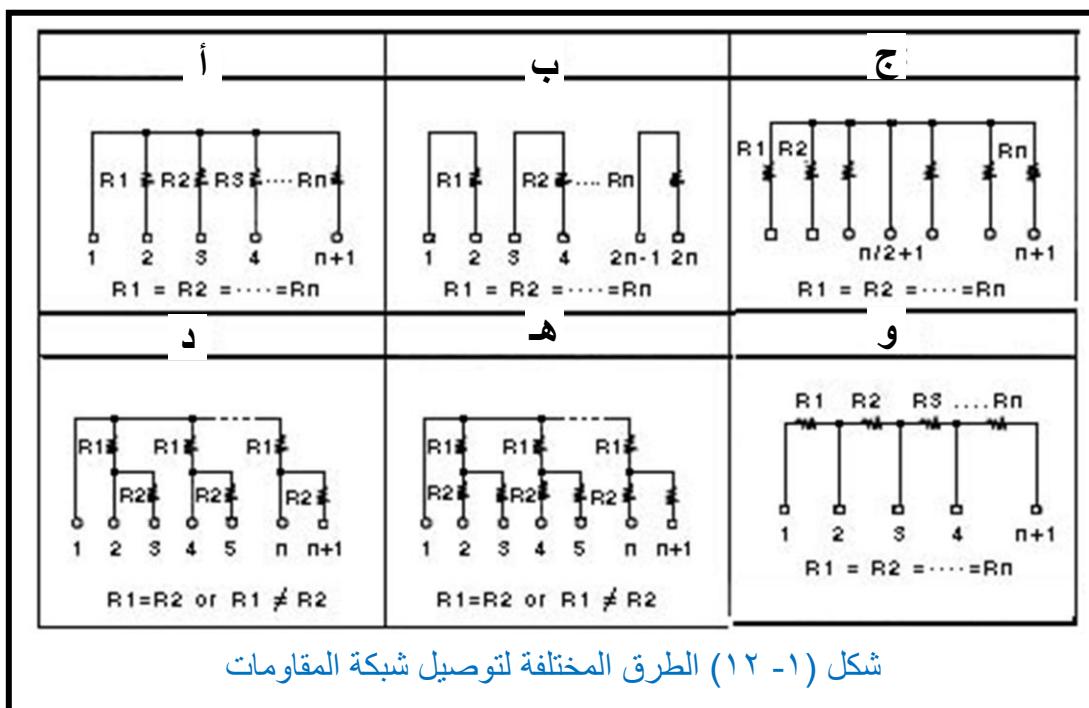

### ثالثاً: شبكة المقاومات Resistor Network

شبكة المقاومات كما في شكل (١١ - ١) تحتوى عدد من المقاومات المتساوية الموصولة مع بعضها بطريقة معينة داخل نفس المحتوى. شكل (١٢ - ١) يبين الطرق المختلفة لتوصيل هذه المقاومات مع بعضها داخلياً. شكل (١٢ - ١أ) مثلاً يبين توصيل كل المقاومات في نقطة واحدة عامة والطرف الثانى لكل مقاومة والطرف العام تخرج كأطراف من المحتوى. شكل (١٢ - ١ب) يبين أن كل مقاومة تم إخراج طرفيها من المحتوى. حاول دراسة باقى طرق التوصيل في شكل (١٢ - ١) للتعرف على الطرق المختلفة الأخرى للتوصيل. ثوّكد هنا على أن كل المقاومات داخل الشبكة تكون متساوية. تستخدم

شبكة المقاومات في الكثير من التطبيقات التي تتطلب هذه المقاومات مثل توصيل مقاومات على التوالى مع مجموعة من الديودات المضيئة LED.

شكل (١٣ - ١) يبين صوراً لمقاومات متغيرة تستخدمن في بعض الأغراض الخاصة مثل التحكم في الصواريخ وسفن الفضاء والأزرع الآلية (الروبوت) حيث تكون هذه المقاومات متناهية الدقة.

شكل (١٣ - ١) صور كثيرة للمقاومات المتغيرة المستخدمة لأغراض خاصة

### ٣- المكثفات الكهربائية Capacitors

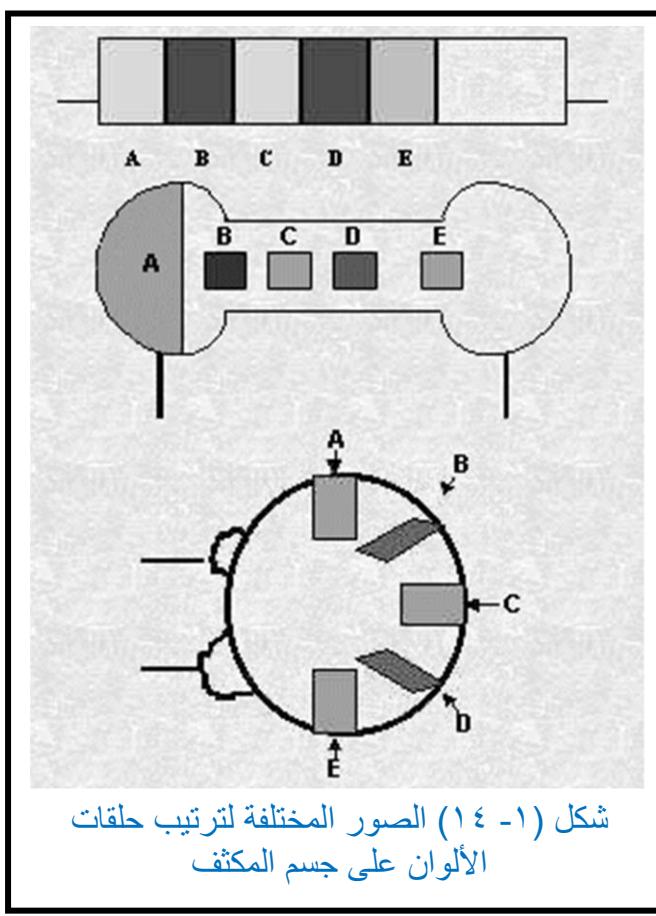

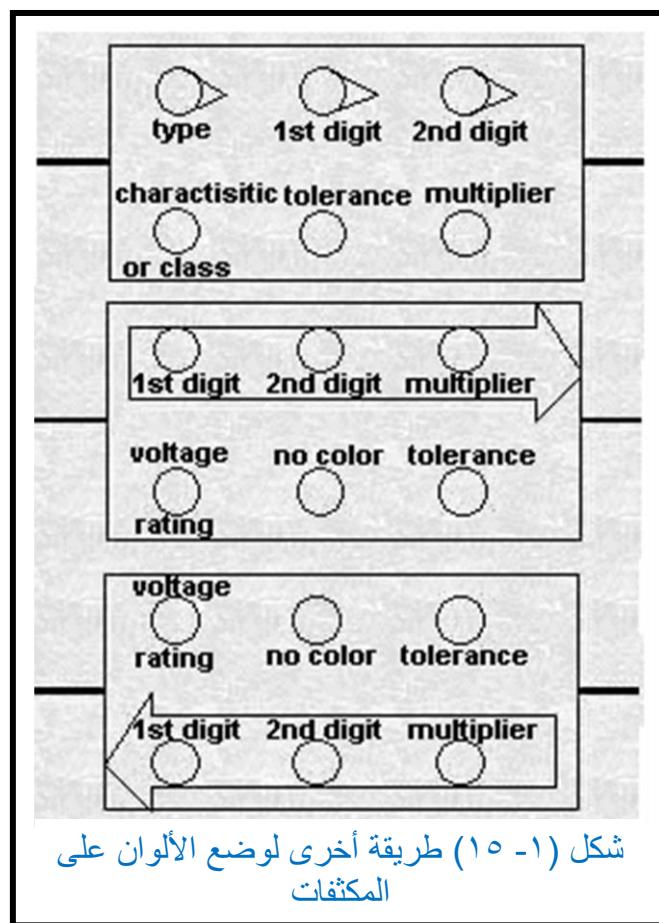

شكل (١٤ - ١) الصور المختلفة لترتيب حلقات الألوان على جسم المكثف

توجد المكثفات الكهربائية في الكثير من الأشكال ومنها الثابت القيمة والمتغير ويتم تصنيفها بطرق عديدة، فهـي إما أن تصنـف على حـسب فـرق الجـهد الذـي يمكن أن تـتحملـهـ، أو عـلـى حـسب طـرـيقـةـ التـصـنـيـعـ. قـيـمةـ المـكـثـفـ إـمـاـ أنـ تـكـتبـ عـلـىـ جـسـمـ المـكـثـفـ إـذـاـ كانـ الـوـضـعـ يـسـمـحـ بـذـلـكـ أـوـ يـتـمـ قـرـاءـهـاـ عـنـ طـرـيقـةـ شـفـرـةـ أـلـوـانـ كـمـاـ كـانـ يـحـدـثـ فـيـ حـالـةـ قـرـاءـةـ قـيـمةـ المـقـاـوـمـاتـ. شـكـلـ (١٤ - ١)ـ يـبـينـ طـرـيقـةـ تـرـتـيبـ أـلـوـانـ عـلـىـ جـسـمـ المـكـثـفـ حـسـبـ شـكـلـهـ. كـمـاـ فـيـ الشـكـلـ نـجـدـ أـنـ هـنـاكـ ٥ـ حـلـقـاتـ أـوـ ٥ـ أـلـوـانـ وـهـنـهـ أـلـوـانـ يـتـمـ تـمـيـزـهـاـ بـالـحـرـفـ A, B, C, D, Eـ مـنـ الـيـسـارـ كـمـاـ فـيـ شـكـلـ (١٤ - ١).ـ الـحـرـفـ Aـ يـمـثـلـ الـعـامـلـ الـحـارـىـ لـلـمـكـثـفـ،ـ أـىـ مـقـدـارـ التـغـيـرـ فـيـ قـيـمـتـهـ نـتـيـجـةـ التـغـيـرـ فـيـ درـجـةـ الـحـرـاءـ.ـ الـحـرـفـ Bـ هـوـ الـرـقـمـ الـأـوـلـ مـنـ الـقـيـمـةـ.ـ الـحـرـفـ Cـ يـمـثـلـ الرـقـمـ

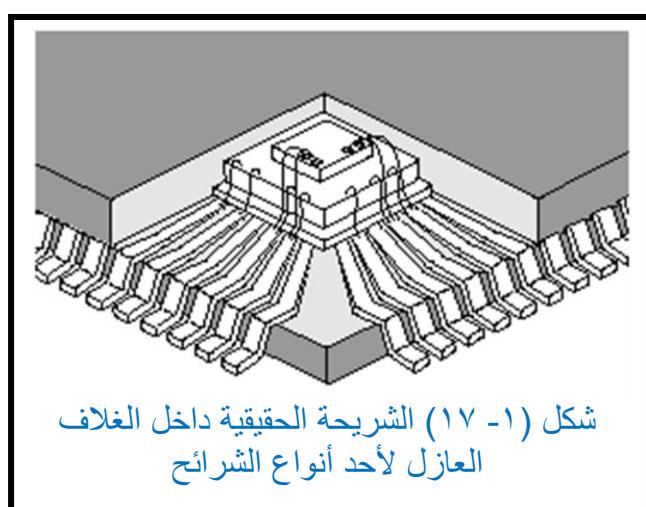

الثاني من القيمة. الحرف D يمثل معامل الضرب أو بمعنى آخر عدد الأصفار. الحرف E يمثل الدقة في قيمة المكثف. القيمة المحسوبة من هذه الشفرة تكون بالبيكوفاراد PF. القيمة العددية لكل لون هي نفس القيم المستخدمة مع المقاومات كما في شكل (١-٦). عدد الألوان على جسم المكثف من الممكن أن يكون ثلاثة أو ستة وفي كل حالة تبقى الشفرة كما هي. شكل (١-١٥) يبين طريقة أخرى لوضع الألوان على جسم المكثف حيث توضع في صورة دوائر كما في الشكل وترتبط ببعضها البعض بحسب المكثف كما في الشكل أيضاً. هناك ٣ دوائر مهمة، الأولى والثانية تمثل الرقم الأول والثانية والدائرة الثالثة تمثل عدد الأصفار التي توضع على عين الرقمن السابقين كما كان الحال مع كود المقاومات. شكل (١-١٦) يبين بعض الصور المختلفة والشائعة للمكثفات.

## ٤-٤ الدوائر التكاملية ICs

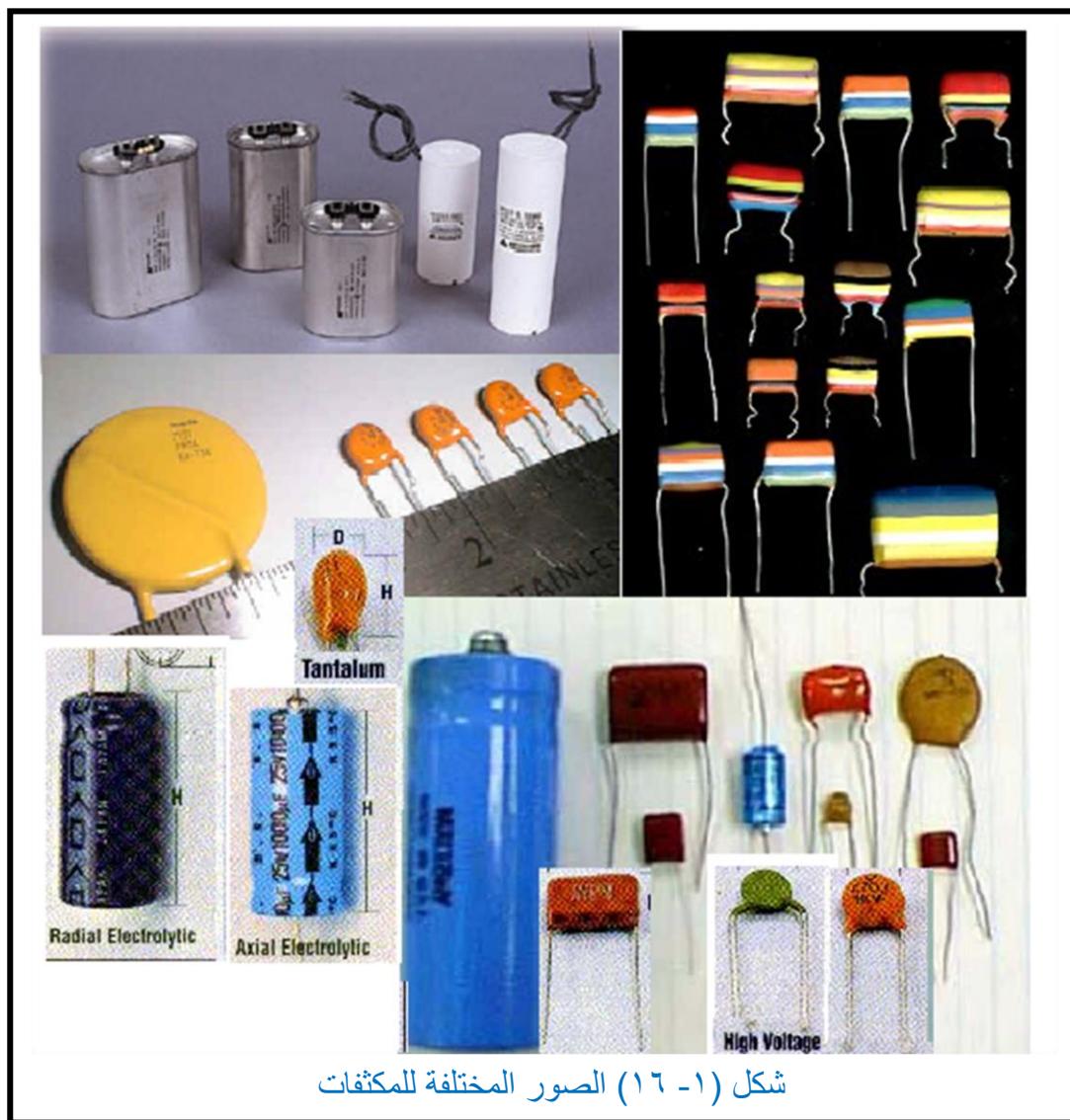

كل واحدة من الدوائر المنطقية التي سنتكلم عنها في هذا الكتاب متاحة في صورة شرائح إلكترونية. من مميزات وضع هذه الدوائر في شرائح إلكترونية أنها ستكون صغيرة الحجم ورخيصة الثمن يمكن الاعتماد عليها في الكثير من ظروف التشغيل reliable، كما أن معظم هذه الشرائح تستهلك القليل من القدرة الكهربائية. لذلك لزم علينا أن نعرض للأشكال المختلفة للشرائح الإلكترونية المتاحة في الأسواق وكيفية قراءة وترتيب أطراف هذه الشرائح حتى نستطيع التعامل معها معملياً.

الكثير منا ينظر إلى الحجم الأسود لأى شريحة على أن هذا هو حجم الشريحة الأصلى، ولكن الحقيقة هى أن هذا الجسم الأسود يكون عادة من مادة عازلة تغطى أو تعلق الجسم الحقيقي للشريحة الموجود بالداخل وهذا الجسم في العادة يكون صغيرا جدا بالنسبة لهذا الغلاف الأسود الموجود فقط لكي يتمكن المصنع من إخراج الأطراف المختلفة للشريحة بطريقة مريحة للمستخدم. شكل (١٧-١) يوضح ذلك.

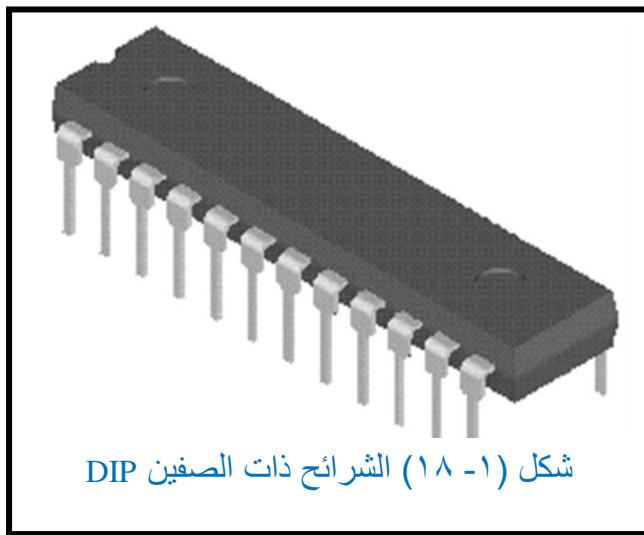

هناك أكثر من طريقة لتغليف الشرائح الإلكترونية، أولها وأكثرها شيوعا هي الشرائح ذات الأطراف النافذة أو الخارمة. في هذه الحالة لابد من عمل خرم أو فتحة لكل طرف من أطراف الشريحة على اللوحة ينفذ منها الطرف ويتم لحامة أو

ثبيته من الناحية الأخرى لللوحة الثبيرة. أى أن الشريحة تكون موجودة على أحد أوجه اللوحة والأطراف مثبتة على الوجه الآخر لها. من الأشكال الشائعة لذلك الشريحة المعروفة بذات الصفين النافذة Dual In line Package، DIP الموضحة في شكل (١٨ - ١).

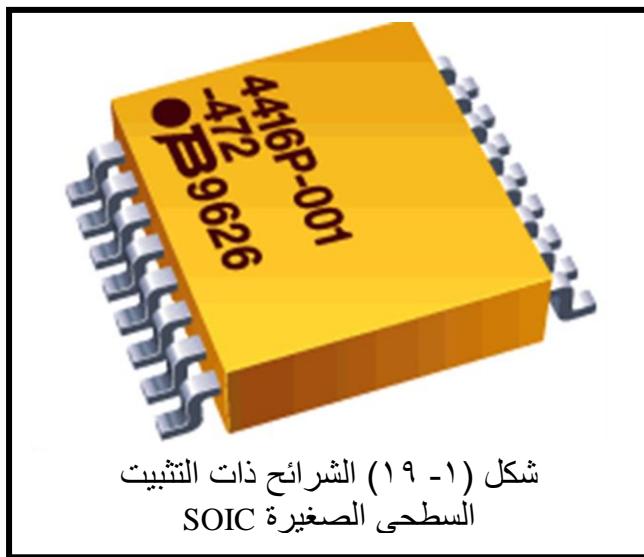

النوع الثاني من الشرائح هو الشريحة السطحية أو غير النافذة وهي لا تحتاج لتخريم اللوحة لثبيتها ولكنها تثبت مباشرة على نفس السطح الموجودة عليه. وهذه بالطبع تكون أفضل في

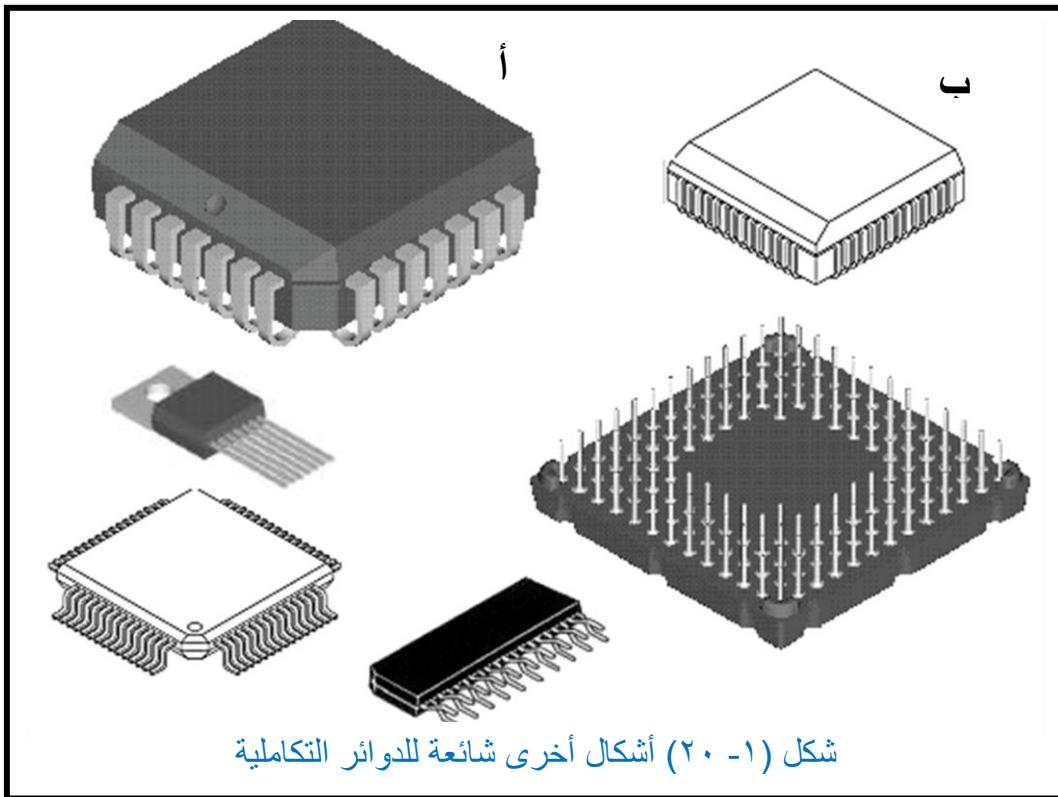

الكثير من التطبيقات لأنها ستتوفر مساحة على اللوحة كما أنها في العادة تكون صغيرة الحجم. هذه الشريحة تسمى الشريحة السطحية الصغيرة Small Outline IC، SOIC. شكل (١٩ - ١٩) يوضح مثالاً لهذا النوع من الشرائح. هناك أشكال عديدة من الشريحة السطحية مثل الشريحة ذات الأرجل السلكية Plastic Leaded Chip Carrier،

PLCC والتي تكون أطرافها عبارة عن أسلاك ملفوفة تحت جسم الشريحة في صورة الحرف J كما في شكل (١ - ٢٠). هناك أيضاً الشريحة السيراميكية التي تكون أطرافها عبارة عن أسلاك لاصقة في جسم الشريحة كما Ceramic Chip Carrier، LCCC في شكل (١ - ٢٠ ب)، كما أن هناك أيضاً العديد من الأشكال الأخرى الموضحة بعضها في شكل (١ - ٢٠).

شكل (١٨ - ١) الشريحة ذات الصفين DIP

شكل (١٩ - ١٩) الشريحة ذات التثبيت السطحي الصغيرة SOIC

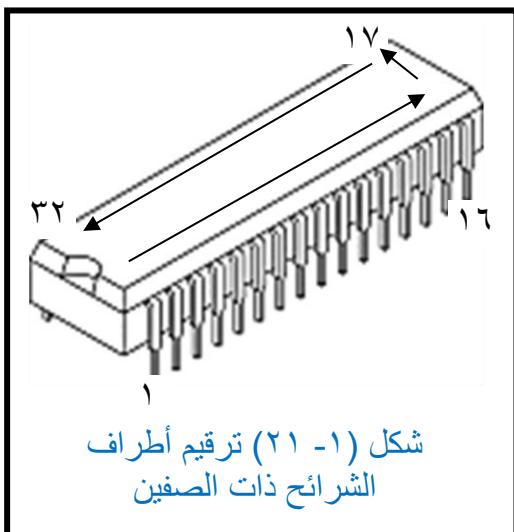

### ترقيم أطراف الشريحة التكاملية

في العادة تكون هناك علامة على سطح أي شريحة تشير إلى الطرف رقم ١. نمسك بالشريحة أفقياً والسطح لأعلى والعلامة ناحيتها ثم نبدأ عد الأطراف متوجهين ناحية اليمين حتى آخر الصف ثم نلف للصف المقابل ونستمر في العد متوجهين ناحية اليسار كما في شكل (١ - ٢١). بنفس الطريقة مع جميع أشكال الشريحة التي رأيناها، نحدد الطرف ١، نعد متوجهين ناحية اليمين مع جميع أطراف الشريحة دورانيا حتى ننتهي عند الطرف المقابل للطرف ١. حاول أن تطبق ذلك مع الشريحة الموجودة في شكل (١ - ٢٠) وبالذات الشريحة في شكل (١ - ٢٠) حيث علامة الطرف ١ موجودة في منتصف صف وليس في أحد الأركان كما تعودنا.

### كثافة المكونات على الشريحة

أحياناً تصنف الشرائح الإلكترونية على حسب كثافة المكونات عليها حيث تقام هذه الكثافة بعدد الترانزستورات المكونة لهذه الشريحة. لاحظ أن جميع مكونات أي شريحة تؤول في النهاية إلى مجموعة من الترانزستورات. من هذه التصنيفات ما يلي:

#### ١- الشرائح ذات التكامل الصغير Small Scale Integration, SSI

وهي الشريحة التي تحتوى أقل من ١٠٠ ترانزستور، وهذه تحوى بعض البوابات المنطقية والقلايدات.

#### ٢- الشرائح ذات التكامل المتوسط Medium Scale Integration, MSI

وهي التي تحتوى من ١٠٠ حتى ١٠٠٠٠ ترانزستور، ويتكون منها العدادات والمسجلات والمشفرات وملحلاطات الشفرة.

#### ٣- الشرائح ذات التكامل العالى Large Scale Integration, LSI

وهي التي تحتوى من ١٠٠٠٠٠ ترانزستور، ويكون منها شرائح الذاكرة والأجيال الأولى من المعالجات.

٤- الشرائح ذات التكامل العالى جدا **Very Large Scale Integration, VLSI** وهى التي تحتوى

من ١٠٠٠٠٠ ترانزستور، ويتكون منها الأجيال المتوسطة من المعالجات وشريحة الذاكرة.

٥- الشرائح فائقة التكامل **Ultra Large Scale Integration, ULSI** وهى التي تحتوى فوق المليون

ترانزستور. الأجيال الأخيرة من المعالجات حتى كتابة هذا الكتاب وصلت كثافتها حتى ٥٠ مليون ترانزستور.

## ١-٥ الإشارات الانسية أو التماثلية والإشارات الرقمية

### Analog and digital signals

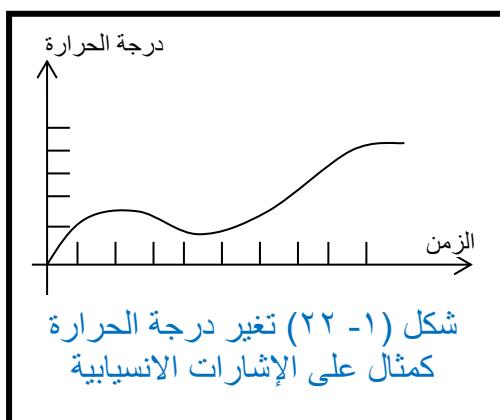

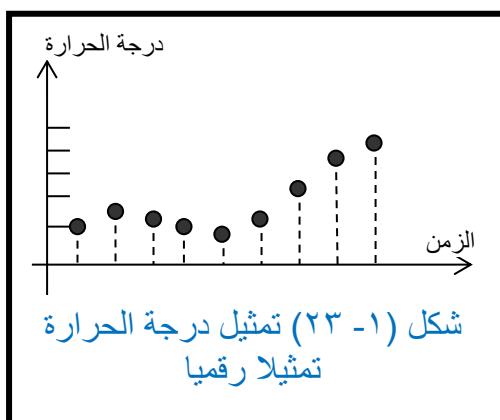

توجد الإشارات الكهربائية في واحدة من صورتين، إما الصورة الانسية (التماثلية كما يطلق عليها أحياناً) أو الصورة الرقمية. الإشارة الانسية هي الإشارة التي تتغير قيمتها بصورة انسية من قيمة إلى قيمة مارة بجميع القيم الممكنة بين القيمتين. كمثال على ذلك درجة حرارة الجو التي تتغير قيمتها بين قيمة صغيرة (٢٠ درجة مثلاً) وقيمة كبيرة (٣٥ درجة مثلاً). عندما تتغير درجة الحرارة من ٢٠ إلى ٣٥ درجة فإنها تمر بجميع القيم الممكنة بين هاتين القيمتين مثل ٢٠,٠٠١ و ٢٠,٠٠٠١ و ٢٢,٠٠٠١ و ٣٣,٥٥٠٥ وهكذا. أى أن درجة الحرارة تناسب من قيمة إلى قيمة أخرى بحيث أنها لابد أن تأخذ أى قيمة تخطر على بالك في المدى الذي تتغير فيه. شكل (١-٢٢) يبين تغير هذه الإشارة مع الزمن. لاحظ أن هذه الإشارة انسية من حيث القيمة كما رأينا ، كما أنها انسية في الزمن أيضاً، فهذه الدالة يمكن أن تكون لها قيمة معينة عند أى زمن يخطر على بالك أيضاً.

تخيل أننا بدأنا نأخذ درجة الحرارة عند فترات زمنية متساوية

ومحددة، كل نصف ساعة مثلاً. كما أنها سنقرأ درجة الحرارة عند كل زمان في صورة رقم صحيح وخانة عشرية واحدة فقط. أى أن درجة الحرارة ستكون مثلًا ٢٠ و ٢٢,١ و ٢٥,٩ و ٣٣,٤ و ٢٥,٩ وهكذا. هذا التمثيل لدرجة الحرارة نقول عنه أنه تمثيلاً رقمياً وهذه الإشارة نقول عنها أنها إشارة رقمية. شكل (١-٢٣) يبين هذه الإشارة. بمجرد تحويل الإشارة الانسية إلى رقمية تصبح كل عينة من العينات الواضحة في شكل (١-٢٣) عبارة عن رقم يوضع في العادة في الصورة الثنائيّة المكونة من وحaid وأصفار. بالرغم من أن كل الإشارات الطبيعية (درجة الحرارة والصوت والضغط وشدة الإضاءة وغيرها الكثير) موجودة في الصورة الانسية إلا أنه يمكن وضعها في الصورة الرقمية تمهدًا لإدخالها إلى الحاسوب حتى يمكن معالجتها رقمياً بالحاسوب وتخزينها في صورة رقمية على أى وسط من أوساط التخزين. كلنا نرى الآن الصوت وقد تم تخزينه في الحاسوب بحيث يمكن استرجاعه في أى وقت. كذلك إشارة الصورة فهناك الأفلام والأغانى المسجلة على ذاكرة

الحاسب أو على أقراص مدججة. هناك طرق عديدة لتحويل الإشارات من الصورة الانسيابية إلى الرقمية والعكس ولكن هذا الموضوع ليس هو المناسب لشرحها لأنها تحتاج لخلفيات لم يتم دراستها حتى الآن.

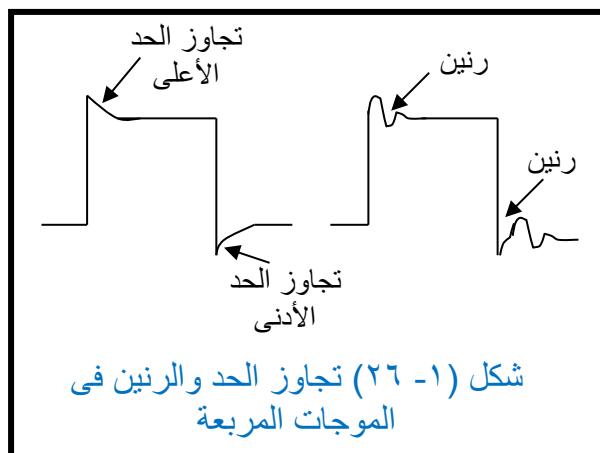

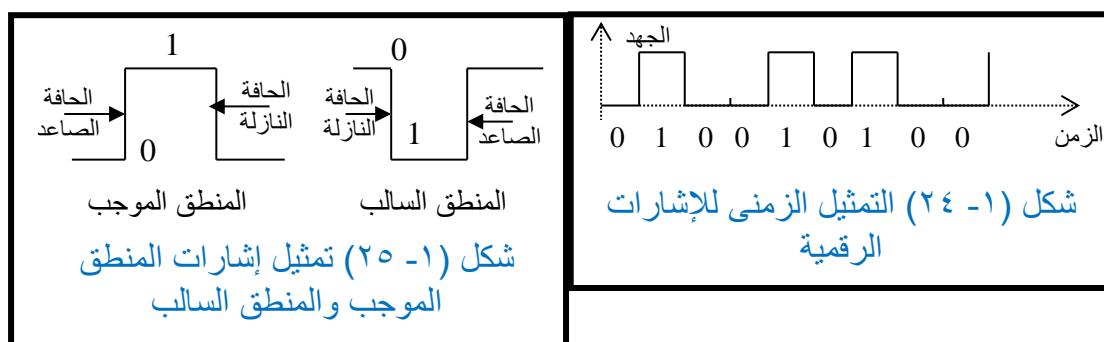

بعد تحويل أي إشارة إلى الصورة الرقمية (وحاید وأصفار) فإنها كإشارة جهد تأخذ مستويين فقط، مستوى يحدد الواحد، ومستوى يحدد الصفر. بذلك تصبح الإشارة الرقمية مع الزمن في صورة موجة مربعة كما في شكل (٢٤). بعض الأنظمة الرقمية تخصص الجهد الأعلى للواحد والجهد الأقل للصفر، وهذه الأنظمة تسمى أنظمة المنطق الموجب positive logic كما أن بعض الأنظمة تخصص الجهد الأعلى للصفر والجهد الأقل للواحد وتسمى أنظمة المنطق السالب negative logic كما في الشكل (٢٥). لاحظ الحافة الصاعدة والحافة النازلة في كل حالة.

من الأشياء الغير مرغوب فيها التي يمكن أن تحدث مع الموجات المربعة هو تجاوز الحدود عند الحافة الصاعدة أو النازلة والرنين أيضا الذي يكون عبارة عن موجة حبيبة تموت بعد فترة زمنية كما في شكل (٢٦ - ١). هذه العيوب تظهر في العادة نتيجة وجود مكثفات طفيلية غير مرغوب فيها في الدائرة.

## ٦ - الأجهزة المستخدمة لاختبار الدوائر الرقمية

سنعرض هنا سريعا لبعض الأجهزة الكثيرة الاستخدام في اختبارات وقياسات الإشارات عموما والرقمية بالذات، ونؤكّد على أننا لن نشرح هذه الأجهزة بالتفصيل لأن المكان المخصص لذلك هو مقرر قياسات ولكننا سنعرض شرعا سريعا مع صورة تبين كل واحد من هذه الأجهزة.

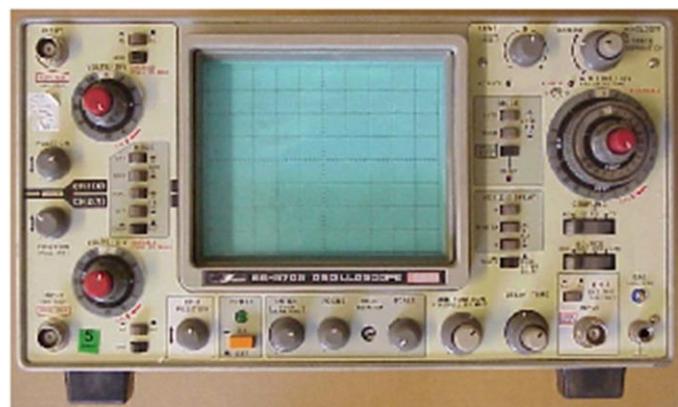

### مبين الذبذبات (الأوسولوسكوب) Oscilloscope

يعتبر الأوسولوسكوب من أكثر أجهزة القياس استخداما في معامل الإلكترونيات. يستخدم الأوسولوسكوب لبيان شكل الموجة الكهربية وكيفية تغيرها مع الزمن حيث يعرض العلاقة بين الجهد (أو التيار) مع الزمن. يمكن بذلك تحديد تردد

الموجة ومقدار جهدتها وزمن الارتفاع وزمن الانخفاض، كما يمكن ملاحظة أي تشويه في شكل الموجة. يمكن كذلك

عرض موجتان في نفس الوقت وملاحظة العلاقة بينهما. فمثلاً يمكن عرض دخل الدائرة وخرجها في نفس الوقت وملاحظة الفرق بينهما لمعرفة إذا كان هناك إزاحة في زاوية الطور بينهما أو إذا كان كل منهما معكوس الآخر، وعلاقة التردد بين كل منهما. شكل (٢٧-١) يبين صورة لأوسلوسكوب بقناتين. هناك بعض الأوسلوسكوبات الغالية الثمن التي تحتوي على ثلاثة قنوات أو أربع قنوات وليس أكثر من ذلك.

شكل (٢٧-١) الأوسولوسكوب

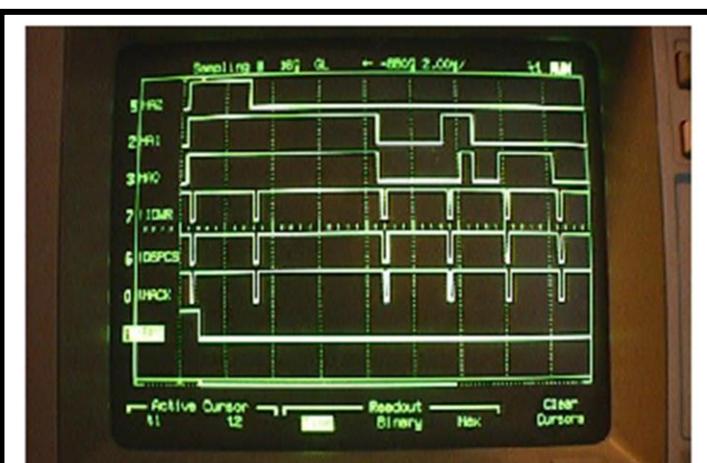

## ال محلل المنطقي Logic analyzer

شكل (٢٨-١) المحلل المنطقي Logic analyzer

يستخدم المحلل المنطقي في دوائر المعالجات أو الحاسوبات بكثرة نظراً لوجود الكثير من الإشارات التي يلزم رؤيتها كلها في نفس الوقت لتحليلها ومعرفة العلاقات بينها مثل الإشارات على خطوط مسار البيانات أو مسار العنوانين أو خطوط التحكم. يمكن استخدام المحلل المنطقي في أكثر من طريقة لعرض الإشارات كما يلى:

١- يستخدم المحلل المنطقي كأوسلوسكوب حيث يمكن

- عرض الإشارة مع الزمن ويمكن عرض أكثر من إشارة في هذه الطريقة قد يصل إلى ٤ إشارات في نفس الوقت.

- يستخدم المحلل المنطقي لبيان المخطط الزمني لعدد من الإشارات يصل إلى ١٦ و ٣٢ إشارة في نفس الوقت. المخطط الزمني في هذه الحالة يبين العلاقة الزمنية لكل إشارة وهل هي واحد أم صفر عند أي لحظة زمنية. عرض الإشارات مختلف عن الحالة السابقة حيث لا يبين تفاصيل مقدار الإشارة إلا أنها صفر أم واحد. هذه الحالة مهمة جداً في بيان إشارات البيانات أو العنوانين في المعالجات أو الحاسوبات.

٣- يمكن للمحلل المنطقي أن يعرض أكثر من إشارة بطريقة الأوسولوسكوب كما في الطريقة الأولى وفي نفس الوقت يعرض باقى الإشارات في نظام المخطط الزمني كما في الحالة الثانية.

٤- يمكن للمحلل المنطقي أن يعرض الإشارات بنظام جدول الحقيقة حيث يعرض الإشارات عبارة عن وحайд وأصفار مكتوبة وليس في مخطط زمني كما في الحالة الثانية. شكل (١ - ٢٨) يبين رسمًا توضيحيًا للمحلل المنطقي.

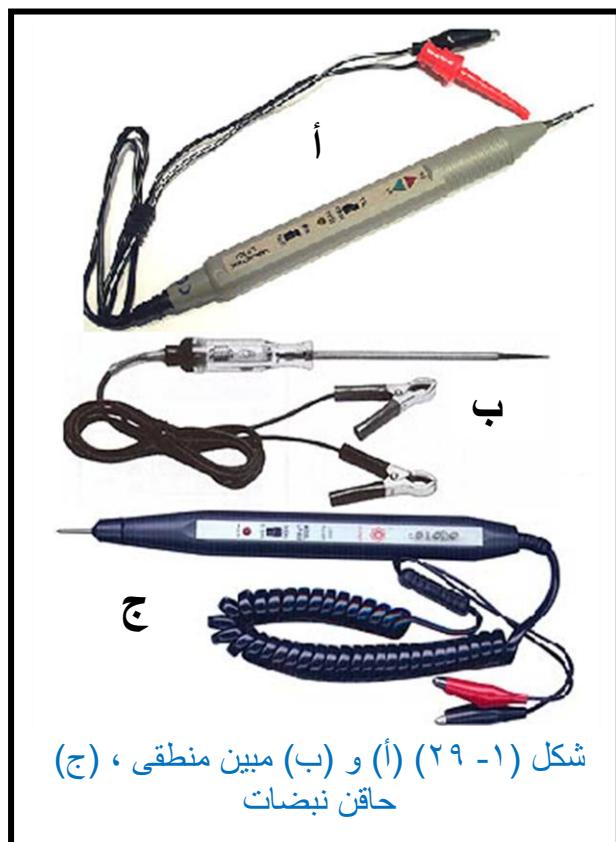

### المبين المنطقي Logic probe

هذا المبين عبارة عن أداة سهلة وبسيطة تمسك في اليد وهي في حجم القلم العادي تستخدمن لاختبار نقطة معينة في الدائرة لمعرفة هل الجهد عند هذه النقطة واحد أم صفر أم عبارة عن نبضات حيث يتم بيان كل حالة على ملبة بيان معينة مع صوت رنيني معين لكل حالة. شكل (١ - ٢٩أ و ب) يبين شكلين مختلفين لهذا المبين. هذا المبين رخيص الثمن ويمكن أن يكون في متناول أي واحد من الهواة.

### حاقد النبضات Pulse injector

حاقد النبضات يشبه المبين المنطقي تماماً سوى أنه يمكن به حقن نبضات عند نقطة معينة في الدائرة كدخل لهذه الدائرة حيث يمكن ملاحظة استجابة الدائرة لهذه النبضات عند أي خرج من مخرج الدائرة. شكل (١ - ٢٩ج) يبين هذا الحاقد.

### جهاز القياس متعدد الأغراض

#### Multimeter

هذا الجهاز من الأجهزة كثيرة الاستخدام في اختبار الدوائر الإلكترونية سواء الرقمية أو غير الرقمية. يمكن بهذا الجهاز قياس المقاومة بالأوم وقياس التيار وفرق الجهد سواء كان متعدد أو مستمر. يتميز هذا الجهاز بصغر حجمه ورخص ثمنه بحيث يمكن أن يكون في متناول أي هاوي. شكل (١ -

٣) يبين صورة لهذا الجهاز. هذا الجهاز منه الأنواع الرقمية كما في الشكل أو الأنواع الانسياحية ذات المؤشر.

### مولد ذبذبات Function generator

لابد أن يحتوى أى معمل للإلكترونيات على أجهزة توليد الذبذبات بالأشكال المختلفة سواء الموجات الجيبية أو المربعة أو المثلثة أو الموجات TTL القياسية، مع إمكانية تغيير كل من تردد ومقدار أى واحدة من هذه الموجات. شكل (١ - ٣١) يبين مولد الذبذبات.

### مصدر قدرة Power supply

شكل (١ - ٣١) مولد ذبذبات Function generator

لابد أن يحتوى أى معمل للإلكترونيات على مصادر قدرة تستخدم لتشغيل أى دائرة أو نظام إلكترونى تنوى اختباره أو تشغيله. في العادة تعطى مصادر القدرة جهدا متغيرا يمكن التحكم فيه أو جهدا ثابتا ٥ فولت يستخدم لتغذية الدوائر الرقمية بالذات. شكل (١ - ٣٢) يبين أحد مصادر القدرة. تباع الآن في محلات الإلكترونيات دوائر مصادر قدرة بسيطة وصغريرة الحجم ورخيصة الثمن كافية جدا للاستخدام مع المشاريع الشخصية التي ينفذها أى واحد من الهواة.

شكل (١ - ٣٢) مصدر قدرة Power supply

### ٧-١ تمارين

- حاول قراءة العديد من المقاومات ذات الألوان المتاحة في المعمل أو على أى لوحة إلكترونية يمكنك العثور عليها.

- بعد قراءة كل مقاومة في التمارين السابقات عن طريق ألوانها حاول قياسها باستخدام الجهاز متعدد الأغراض، وقارن بين النتيجتين. هل هناك خطأ؟ وهل هذا الخطأ يقع في المدى المحدد لدقة المقاومة؟

- حاول توصيل أكثر من مقاومة على التوالي، ثم على التوازي وقس قيمة المقاومة الناتجة في كل حالة.

- أعد التمارين ١ و ٢ و ٣ ولكن هذه المرة على المكثفات.

- ٦- على أى لوحة من اللوحات الإلكترونية حاول التعرف على أنواع الشرائح الإلكترونية المشبوبة عليها.

- ٧- حاول التعرف على كل أجهزة القياس الموجودة في المعمل أو الورشة التي تتدرب فيها.

- ٨- وصل مولد الذبذبات على الأوسولوسكوب ولاحظ الأشكال المختلفة للموجات التي ينتجها المولد.

- ٩- حاول قياس تردد ومقدار كل إشارة وقارن القراءة التي تحصل عليها من على الأوسولوسكوب مع القراءة الموجودة على زر المولد.

# الفصل الثاني

٢

## أنظمة العد

Numbering Systems

## ١-٢ مقدمة

**نحن** نعيش في عالم من الأرقام العشرية التي تتكون من العشرة أرقام الشهيرة صفر حتى تسعه. فلماذا ارتبطنا بهذا النظام؟ ولماذا توقفت صورة الأرقام عند تسعه؟ هل هذا له علاقة بأن أصابع اليد عشرة؟ لا أحد يدرى ... ربما ! السؤال الآن هو: هل من الممكن أن نستخدم نظام آخر للعد غير النظام العشري decimal system؟ تخيل أننا افترضنا وجود نظام ثنائي مثلا لا يحتوى إلا الرقم صفر والرقم واحد، أى أن أصابع اليد كانت اثنين بدلا من عشرة! . كيف سيكون العد في ظل هذا النظام، وكيف سنجمع أو نطرح في هذه الحالة؟ ولماذا النظام الثنائى binary system فقط؟ ماذا لو فرضنا نظام عد آخر يتكون من ثمانيه أرقام، الصفر حتى سبعة (النظام الثمانى octal system)! أو النظام المستعشرى hexadecimal system الذى يتكون من ستة عشرة رقما، صفر حتى ١٥ ، أو حتى أى نظام عد آخر. سنرى بالتفصيل في هذا الفصل كيفية استخدام أى نظام عد مختلف عن النظام العشري. المفاجأة كما سنرى هي أن بعض هذه الأنظمة تكون مفيدة جدا في بعض المواقف، فالنظام الثنائى مثلا هو النظام المستخدم بكثرة في أنظمة الحاسوبات، وشاع استخدام النظام الثمانى والنظام المستعشرى كذلك، ومعظم تعاملنا في هذا الكتاب سيكون مع الأرقام الثنائية كما سنرى.

## ٢-٢ النظام العشري Decimal system

لابد من المرور على نظام العد العشري وحقائق استخدامه حتى نستخدم هذه الحقائق ونعملها للحصول على أنظمة العد الأخرى. إننا في النظام العشري نستخدم عشرة أرقام من صفر حتى تسعه للتعبير عن الكميات من صفر حتى تسعه. عندما نعبر عن كميات أكبر من التسعة نستخدم عددا مركبا من نفس الأرقام من صفر حتى تسعه ولكن في هذه الحالة فإن موضع الرقم داخل العدد يكون له وزنا معينا. فمثلا العدد أو الكمية ٥١ تتكون من رقمين الواحد والخمسة ولكن الخمسة هنا موجودة في موقع أو في خانة العشرات التي يوزن كل واحد فيها بعشرة، لذلك فإن الخمسة في هذه الخانة تمثل خمسين. بينما الواحد يوجد في خانة الآحاد التي يمثل كل واحد فيها بنفس قيمته أى بواحد. لذلك فإن الرقم ٥١ يمكن أن نكتب على هذه الصورة:

$$51 = 5 \times 10 + 1 \times 1$$

وهكذا تم استحداث خانات جديدة مثل خانات المآت التي يمثل كل واحد فيها بمائة وخانة الآلاف التي يمثل كل واحد فيها بألف، وهكذا نرى أن هذه الخانات عبارة عن قوى أو أساس الرقم عشرة التي نقول عنها أنها قاعدة هذا النظام. الكمية ٤٩٩ مثلا يمكن كتابتها كما يلى:

$$499 = 4 \times 10^2 + 9 \times 10^1 + 9 \times 10^0$$

وكذلك الكمية 87535 يمكن كتابتها على الصورة:

$$87535 = 8 \times 10^4 + 7 \times 10^3 + 5 \times 10^2 + 3 \times 10^1 + 5 \times 10^0$$

إذا كانت الكمية العشرية تحتوى كسرًا فإن الأرقام الكسرية التي على يمين العلامة العشرية تكتب منسوبة إلى قوى سالبة من الرقم أو القاعدة 10 كما يلى:

$$535.25 = 5 \times 10^2 + 3 \times 10^1 + 5 \times 10^0 + 2 \times 10^{-1} + 5 \times 10^{-2}$$

وهكذا يمكن التعبير عن أي كمية بالأرقام من صفر حتى تسعة عن طريق فرض قيمة معينة لموضع الرقم داخل الكمية أو داخل العدد. قبل أن نترك النظام العشري decimal إلى النظام الثنائى binary نؤكد على أن هذا النظام به عشرة أرقام صفر حتى تسعة، وقاعدة هذا النظام هي العشرة.

### ٣-٢ نظام العد الثنائى Binary system

في النظام الثنائى يوجد رقمان فقط وهما الصفر 0 والواحد 1. معنى ذلك أن أي كمية أكبر من الواحد سنعبر عنها بعدد مركب من الأصفار والوحاید ولكن موضع كل صفر أو واحد سيكون له قيمة معينة هنا. أي أننا سنعتبر كل خانة يوجد فيها أي صفر أو واحد بقيمة معينة أخرى، هذه القيم ستكون قوى الرقم أو القاعدة 2 مثل قوى الرقم 10 في النظام العشري كما سبق. يتضح ذلك من الأمثلة التالية:

$$10 = 1 \times 2^1 + 0 \times 2^0 = 2 \quad (1-2)$$

$$101 = 1 \times 2^2 + 0 \times 2^1 + 1 \times 2^0 = 5 \quad (2-2)$$

$$101011 = 1 \times 2^5 + 0 \times 2^4 + 1 \times 2^3 + 0 \times 2^2 + 1 \times 2^1 + 1 \times 2^0 = 43 \quad (-2)$$

٣)

وهكذا أمكن التعبير عن أي كمية في النظام الثنائى بفرض قيمة للموضع أو الخانة التي يوجد بها الرقم الثنائى مضروبا في أحد قوى الرقم 2. الآن يمكننا العد بالنظام الثنائى باتباع نفس نظام العد العشري حيث كنا نعد من صفر حتى تسعة ثم نبدأ خانة جديدة وهى خانة العشرات ونضع بها واحد ونستمر في العد ١٠، ١١، ١٢، ١٣، ... حتى ٩٩ بعدها نزيد واحد في خانة العشرات ونستمر في العد ٢٠، ٢١، ٢٢، ... وهكذا حتى ٩٩ بعدها نفتح خانة جديدة (المئات) ونستمر في العد ١٠١، ١٠٢، ... وهكذا حتى ٩٩٩ ثم نبدأ خانة جديدة وهكذا. بنفس الطريقة

| الأرقام<br>العشيرية |   | الأرقام الثنائية |   |   |   |   |

|---------------------|---|------------------|---|---|---|---|

| 0                   | 0 | 0                | 0 | 0 | 0 | 0 |

| 1                   | 0 | 0                | 0 | 0 | 1 |   |

| 2                   | 0 | 0                | 1 | 0 | 0 |   |

| 3                   | 0 | 0                | 1 | 1 |   |   |

| 4                   | 0 | 1                | 0 | 0 |   |   |

| 5                   | 0 | 1                | 0 | 1 |   |   |

| 6                   | 0 | 1                | 1 | 0 |   |   |

| 7                   | 0 | 1                | 1 | 1 |   |   |

| 8                   | 1 | 0                | 0 | 0 |   |   |

| 9                   | 1 | 0                | 0 | 1 |   |   |

| 10                  | 1 | 0                | 1 | 0 |   |   |

| 11                  | 1 | 0                | 1 | 1 |   |   |

| 12                  | 1 | 1                | 0 | 0 |   |   |

| 13                  | 1 | 1                | 0 | 1 |   |   |

| 14                  | 1 | 1                | 1 | 0 |   |   |

| 15                  | 1 | 1                | 1 | 1 |   |   |

جدول ١-٢

سنعد في النظام الثنائي ٠، ١ ثم نبدأ خانة جديدة ١٠، ١١، ثم نبدأ خانة جديدة ١٠٠، ١٠١، ... حتى ١١١ ثم نبدأ خانة جديدة، وهكذا نستمر في العد. جدول ١-٢ يبين الأعداد من صفر حتى ١٥ والقيمة العشرية المقابلة لكل عدد. لاحظ في هذا الجدول أننا لكي نعد من صفر حتى ١٥ يلزمـنا أربع خانات ثنائية. الآن يمكن كتابة القاعدة التالية:

**أكبر قيمة عشرية يمكن أن نصل إليها لعدد معين من الخانات الثنائية تساوى  $(2^n - 1)$**  حيث  $n$  هي عدد الخانات الثنائية. فإذا كانت  $n=4$  فأكبر عدد يمكن أن نصل إليه هو ١٥ وإذا كانت  $n=5$  فأكبر قيمة هي ٣١ وإذا كانت  $n=6$  فأكبر قيمة هي ٦٣ وهكذا.

### ١-٣-٢ طريقة التحويل من النظام الثنائي إلى النظام العشري

طريقة التحويل من النظام الثنائي إلى العشري سهلة و مباشرة ولقد رأيناها في المعادلات (١-٢) و (٢-٢) و (٢-٣) ونسوق مثال آخر نوضح به هذه الطريقة:

$$11011_2 = 1 \times 2^4 + 1 \times 2^3 + 0 \times 2^2 + 1 \times 2^1 + 1 \times 2^0 = 27_{10}$$

الرقم الجانبي بعد أي عدد يدل على نوع هذا العدد، فالرقم ٢ الجانبي يعني أن هذا العدد ممثل في النظام الثنائي والرقم ١٠ يعني أن هذا العدد ممثل في النظام العشري. الخانة في النظام الثنائي التي تأخذ صفر أو واحد تسمى بت. أول خانة من اليمين تسمى الخانة ذات القيمة الصغرى Least Significant Bit, LSB وأخر خانة ناحية اليسار تسمى الخانة ذات القيمة العظمى Most significant bit, MSB.

في حالة احتواء الرقم على كسر مثل 11011.1101 فإن المكافئ العشري في هذه الحالة يمكن حسابه كالتالي:

$$\begin{aligned} 11011.1101 &= 1 \times 2^4 + 1 \times 2^3 + 0 \times 2^2 + 1 \times 2^1 + 1 \times 2^0 + 1 \times 2^{-1} + 1 \times 2^{-2} + 0 \times 2^{-3} + 1 \times 2^{-4} \\ &= 16 + 8 + 2 + 1 + 0.5 + 0.25 + 0.0625 \\ &= 27.7135 \end{aligned}$$

حيث النقطة في الرقم الثنائي ستنطلق عليها العلامة الثنائية بدلاً من العلامة العشرية في حالة النظام العشري.

### ٢-٣-٢ التحويل من النظام العشري إلى النظام الثنائي

الطريقة الأولى للتحويل من نظام عشري إلى نظام ثنائي هي عن طريق تحويل الرقم العشري إلى مجموعة من أوزان الرقم ٢ ابتداء من  $2^0$  ثم  $2^1$  ثم  $2^2$  وهكذا. إن وجد رقم مقابل لواحد من هذه الأوزان توضع الخانة المقابلة بواحد وإن لم يوجد توضع الخانة المقابلة بصفر فالرقم ٩ مثلاً عبارة عن  $8+1$  حيث الشمانية هي  $2^3$  والواحد هو  $2^0$  وعلى ذلك فالرقم ٩ يمكن وضعه على الصورة:

$$2^3 \ 2^2 \ 2^1 \ 2^0$$

$$1 \ 0 \ 0 \ 1$$

وهذه هي بعض الأمثلة الإضافية لذلك:

$$12 = 8 + 4 = 2^3 + 2^2 = 1100$$

$$25 = 16 + 8 + 1 = 2^4 + 2^3 + 2^0 = 11001$$

$$58 = 32 + 16 + 8 + 2 = 2^5 + 2^4 + 2^3 + 2^1 = 111010$$

$$82 = 64 + 16 + 2 = 2^6 + 2^4 + 2^1 = 1010010$$

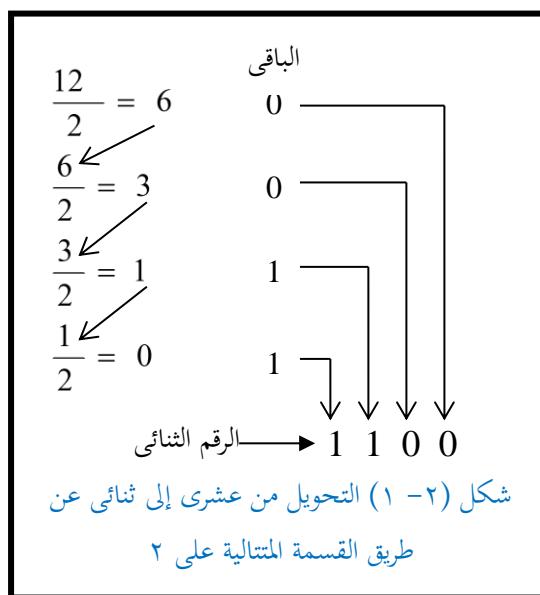

هذه الطريقة في العادة تستخدم مع الأرقام الصغيرة، أما مع الأرقام الكبيرة فطريقة القسمة المتتالية على ٢ هي الأنسب للتحويل من النظام العشري إلى النظام الثنائي. في هذه الطريقة نقسم الرقم العشري على ٢ على مرات متتابعة. في كل مرة سيبقى إما واحد أو صفر هذا الباقي يمثل بذات الرقم الثنائي من اليمين إلى اليسار، أما ناتج القسمة فنأخذه ونقسمه على ٢ مرة أخرى إلى أن يؤول ناتج القسمة إلى صفر. شكل (٢ - ١) يوضح هذه العملية. نلاحظ من هذا الشكل أنه تم قسمة الرقم ١٢ على ٢ فكانت

النتيجة تساوى ستة والباقي صفر يمثل أول بت في العدد الثنائي من اليمين، بعد ذلك أخذنا الرقم ٦ وقسمناه على ٢ مرة أخرى فكان

الناتج ٣ والباقي صفر الذي يمثل البت الثانية في العدد الثنائي، بعد ذلك قسمنا ٣ على ٢ فكان الناتج واحد والباقي واحد يمثل الخانة الثالثة في العدد الثنائي، وأخيراً أخذنا الرقم ١ وقسمناه على ٢ فكان الناتج صفر والباقي واحد وهذا يمثل الخانة رقم ٤ والأخيرة في العدد الثنائي.

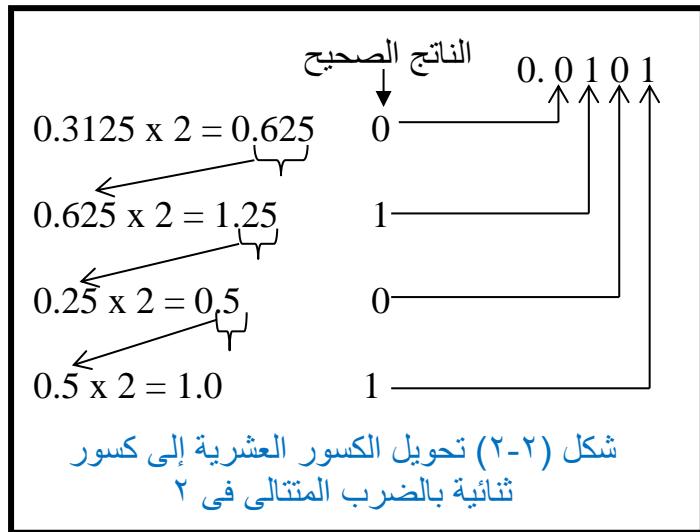

لتحويل الأرقام الكسرية من النظام العشري إلى النظام الثنائي يمكن اتباع طريقة الأوزان للرقم ٢ عن طريق وضع الرقم العشري في صورة مجموعة

لتحويل الأرقام الكسرية من النظام

من الكسور كل منها أحد قوى الرقم ٢ السالبة ولكن هذه الطريقة تكون في العادة أصعب. لذلك نفضل استخدام الطريقة الثانية وهي طريقة الضرب المتتالي في ٢ . في هذه الطريقة نضرب الكسر في ٢ فإذا ظهر واحد صحيح في نتيجة الضرب، نضع هذا الواحد في الرقم الثنائي، وإذا لم يظهر واحد صحيح نضع صفر في الرقم الثنائي، بعد ذلك نأخذ الكسر الناتج ونجرى عليه نفس العملية، وهكذا إلى أن يتلاشى الكسر أو نكتفى بعدد معين من الخانات بعد العلامة الثنائية. شكل (٢-٢) يبين هذه الطريقة بوضوح. في هذا الشكل نريد تحويل الكسر 0.3125 إلى كسر ثنائي لذلك تم ضرب هذا الكسر في ٢ فكان الناتج هو

| الحمل                                              | الناتج |

|----------------------------------------------------|--------|

| $0 + 0 =$                                          | 0      |

| $0 + 1 =$                                          | 1      |

| $1 + 0 =$                                          | 1      |

| $1 + 1 =$                                          | 0      |

| شكل (٢ - ٣) القوانين الأساسية لعملية الجمع الثنائي |        |

$$\begin{array}{r}

\text{الحمل} \\

\begin{array}{r}

1 \quad 1 \\

0 \quad 1 \quad 1 \\

+ \quad 0 \quad 1 \quad 1 \\

\hline

1 \quad 1 \quad 0

\end{array}

\end{array}$$

شكل (٢ - ٤) مثل

العمليات الجمع الثنائي

أى صفر صحيح، لذلك فإن أول خانة في الكسر الثنائي ستكون صفر كما في الشكل. بعد ذلك نأخذ الكسر 0.625 ونضربه في ٢ فيكون الناتج هو 1.25 وهو عبارة عن واحد صحيح يوضع في المخانة الثانية للرقم الثنائي، ونأخذ الكسر 0.25 ونضربه في ٢ مرة أخرى فيكون الناتج هو 0.5 فنضع

صفر في الرقم الثنائي ونضرب الكسر 0.5 في ٢، فيكون الناتج هو 1.0 فنضع واحد في الرقم الثنائي ونوقف عملية الضرب طالما أن الكسر الناتج أصبح صبراً. وعلى ذلك فالكسر الثنائي سيكون 0.0101.

### ٣-٣-٢ العمليات الحسابية في النظام الثنائي

سنرى في هذا الجزء كيفية إجراء العمليات الحسابية الأساسية، الجمع والطرح والضرب والقسمة، في النظام الثنائي لما في ذلك من أهمية في التعامل مع الإشارات الثنائية داخل الحاسوب كما سنرى في الفصول القادمة.

|                                                                                                                                                                          |                                                                                                                                                                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $  \begin{array}{r}  1 \quad 1 \quad 1 \quad 1 \\  1 \quad 0 \quad 1 \quad 0 \\  \hline  \underline{1 \quad 1 \quad 0 \quad 0}  \end{array}  $                           | $  \begin{array}{r}  1 \quad 1 \quad 1 \quad 1 \\  1 \quad 0 \quad 1 \quad 0 \\  \hline  \underline{1 \quad 1 \quad 0 \quad 0}  \end{array}  $                           |

| $  \begin{array}{r}  \text{الحمل} \\  \begin{array}{r}  \uparrow \quad \uparrow \quad \uparrow \quad \uparrow \\  1 \quad 1 \quad 0 \quad 0  \end{array}  \end{array}  $ | $  \begin{array}{r}  \text{الحمل} \\  \begin{array}{r}  \uparrow \quad \uparrow \quad \uparrow \quad \uparrow \\  1 \quad 1 \quad 0 \quad 0  \end{array}  \end{array}  $ |

شكل (٢ - ٥) الحمل وناتج الجمع لثلاث بتات

#### أولاً: الجمع الثنائي

القوانين الأساسية لجمع خانتين ثنائيتين موضحة في شكل (٢ - ٣). نلاحظ من هذا الشكل أن جميع هذه العمليات تعطي صبراً في الحمل ما عدا العملية الأخيرة وهي جمع ١+١ التي تعطى مجموع أو ناتج يساوى صفر وحمل يساوى واحد. بتطبيق هذه القوانين يمكن إجراء عمليات الجمع على أي عددين كما في شكل (٢ - ٤) الذي يبين عملية جمع الرقمين 011 و 011

والتي تعطى الناتج 11 . القاعدة هي أنه كلما تم جمع واحد زائد واحد فإن الناتج يكون صفرًا في نفس العمود ويتم حمل واحد إلى الخانة أو العمود التالي كما في الشكل. في شكل (٢ - ٤) حاصل جمع العمود الأول يعطى ناتج صفر وحمل واحد يجمع مع العمود الثاني. حاصل جمع العمود الثاني  $1+1=2$  يعطى واحد وحمل واحد للخانة الثالثة، وحاصل جمع العمود الثالث  $0+0+1=1$  يعطى واحد وحمل صفر حيث تنتهي العملية. في وجود الحمل من أي عمود للعمود التالي فإنك ستجمع ثلاثة برات وناتج الجمع لثلاث برات موضح في شكل (٢ - ٥).

|           | الاستلاف | الناتج |

|-----------|----------|--------|

| $0 - 0 =$ | 0        | 0      |

| $1 - 1 =$ | 0        | 0      |

| $1 - 0 =$ | 1        | 0      |

| $0 - 1 =$ | 1        | 1      |

**شكل (٢ - ٦) القوانين الأساسية لعملية الطرح الثنائي**

$$\begin{array}{r}

\text{الاستلاف} \leftarrow 10 \\

1 \ 0 \ 1 \\

- 0 \ 1 \ 1 \\

\hline

0 \ 1 \ 0

\end{array}$$

**شكل (٢ - ٧) مثال لعمليات الطرح الثنائي**

**ثانياً: الطرح الثنائي**

القوانين الأساسية للطرح موضحة في شكل (٢ - ٦). نلاحظ من هذا الشكل أن الاستلاف دائمًا صفر ما عدا

الحالة التي يتم فيها طرح واحد من صفر حيث أنه في هذه الحالة

|                | الناتج |

|----------------|--------|

| $0 \times 0 =$ | 0      |

| $0 \times 1 =$ | 0      |

| $1 \times 0 =$ | 0      |

| $1 \times 1 =$ | 1      |

**شكل (٢ - ٨) القوانين الأساسية لعملية الضرب الثنائي**

يكون الناتج واحد والاستلاف borrow واحد أيضًا. لاحظ أنه عند استلاف واحد من عمود إلى العمود الذي على يمينه فإن هذا الواحد يكون باثنين (يكافئ عملية استلاف الواحد بعشرة في النظام العشري). شكل (٢ - ٧) يوضح مثال لطرح الرقم 011 من الرقم 101 حيث كان الناتج هو 010. في العمود الأول من اليمين تم طرح واحد من واحد فكان الناتج صفرًا. في العمود الثاني تم طرح واحد من صفر لذلك لم استلاف واحد باثنين (10) كما في الشكل حيث تم طرح واحد من اثنين فكان الناتج واحد. في العمود الثالث تم طرح صفر من صفر فكان الناتج صفرًا وعلى ذلك كانت النتيجة النهائية هي 010 كما في الشكل.

$$\begin{array}{r}

1011 \\

\times 1001 \\

\hline

1011 \\

0000 \\

0000 \\

\hline

1011 \\

1100011

\end{array}$$

**شكل (٢ - ٩) مثال للضرب الثنائي**

### ثالثاً: الضرب الثنائي

شكل (٢ - ٨) يبين العمليات الأساسية للضرب الثنائي. نلاحظ أن ناتج الضرب دائمًا صفر إلا عندما يكون الطرفين وحيد. عند ضرب أي رقمين تتبع نفس طريقة الضرب في النظام العشري حيث نضرب خانات المضروب في المضروب فيه خانة بعد خانة مع الإزاحة ناحية اليمين بمقدار خانة ثم

نقوم بالجمع كما في شكل (٢ - ٩) الذي يبين عملية ضرب الرقمين 1011 و 1001 حيث كان الناتج هو 1100011.

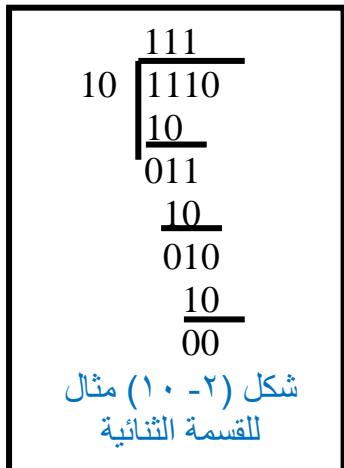

#### رابعاً: القسمة الثنائية

القسمة في النظام الثنائي تتم بنفس طريقة النظام العشري. شكل (١٠ - ٢) يبين مثلاً لذلك حيث تم قسمة الرقم 1110 على الرقم 10 حيث كانت النتيجة تساوى 111.

#### ٤-٢ المتمم الأحادي والمتمم الثنائي Ones and twos complement

المتممات الأحادية والثنائية مفيدة جداً في تمثيل الأرقام السالبة وفي إجراء العمليات الحسابية التي تتم داخل الحاسوب. المتمم الأحادي لأى رقم نحصل عليه ببساطة عن طريق عكس كل واحد إلى صفر، وكل صفر إلى واحد كما في المثال التالي:

$$\begin{array}{r} \text{الرقم الثنائي} & 1101001 \\ \text{المتمم الأحادي} & 0010110 \end{array}$$

المتمم الثنائي لأى رقم ثبائي يمكن الحصول عليه بإضافة واحد للمتمم الأحادي لهذا الرقم كما في المثال التالي:

$$\begin{array}{r} \text{الرقم الثنائي} & 1101001 \\ \text{المتمم الأحادي} & 0010110 \\ \text{إجمع ١ مع المتمم الأحادي} & 1 + \\ \hline \text{المتمم الثنائي} & 0010111 \end{array}$$

هناك طريقة بسيطة وسهلة للحصول على المتمم الثنائي مباشرة في خطوتين كما يلى:

- ١ - ابدأ من ناحية اليمين للرقم المطلوب إيجاد المتمم الثنائي له واتكتب بتاته كما هي حتى أول واحد تقابل له اكتبه كما هو أيضاً.

- ٢ - كل البتات بعد أول واحد، إعكسها فتحصل على المتمم الثنائي.

- كمثال على ذلك الرقم 10111000:

- ١ - من أقصى اليمين هناك ٣ أصفار مع أول واحد نكتبها كما هي كالتالى: 1000.

٢ - ثم كل البتات بعد ذلك يتم عكسها فنحصل على 01001000 وهو المتم الثنائي للرقم المعطى.

كمثال آخر على ذلك نفترض الرقم 011:

١ - نبدأ من ناحية اليمين أول بت واحد نكتبها كما هي.

٣ - ثم نعكس كل البتات بعد ذلك فنحصل على الرقم 101 الذي يمثل المتم الثنائي للرقم المعطى.

## ٥-٢ الأرقام السالبة والموجبة في النظام الثنائي

لا تخلو العمليات الحسابية في الحاسوبات من جمع أو طرح أو ضرب أو قسمة أرقام قد تكون سالبة وقد تكون موجبة. فمثلاً ما هي نتيجة جمع الرقمان (3) + (-9)، وهكذا فإن هناك حاجة ضرورية للتعبير عن الإشارة في الأرقام الثنائية. بالطبع فإن العلامة (+) و (-) غير معرفة في النظام الثنائي فما هو العمل؟ في النظام الثنائي تم التعارف على أن تعتبر آخر بت في الرقم من ناحية اليسار هي بت الإشارة. فإذا كانت هذه البت تساوى صفر فالرقم موجب وإذا كانت هذه البت تساوى واحد فالرقم سالب. بعد ذلك هناك ثلاثة طرق للتعبير عن الرقم كما يلى:

### ١-٥-٢ النظام الأول: نظام مقدار الإشارة **Sign magnitude**

في هذا النظام تعتبر خانة الإشارة هي الخانة التي في أقصى يسار الرقم وباقى البتات تمثل مقدار هذا العدد. فمثلاً الرقم 0101، فيه خانة الإشارة تساوى 0 فالرقم موجب وباقى الرقم هو 101 الذي يمثل القيمة 5، إذن فهذا الرقم عبارة عن 5+. بينما الرقم 1101 فيه خانة الإشارة تساوى واحد والبتات 101 تمثل 5، إذن فالرقم الثنائي 1101 يمثل الرقم (-5) أي أن الفرق الوحيد بين الرقمان 5+، 5- هو الواحد أو الصفر في الخانة الموجودة في أقصى اليسار. أى أنه في نظام مقدار الإشارة للتعبير عن الأرقام السالبة والموجبة ، فإن كل من الرقمان السالب والموجب يكون لهما نفس شكل البتات و يختلفان فقط في بت الإشارة.

### ٢-٥-٢ النظام الثاني: نظام المتم الأحادي

في هذا النظام يمثل الرقم السالب بالمتم الأحادي لنظيره الموجب فمثلاً الرقم 0101 يمثل (5+) لأن آخر بت على اليسار تساوى صفر، وعلى ذلك فالمتم الأحادي للرقم السابق وهو 1010 يمثل الرقم (5-).

**٣-٥-٢ النظام الثالث: نظام المتمم الثنائي**

في هذا النظام يمثل الرقم السالب بالمتمم الثنائي لنظيره الموجب. فمثلاً الرقم 0101 يمثل الرقم (+5) والمتمم الثنائي له هو 1011 يمثل الرقم (-5). نظام المتمم الثنائي هو الأكثر استخداماً في الأنظمة الرقمية كما سُنرى فيما بعد.

**مثال**

ما هي قيمة الرقم 11000 والرقم 01011 في كل نظام من الأنظمة السابقة؟

**في النظام الأول نظام مقدار الإشارة:** الرقم 11000 هو رقم سالب لأن آخر بت تساوى واحد، ومقداره هو  $8 = 2^3$  وعلى ذلك فهذا الرقم هو (-8)، بينما الرقم 01011 فهو رقم موجب لأن آخر بت صفر وقيمتها هي  $+11$  (إحدى عشر).

**في نظام المتمم الأحادي:** الرقم 11000 هو رقم سالب لأن آخر بت تساوى واحد وعلى ذلك فقيمة هذا الرقم هي المتمم الأحادي له وهي 00111، وعلى ذلك فإن الرقم 11000 يمثل الرقم (-7). بينما الرقم 01011 فهو رقم موجب وقيمتها هي  $(+11)$  أو إحدى عشر.

**في نظام المتمم الثنائي:** الرقم 11000 سالب لأن آخر بت تساوى واحد وقيمة الرقم هي المتمم الثنائي له وهي 01000 وبالتالي فالرقم هو (-8). أما الرقم 01011 فهو موجب وقيمتها هي  $(+11)$  أو إحدى عشر).

في نظام المتمم الثنائي الرقم 11000 يمكن كتابته على الصورة :

$$\begin{aligned} 11000 &= -1 * 2^4 + 1 * 2^3 \\ &= -16 + 8 = -8 \end{aligned}$$

والرقم 01011 يمكن كتابته على الصورة :

$$01011 = -0 * 2^4 + 1 * 2^3 + 1 * 2^1 + 1 * 2^0 = 11$$

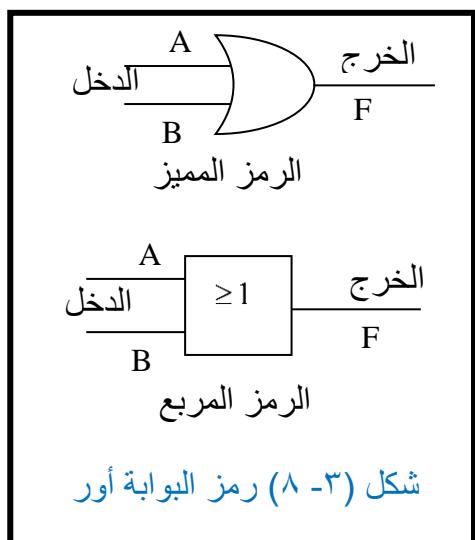

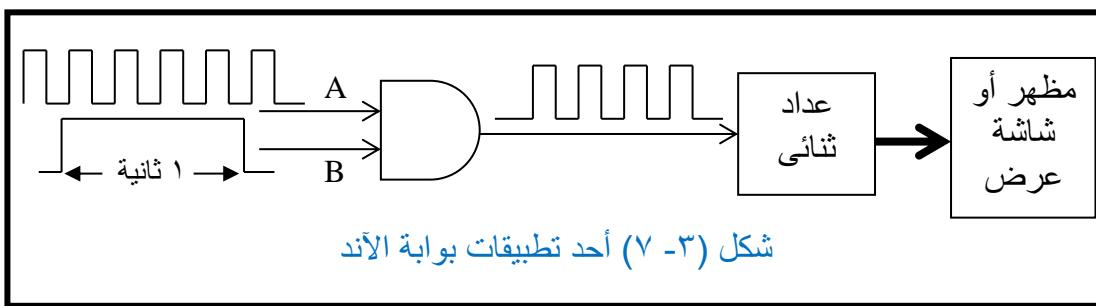

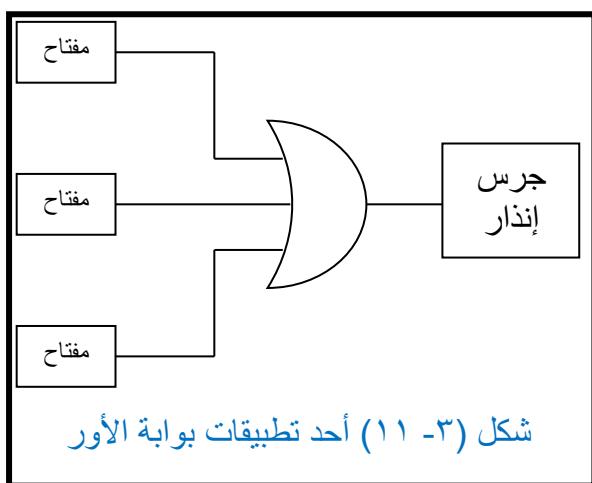

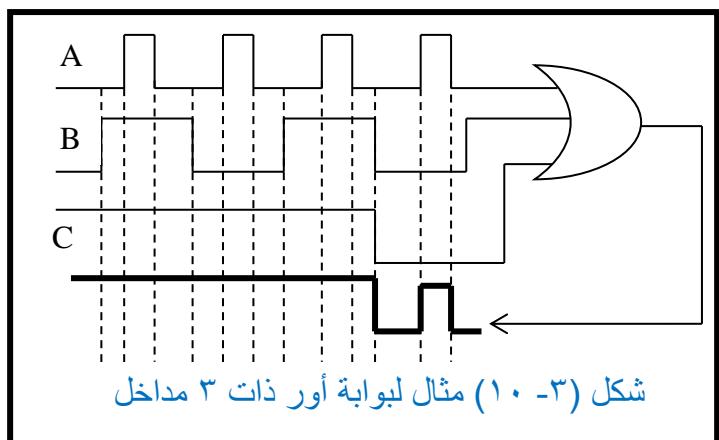

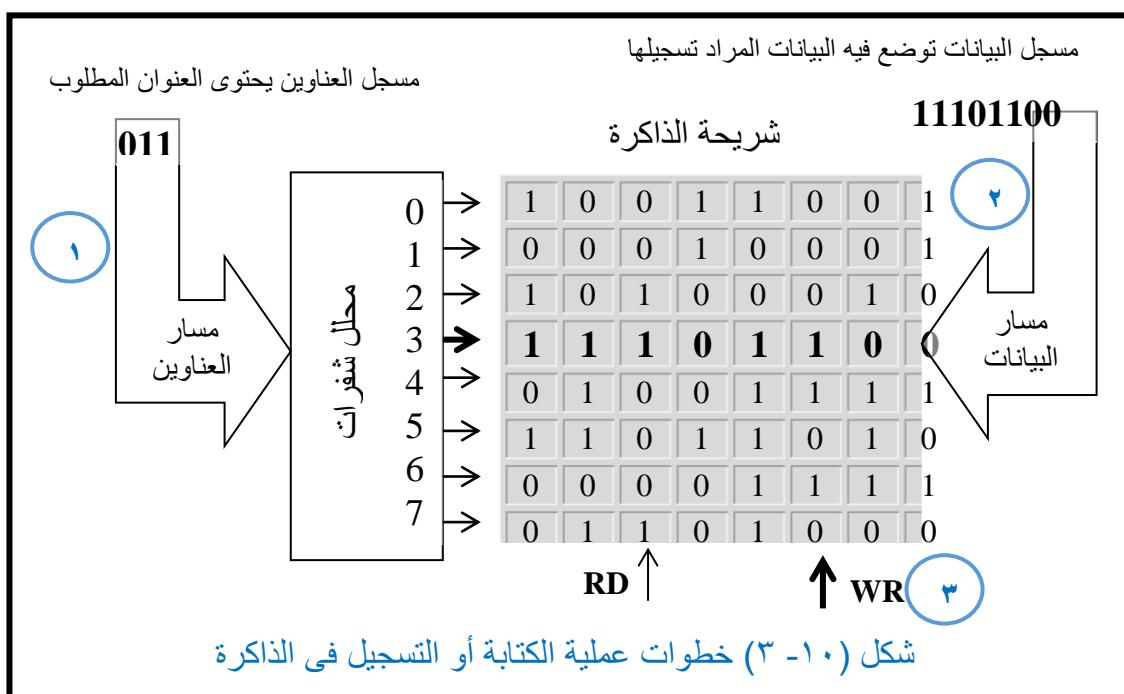

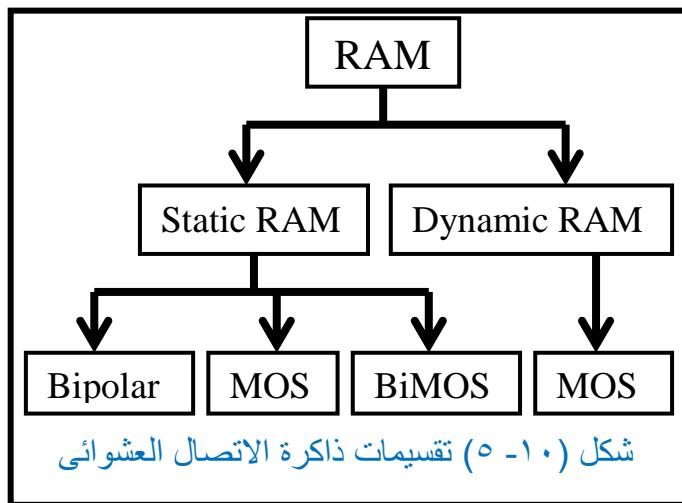

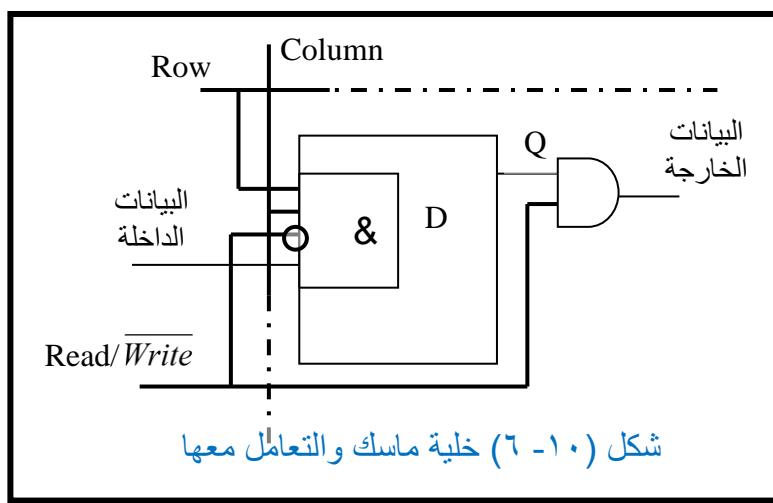

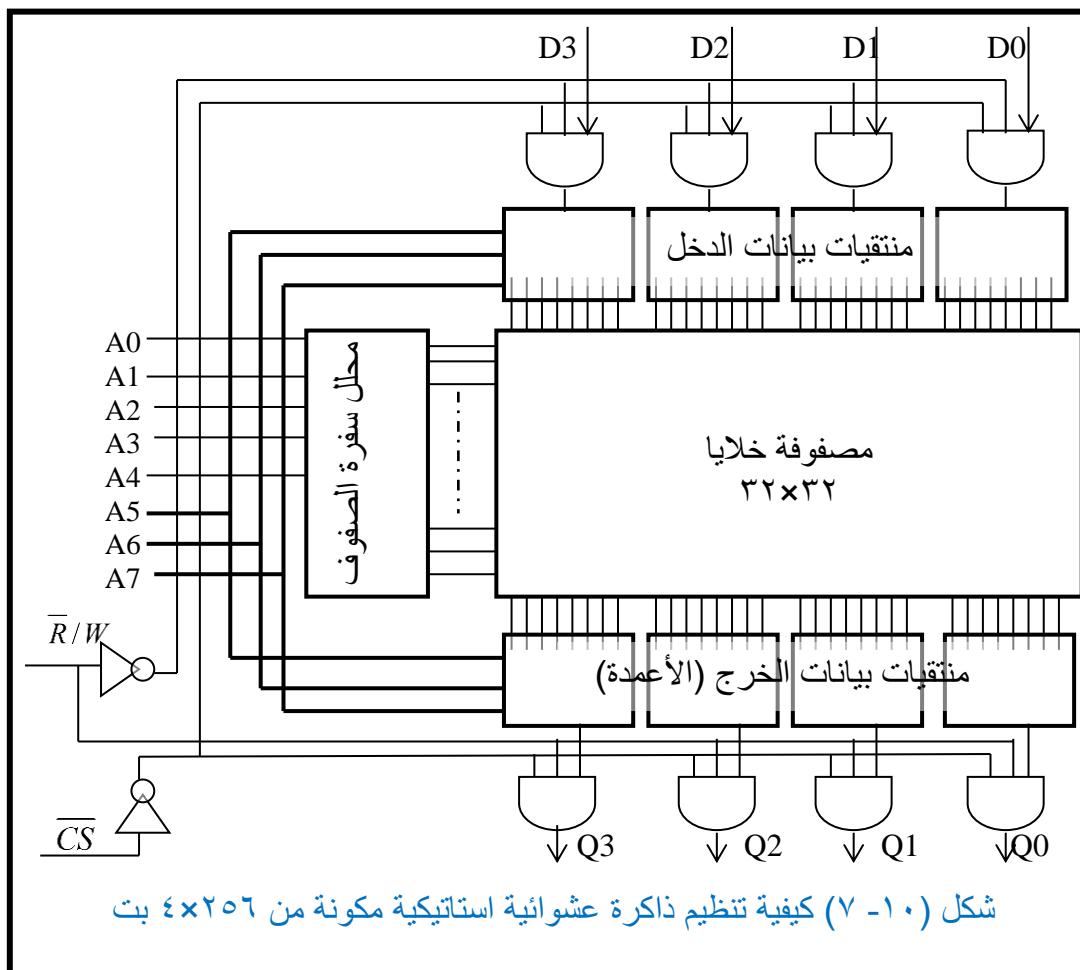

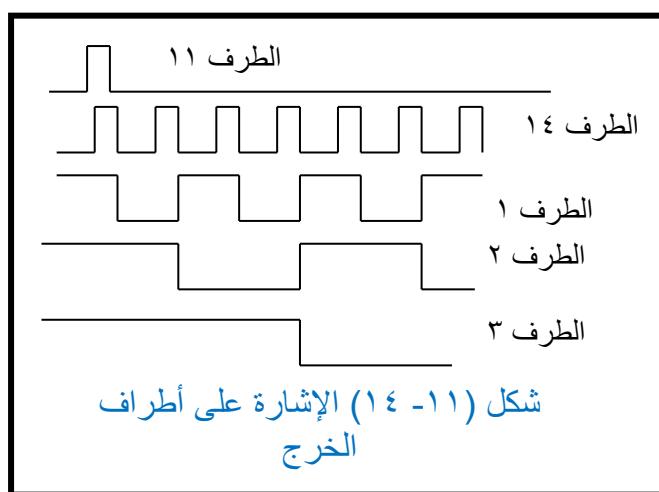

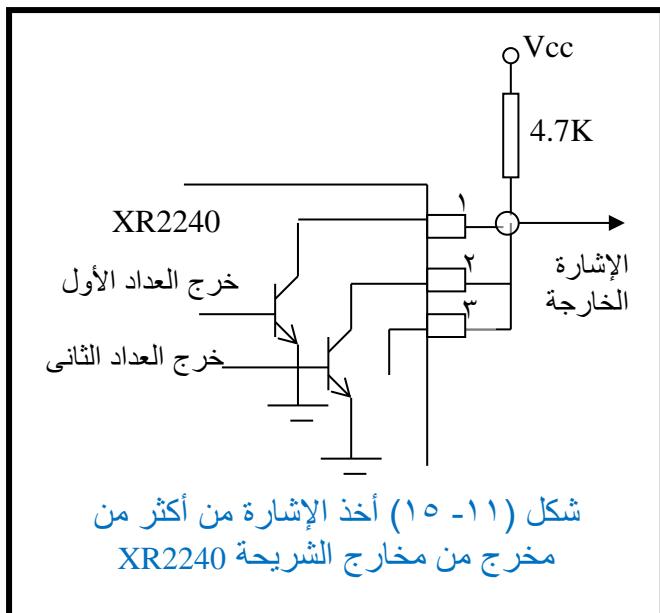

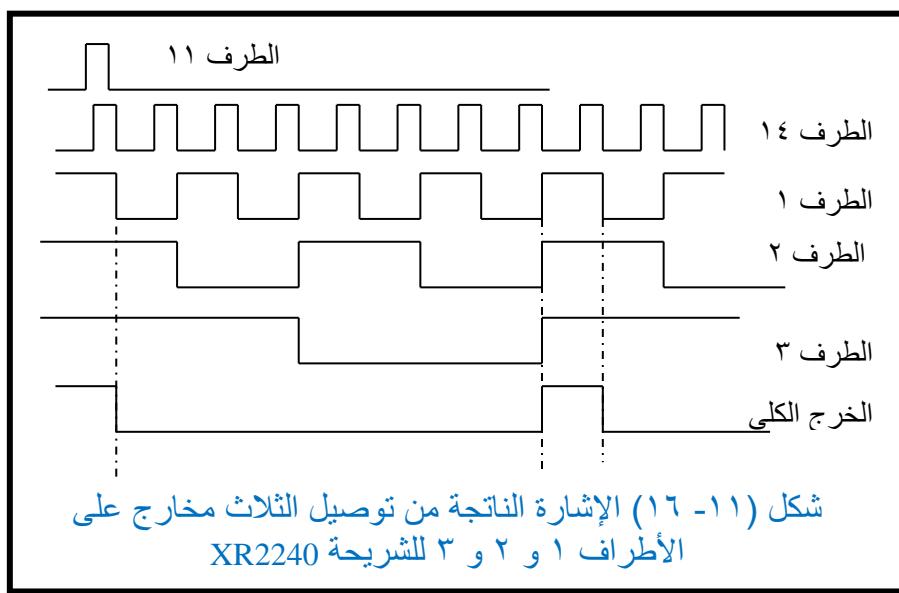

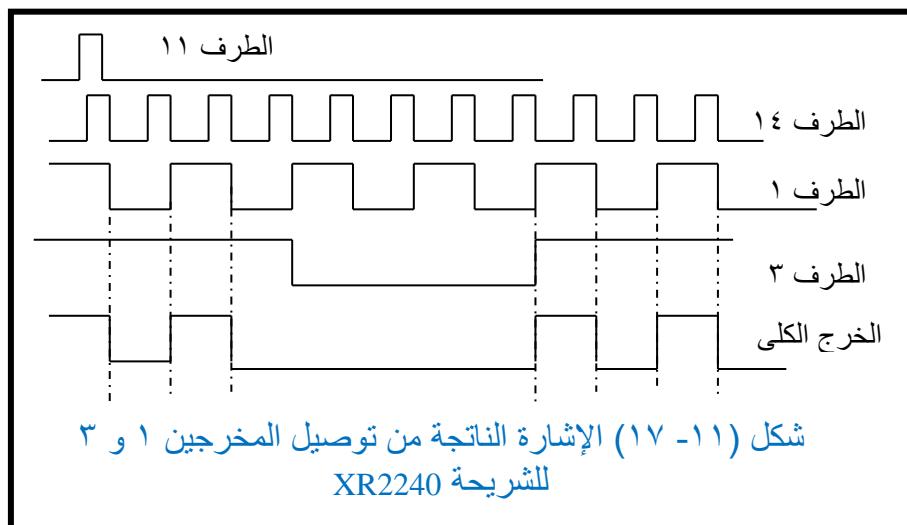

أى أن قيمة الرقم هي التمثيل الحقيقى للوحيد الموجود فيه بما في ذلك بت الإشارة سوى أن قيمة بت الإشارة تكتب سالبة. وهذه ميزة من مميزات استخدام المتمم الثنائي هي أن قيمة الرقم العشرية تحسب مباشرة بطريقة التحويل من ثنائى إلى عشري العادى سوى أن بت الإشارة تكتب سالبة. أيضاً من عيوب طريقة المتمم الأحادي أن الصفر (0000) متممه الأحادي (1111) أى أن هناك فرق بين (+0) و (-0). بينما في المتمم الثنائي فإن (0000) متممه الثنائي هو أيضاً (0000).